(54) ЦИФРОВОЙ СИНТЕЗАТОР ПРЯМОГО ДЕЙСТВИЯ

| название | год | авторы | номер документа |

|---|---|---|---|

| Синтезатор частот | 1980 |

|

SU985947A1 |

| Синтезатор частот | 1980 |

|

SU896762A1 |

| УСТРОЙСТВО ПОИСКА И СЛЕЖЕНИЯ ЗА ШИРОКОПОЛОСНЫМ СИГНАЛОМ | 1983 |

|

SU1840276A1 |

| СИНТЕЗАТОР ЧАСТОТ | 2011 |

|

RU2477920C1 |

| Синтезатор частот | 1985 |

|

SU1256133A1 |

| СИНТЕЗАТОР ЧАСТОТ | 1991 |

|

RU2014733C1 |

| Цифровой синтезатор частот | 1989 |

|

SU1691926A1 |

| Устройство для поиска шумоподобного сигнала | 1984 |

|

SU1277415A1 |

| Цифровой синтезатор частоты | 1984 |

|

SU1252939A1 |

| Цифровой синтезатор прямого действия | 1980 |

|

SU947971A1 |

1

Изобретение относится к импульсной технике и может быть использовано в частотнопреобразующих узлах аппаратуры времени и образцовых частот, измерительных приборов, устройств синхронизации различного назначения, электрических музыкальных инструментов, а также в технике связи.

Известен синтезатор частоты, содержащий опорный генератор, цифровой делитель частоты, блок управления, а также анализатор временного положения импульсов. Требуемый номинал частоты в известном устройстве получается в среднем, однако приняты меры по стабилизации периода выходных импульсов и устранения случайных аппаратурных задержек. Это достигнуто введением анализатора временного положения импульсов, который сравнивает временное положение каждого выходного импульса со входным импульсом входной высокочастотной последовательности синтезатора. По сигналам рассогласования анализатор вырабатывает сигналы на коррекцию коэффициента деления 1.

Этот синтезатор является сложным ввиду наличия быстродействующего блока -

анализатора временного положения импульсов - и, кроме того, выходные импульсы имеют скачкообразную модуляцию фазы, возникающую при коррекциях коэффициен-та деления.

Наиболее близким к предлагаемому является синтезатор частот, содержащий последовательно включенные генератор опорных импульсов, управляемый делитель и блок переменной задержки.

В устройстве приняты меры по уменьщению нестабильности временного положения (фазы) выходных импульсов при помощи блока переменной задержки импульсов, управляющий вход которого связан с анализатором временного положения выходных импульсов. Последний анализирует временное рассогласование выходных имдульсов делителя относительно соответствующих входных импульсов управляемого делителя. В результате формируется сигнал на коррекцию временного положения, выдаваемый в блок переменной задержки импульсов 2.

Недостатком этого устройства является ограниченная стабильность временного положения (фазы) выходных импульсов, низкое быстродействие.

Цель изобретения - повышение быстродействия.

Указанная цель достигается тем, что в цифровой синтезатор прямого действия, содержащий последовательно включенные генератор опорных импульсов, управляемый делитель и блок переменной задержки импульсов, введены дополнительный управляемый делитель и запоминающее устройство, первый выход которого связан с управляющим входом основного управляемого делителя, остальные выходы которого связаны с установочными входами блока переменной задержки, а адресные входы запоминающего устройства связаны с выходами разрядов дополнительного управляемого делителя, счетный вход которого подключен к выходу блока переменной задержки импульсов.

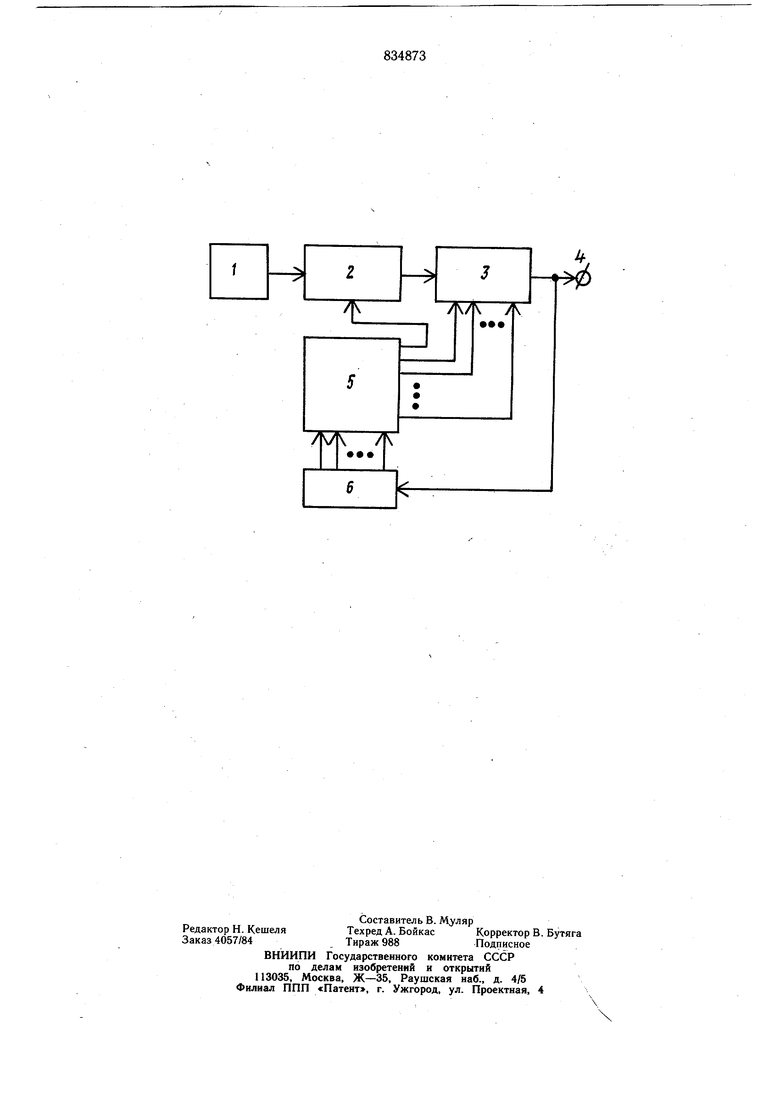

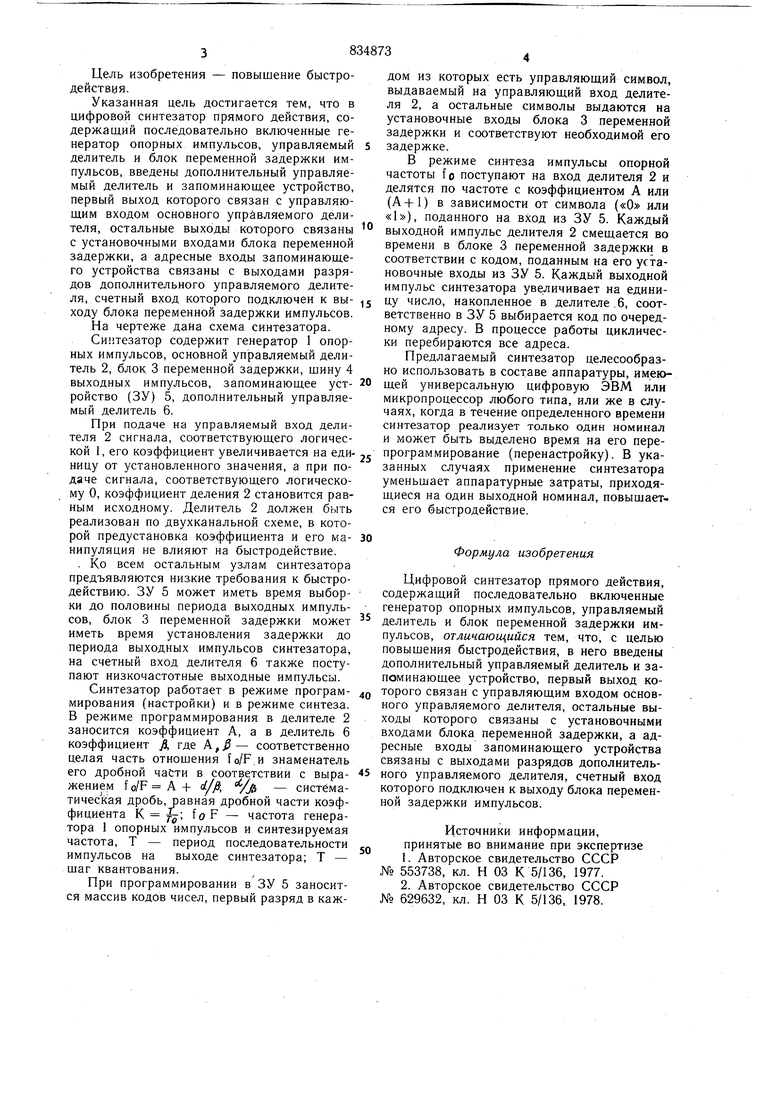

На чертеже дана схема синтезатора.

Синтезатор содержит генератор 1 опорных импульсов, основной управляемый делитель 2, блок 3 переменной задержки, шину 4 выходных импульсов, запоминающее устройство (ЗУ) 5, дополнительный управляемый делитель 6.

При подаче на управляемый вход делителя 2 сигнала, соответствующего логической 1, его коэффициент увеличивается на единицу от установленного значения, а при подаче сигнала, соответствующего логическому О, коэффициент деления 2 становится равным исходному. Делитель 2 должен быть реализован по двухканальной схеме, в которой предустановка коэффициента и его манипуляция не влияют на быстродействие.

. Ко всем остальным узлам синтезатора предъявляются низкие требования к быстродействию. ЗУ 5 может иметь время выборки до половины периода выходных импульсов, блок 3 переменной задержки может иметь время установления задержки до периода выходных импульсов синтезатора, на счетный вход делителя 6 также поступают низкочастотные выходные импульсы.

Синтезатор работает в режиме программирования (настройки) и в режиме синтеза. В режиме программирования в делителе 2 заносится коэффициент А, а в делитель 6 коэффициент Д где А.- соответственно целая часть отношения fo/F и знаменатель его дробной части в соответствии с выражением //g - систематическая дробь, равная дробной части коэффициента К ; fo F - частота генератора 1 опорных импульсов и синтезируемая частота, Т - период последовательности импульсов на выходе синтезатора; Т - щаг квантования.

При программировании в ЗУ 5 заносится массив кодов чисел, первый разряд в каждом из которых есть управляющий символ, выдаваемый на управляющий вход делителя 2, а остальные символы выдаются на установочные входы блока 3 переменной задержки и соответствуют необходимой его задержке.

В режиме синтеза импульсы опорной частоты fo поступают на вход делителя 2 и делятся по частоте с коэффициентом А или (A-J-1) в зависимости от символа («О или «1), поданного на вход из ЗУ 5. Каждый выходной импульс делителя 2 смещается во времени в блоке 3 переменной задержки в соответствии с кодом, поданным на его установочные входы из ЗУ 5. Каждый выходной импульс синтезатора увеличивает на единицу число, накопленное в делителе.6, соответственно в ЗУ 5 выбирается код по очередному адресу. В процессе работы циклически перебираются все адреса.

Предлагаемый синтезатор целесообразно использовать в составе аппаратуры, имеющей универсальную цифровую ЭВМ или микропроцессор любого типа, или же в случаях, когда в течение определенного времени синтезатор реализует только один номинал и может быть выделено время на его перепрограммирование (перенастройку). В указанных случаях применение синтезатора уменьшает аппаратурные затраты, приходящиеся на один выходной номинал, повышается его быстродействие.

Формула изобретения

Цифровой синтезатор прямого действия, содержащий последовательно включенные генератор опорных импульсов, управляемый делитель и блок переменной задержки импульсов, отличающийся тем, что, с целью повышения быстродействия, в него введены дополнительный управляемый делитель и запоминаюшее устройство, первый выход которого связан с управляющим входом основного управляемого делителя, остальные выходы которого связаны с установочными входами блока переменной задержки, а адресные входы запоминающего устройства связаны с выходами разрядов дополнительного управляемого делителя, счетный вход которого подключен к выходу блока переменной задержки импульсов.

Источники информации, принятые во внимание при экспертизе

/М /Г

А

Авторы

Даты

1981-05-30—Публикация

1979-10-30—Подача