(54) ДЕШИФРАТОР ЧИСЛОВОГО КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Дешифратор числового кода | 1983 |

|

SU1181157A1 |

| Устройство для дешифрации числового кода | 1990 |

|

SU1785082A1 |

| Устройство для измерения длительности кодовых импульсов | 1980 |

|

SU868693A1 |

| Дешифратор числового кода | 1977 |

|

SU734874A1 |

| Устройство для измерения длительности кодовых импульсов | 1987 |

|

SU1506434A1 |

| Кодовый трансмиттер | 1983 |

|

SU1179549A1 |

| Устройство для диспетчерского контроля | 1984 |

|

SU1249559A1 |

| ЦИФРОВОЕ N-КАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2018 |

|

RU2685445C1 |

| ЦИФРОВОЕ ПЯТИКАНАЛЬНОЕ РЕЛЕ С ФУНКЦИЕЙ САМОДИАГНОСТИКИ | 2017 |

|

RU2671545C1 |

| Запоминающее устройство с самоконтролем | 1982 |

|

SU1037342A1 |

1

Изобретение относится к автоматике.

Известны дешифраторы числового кода, содержащие приемный блок, счетчики, генератор и запоминающие бло ки 1.

Наиболее близкий к пределагаемому дешифратор числового кода сидержит приемный блок, входы которого соединены с входными шинами, первый и второй выходы - с управляющими входами соответственно первого и второго счётчиков, а третий выход подключен ко входу запуска генератора, первый и второй запоминающие блоки, информационные входы который: соединены соответственно с выходами, первого и второго счетчиков,, согласующий блок, между выходами которого и общей шиной включены электромагнитные реле 2..

Недостатком известных устройств является низкая.помехозащищенность.

Цель изобретения - повышение помехозащищенности дешифратора числового кода.

Указанная цель достигается тем, что в дешифратор числового кода, содержащий приемный блок, входы которого соединены с входными шинами.

первый и второй выходы - с управляющими входами соответственно первого и второго счетчиков, а третий выход подключен ко входу запуска генератора, первый и второй запоминающие блоки, информационные входы которых соединены соответственно с выходами первого и второго счетчиков, согласующий блок, между выходами которого

0 и общей шиной включены электромагнитные реле,введены третьи счетчик и запоминающ::й блок, а также сум матор и блок вьщеления импульсами интервала, первый вход которого сое5динен с четвертым выходом приемного блока, второй вход - с выходом генератора, первый и второй выходы подключены соответственно к счетным входам первого и второго счетчиков, тре0тий выход- Ко входам записи первого и второго запоминающих блоков, а четвертый выход соединен со входом записи третьего запоминающего блока, выход которого подключен ко входу

5 согласующего блока, вход блокировки через третий счетчик - к выходу генератора, а информационный вход соединен с выходом сумматора, входы которого подключены к выходам первого 30 и второго запоминё1ющих блоков.

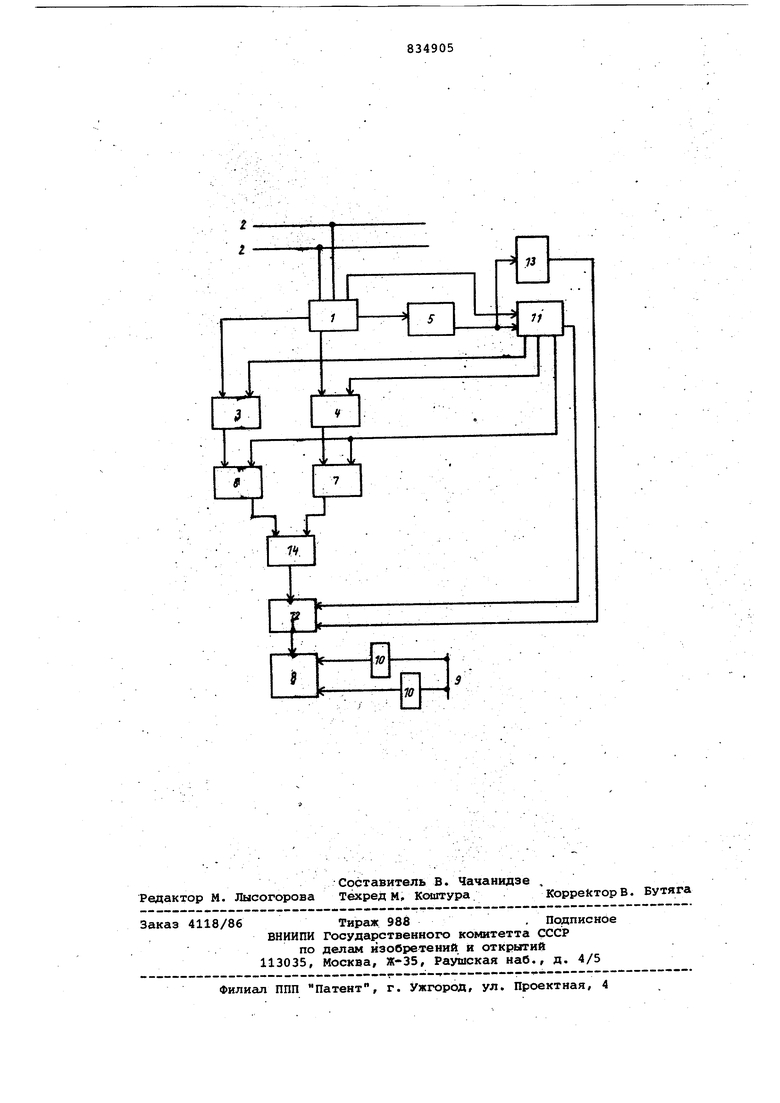

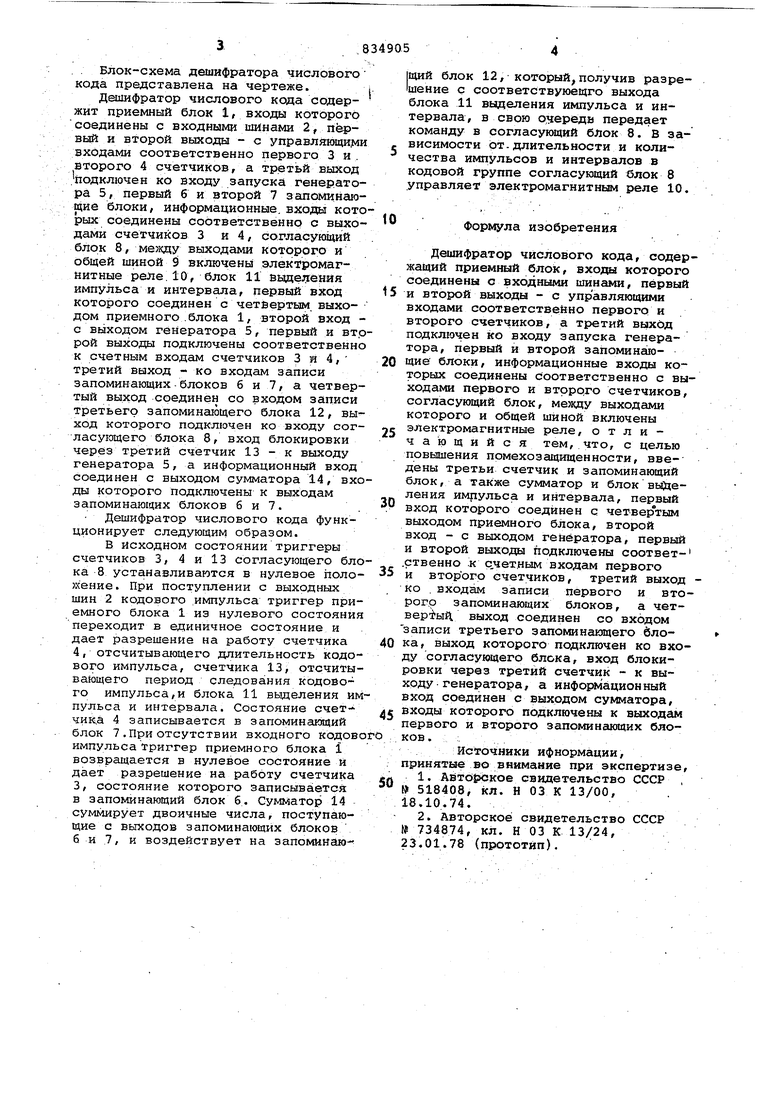

. . Блок-схема дешифратора числового кода представлена на чертеже.

Дешифратор числового кода содержит приемный блок 1, входы которого

соединены с входными шинами 2, первый и второй выходы - с управляющими входами соответственно первого 3 и . второго 4 счетчиков, а третьи выход

.подключен ко входу запуска генератора 5, первый 6 и второй 7 запоминаюрие блоки, информационные, входы которых соединены соответственно с выходами счетчиков 3 и 4, согласующий блок 8, между выходами которого и общей шиной 9 включены электромагйитные реле 10, блок 11 вьще,яения импульса и интервала, первый вход которого соединен с четвертым, выходом приемного .блока 1, второй вход с выходом генератора 5, первый и втррой выходы подключены соответственно к счетным входам счетчиков 3 и 4, третий выход - ко входам записи запоминающихблоков б и 7, а четвертый выход соединен со входом записи третьего запоминающего блока 12, выход которого подключен ко входу согласующего блока 8, вход блокировки через третий счётчик 13 - к выходу генератора 5, а информационный вход соединен с выходом сумматора 14, входы которого подключены к выходам запоминающих блоков 6 и 7. . Дешифратор числового кода функционирует следующим образом.

В исходном состоянии триггеры счетчиков 3, 4 и 13 согласующего блока В устанавливаются в нулевое положение. При поступлении с выходных шин 2 кодового .импульса триггер приемного блока 1 из нулевого состояния переходит в единичное состояние и дает разрешение на работу счетчика 4, отсчитывающего длительность кодового импульса, счетчика 13, отсчитывающего период следования кодового импульса,и блока 11 выделения импульса и интервала. Состояние счет- чикд 4 записывается в запоминающий блок 7 .При отсутствии входного кодов импульса Триггер приемного блока 1 возвращается в нулевое состояние И дает разрешение на работу счетчика 3, состояние которого записывается в запоминающий блок 6. Сумматор 14 суммирует двоичные числа, поступающие с выходов запоминающих блоков 6 и 7, и воздействует на запоминающий блок 12, который,получив разрешение с соответствуюещго выхода блока 11 выделения импульса и интервала, в свою о,чередв передает команду в согласующий блок 8. В зависимости ОТ-длительности и количества импульсов и интервалов в кодовой группе согласующий блок 8 управляет электромагнитньш реле 10.

Формула изобретения

Дешифратор числового кода, содержащий приемный блок, входы которого соединены с входными шинами, первый и второй выходы - с управляющими входами соответственно первого и второго счетчиков, а третий выход подключен ко входу запуска генератора, первый и второй запоминающие блоки, информационные входы которнлх соединены соответственно с выходами первого и второго счетчиков, согласующий блок, между выходами которого и общей шиной включены электромагнитные реле, о т л и чающийся тем, что, с целью повышения помехозащищенности, введены третьи счетчик и запоминающий блок, а также сумматор и блок вьйеления имрульса и интервала, первый вход которого соединен с четвер°тым выходом приемного блока, второй вход - с выходом генератора, первый и второй выходы подключены соответ.ственно .к с.чет.НЕлм входам первого и второго счетчиков, третий выход ко .входам записи первого и второго запоминающих блоков, а четвер ый выход соединен со входом записи третьего запоминающего блока, выход которого подключен ко входу согласующего блока, вход блокировки через третий счетчик - к выходу генератора, а инфО1 4ацион ный вход соединен с выходом сумматора, входы которого подключены к выходам первого и второго запоминающих блоков .

Источники ифнормации, принятые 8О внимание при экспертизе

Авторы

Даты

1981-05-30—Публикация

1979-05-25—Подача