(54) ПРЕОБРАЗОВАТЕЛЬ КОДА

| название | год | авторы | номер документа |

|---|---|---|---|

| Преобразователь перемещения в код | 1988 |

|

SU1566480A1 |

| Преобразователь двоичного кода угла в двоично-десятично-шестидесятиричный код градусов,минут,секунд | 1980 |

|

SU960791A1 |

| Устройство для преобразования кода системы остаточных классов в десятичный код | 1984 |

|

SU1167600A1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Функциональный цифроаналоговый преобразователь двоично-десятичного кода для следящих систем | 1986 |

|

SU1473085A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| ШИФРАТОР | 1989 |

|

RU2033691C1 |

| Устройство индикации измерительного прибора | 1984 |

|

SU1262395A1 |

| Устройство для цифровой индикации | 1979 |

|

SU903961A1 |

Изобретение относится к автоматике и вычислительной технике и предназначено для .преобразования равновесного кода из десятичной системы счисления в восьмеричную с произвольным законом преобразования.

Известен комбинационный преобразователь многоразрядного кода одного типа в код другого типа, содержащий преобразователи единиц и десятков и сумматоры единиц, десятков и сотен

Однако в преобразователях единиц и десятков преобразованию подвергаются все кодовые комбинации преобразуемого кода, что усложняет оборудование и увеличивае т количество элементов.

Известен также преобразователь кода, содержащий, в каждой декаде последовательно соединенные деишфратор и шифратор,причем ьходы дешифратора соединены с входными шинами, а также общий для всех декад дополнительный шифратор, входы которого соединены с выходными шинами старших разрядов .2l.

Однако данное устройство является сложным и содержит большое количество злементов.

Цель изобретения - урощение преобразовательных функций и повышение наджености.

Поставленная цель достигается тем, что в преобразователь кода из десятичной системы счисления в восьмеричную, содержгиций в каждой декаде последовательно соединенные дешифратор и шифратор, причем входы

0 дешифратора соединены с входными шинами, а также общий для всех декад дополнительный шифратор, выходы которого соединены с выходными шинами старших разрядов, в каждую декаду

5 введены элемент ИЛИ и коммутатор на два направления, первые информационные входы которого соединены с выходами шифратора, вторые информационные входы коммутатора объединены по0разрядно с входами дешифратора, прямой и инверсный управляющие входы коммутатора объединены и подключены к выходу элемента ИЛИ данной декады, оба входа которого соединены с вы5ходами дешифратора указанной декады, а также общий для всех декад элемент ИЛИ, причем входы общего элемента ИЛИ соединены с выходами элементов ИЛИ всех декад, а выход общего эле0мента ИЛИ соединен со входом дополнительного шифратора, выходы коммутаторов соединены с выходными шинами младших разрядов.

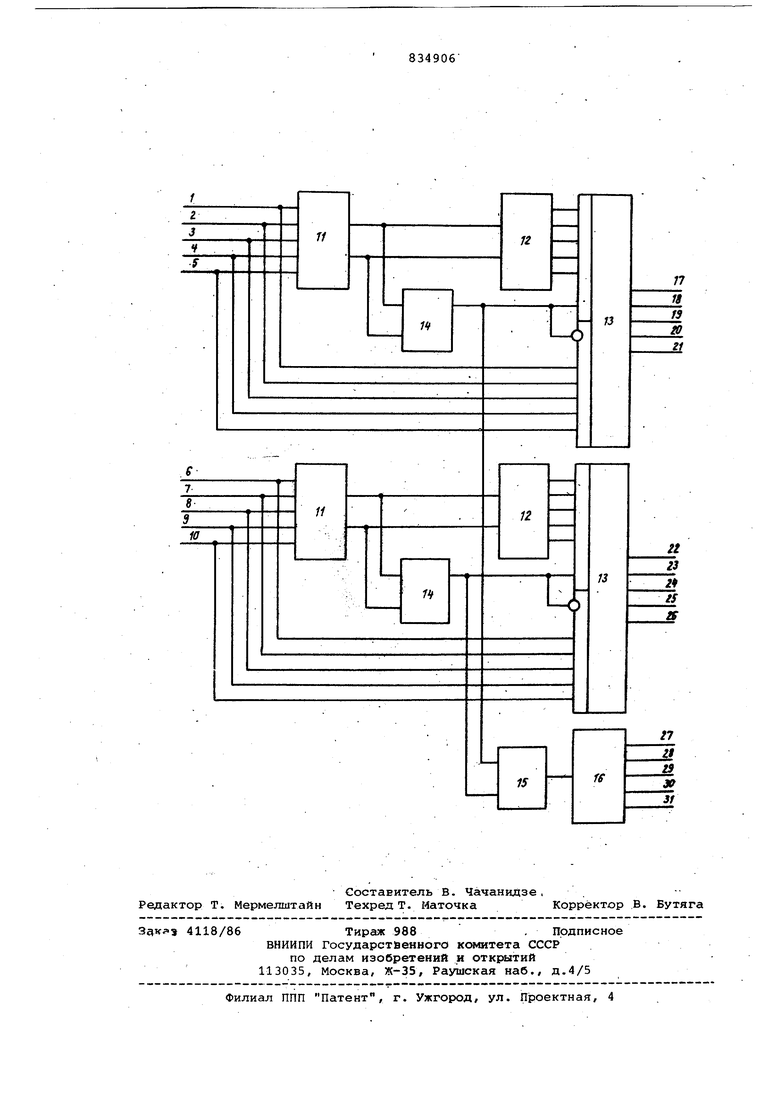

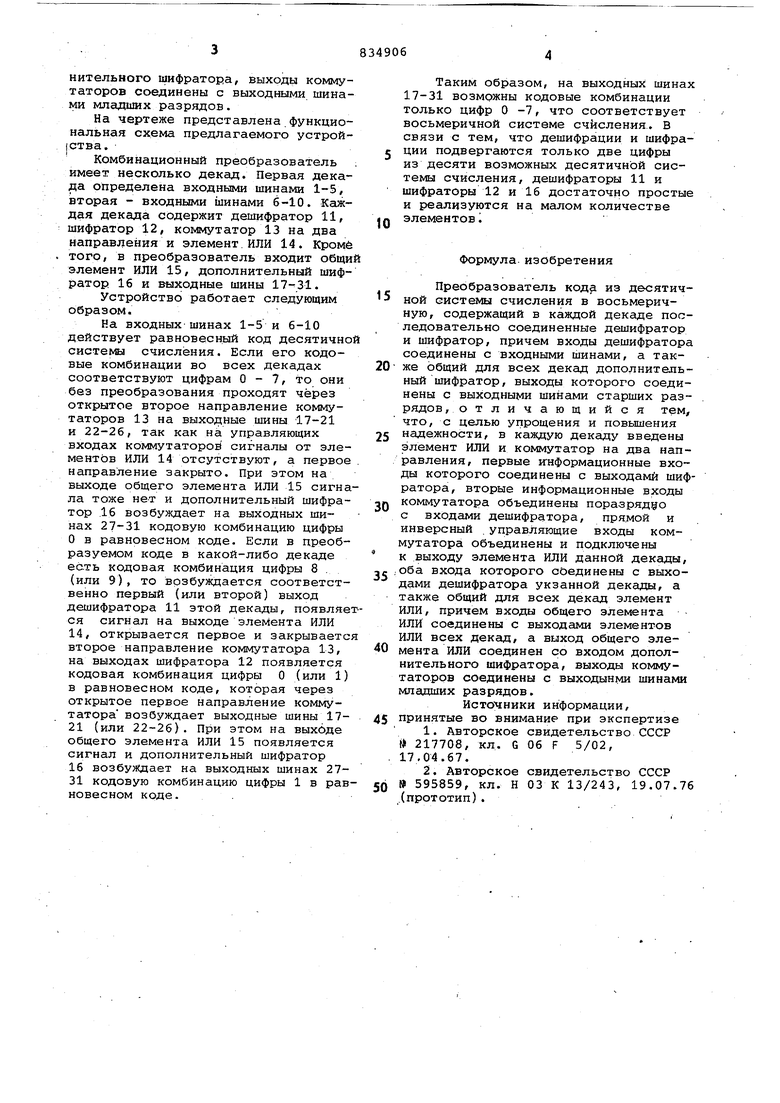

На чертеже представлена.функциональная схема предлагаемого устрой ства.

Комбинационный преобразователь имеет насколько декад. Первая декада определена входными шинами 1-5, вторая - входными шинами 6-10. Каждая декада содержит дешифратор 11, шифратор 12, коммутатор 13 на два направления и элемент. ИЛИ 14. Кроме того в преобразователь входит общи элемент ИЛИ 15, дополнительный шифратор 16 и выходные шины .

Устройство работает следующим образом.

На входных шинах 1-5 и 6-10 действует равновесный код десятично системы счисления. Если его кодовые комбинации во всех декадах соответствуют цифрам О - 7, то они без преобразования проходят через открытое второе направление коммутаторов 13 на выходные шины 17-21 и 22-26, так как на управляющих входах коммутаторов сигналы от элементов ИЛИ 14 отсутствуют, а первое направление закрыто. При этом на выходе общего элемента ИЛИ 15 сигнала тоже не-т и дополнительный шифратор 16 возбуждает на выходных шинах 27-31 кодовую комбинацию цифры О в равновесном коде. Если в преобразуемом коде в какой-либо декаде есть кодовая комбинация цифры 8 . (или 9), то возбуждается соответственно первый (или второй) выход дешифратора 11 этой декады, появляеся сигнал на выходе элемента ИЛИ 14, открывается первое и закрываетс второе направление коммутатора 13, на выходах шифратора 12 появляется кодовая комбинация цифры О (или 1) в равновесном коде, которая через открытое первое направление коммутатора возбуждает выходные шины 1721 (или 22-26), При этом на выходе общего элемента ИЛИ 15 появляется сигнал и дополнительный шифратор 16 возбуждает на выходных шинах 2731 кодовую комбинацию цифры 1 в равновесном коде. .

Таким образом, на выходных шинах 17-31 возможны кодовые комбинации только цифр О -7, что соответствует восьмеричной системе счисления, В связи с тем, что дешифрации и шифрас ции подвергаются только две цифры из десяти возможных десятичной системы счисления, дешифраторы 11 и шифраторы 12 и 16 достаточно простые и реализуются на малом количестве Q элементовi

Формула, изобретения

Преобразователь код из десятичной системы счисления в восьмеричную, содержащий в каждой декаде последовательно соединенные дешифратор и шифратор, причем входы дешифратора соединены с входными шинами, а также общий для всех декад дополнительный шифратор, выходы которого соединены с выходными шинами старших разрядов , отличающийся тем, что, с целью упрощения и повышения

5 надежности, в каждую декаду введены элемент ИЛИ и коммутатор на два направления, первые информационные входы которого соединены с выходами шифратора, вторые информационные входы

Q коммутатора объединены поразрядно с входами дешифратора, прямой и инверсный управляющие входы коммутатора объединены и подключены

к выходу элемента ИЛИ данной декады, .оба входа которого соединены с выходами дешифратора укзанной декады, а также общий для всех декад элемент ИЛИ, причем входы общего элемента ИЛИ соединены с выходами элементов ИЛИ всех декад, а выход общего элемента ИЛИ соединен со входом дополнительного шифратора, выходы коммутато.ров соединены с выходынми шинами младших разрядов.

Источники информации,

5 принятые во внимание при экспертизе

1,Авторское свидетельство СССР № 217708, кл. G 06 F 5/02,

. 17,04,67.

2,Авторское свидетельство СССР

0 595859, кл, Н 03 К 13/243, 19,07,76 Xпрототип),

Авторы

Даты

1981-05-30—Публикация

1979-07-04—Подача