1

Изобретение относится к вычислительной технике и может быть использовано в следящих системах, в частности, в позиционных устройствах числового программного управления.

Цель изобретения - повышение точности преобразования малых значений входного кода.

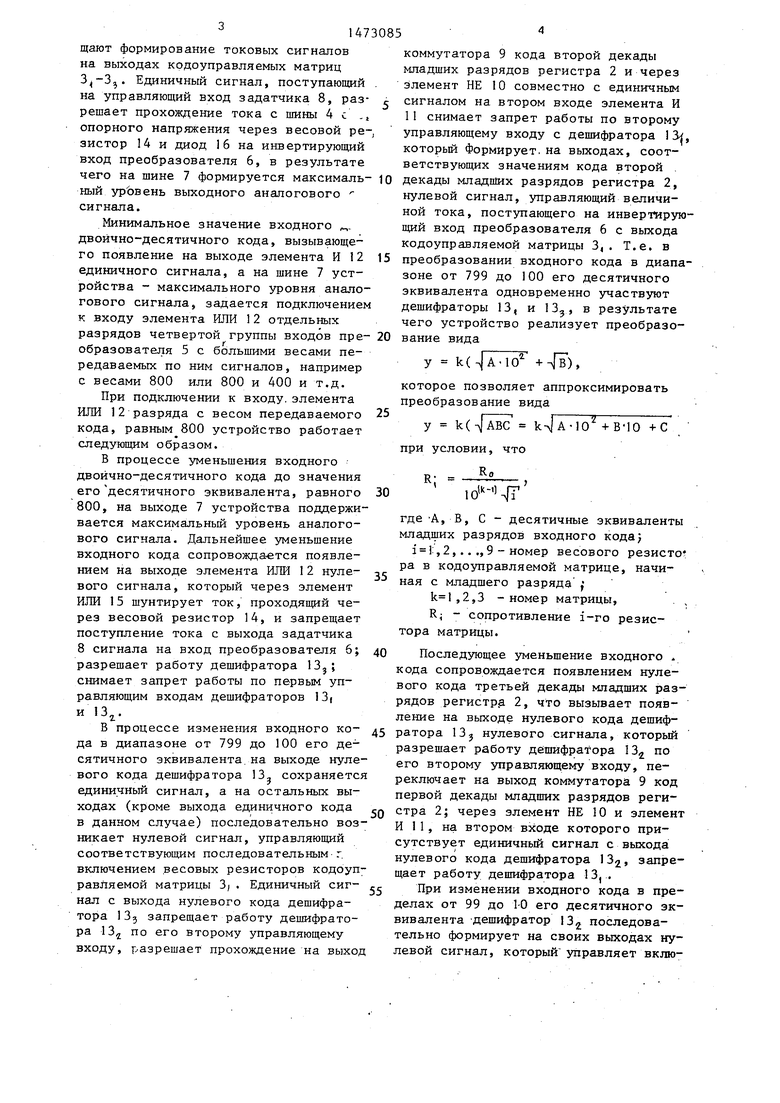

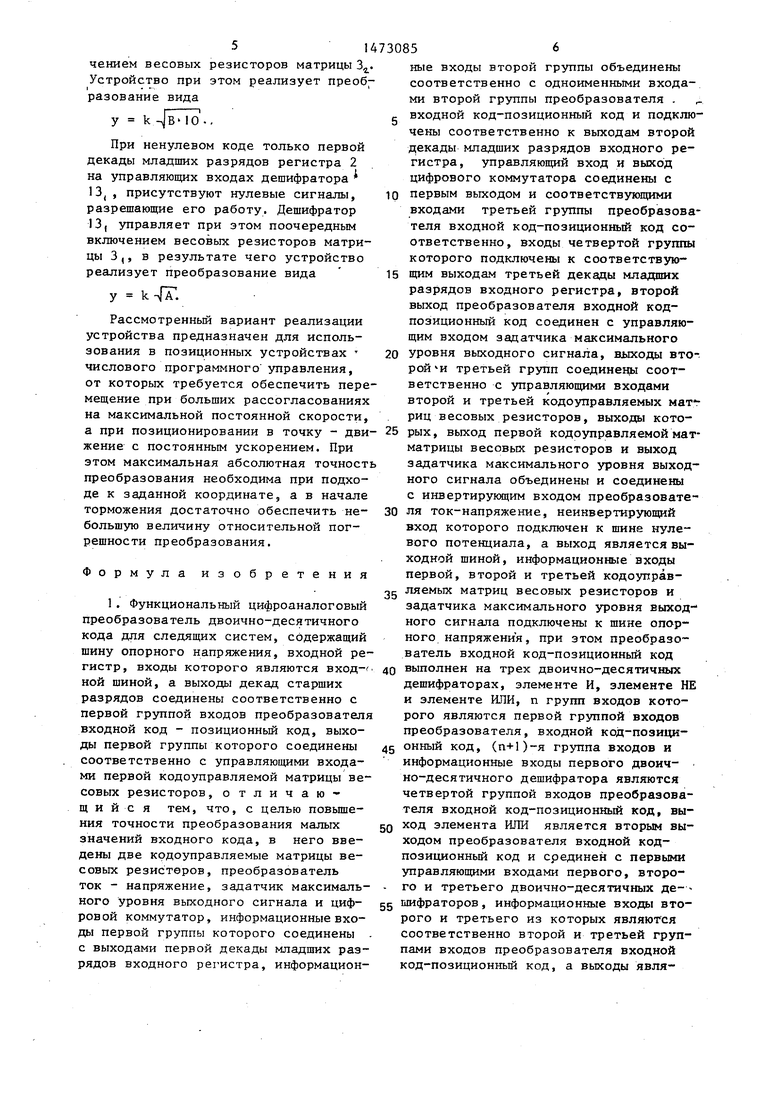

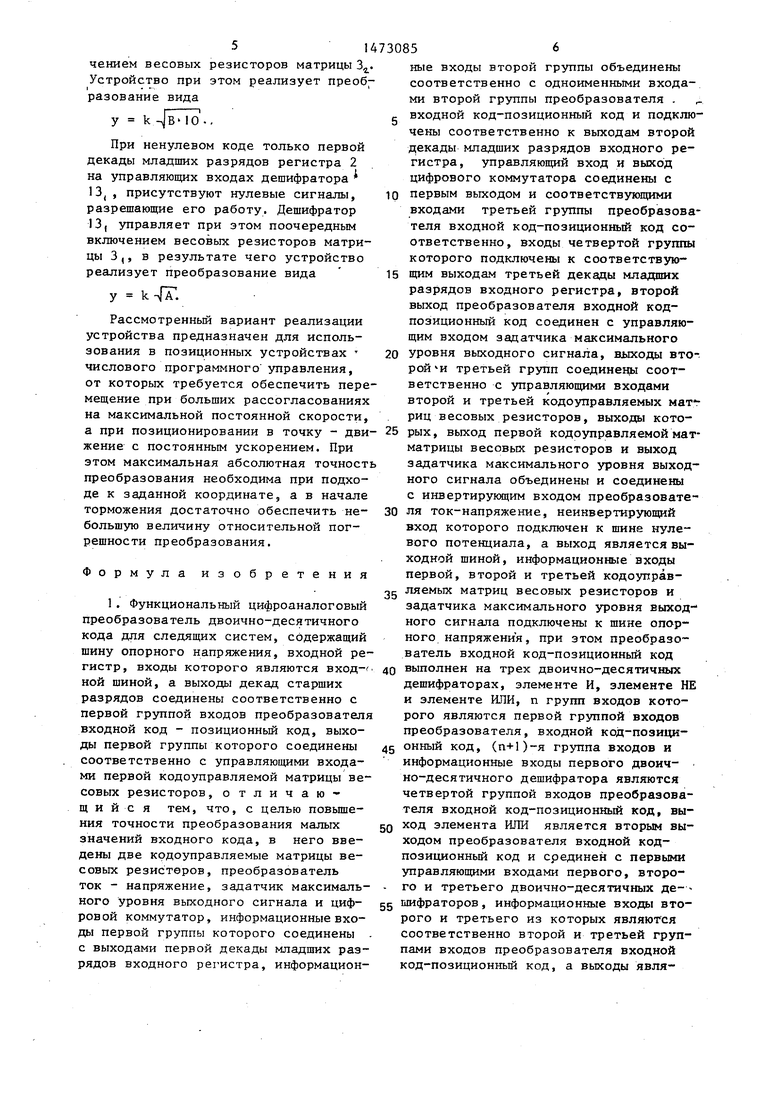

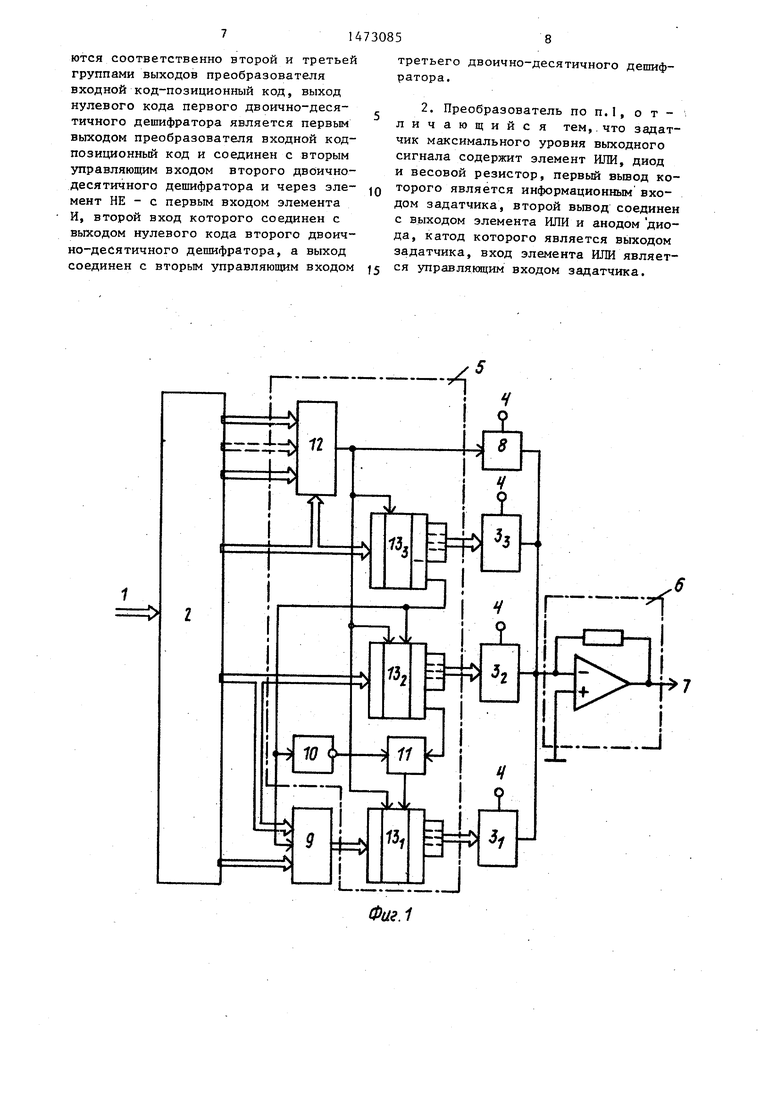

На фиг.I представлена функциональная схема устройства; на фиг.2 - пример реализации задатчика максимального уровня выходного сигнала.

Устройство содержит входную -шину 1, входной регистр 2, кодозшравляе- мые матрицы весовых резисторов, шину 4 опорного напряжения, преобразователь 5 входной код - позиционный код, преобразователь 6 ток - напряжение , выходную шину 7, 3 адатчик 8 максимального уровня вьпсодного сигнала, цифровой коммутатор 9, элемент НЕ. 10,

элемент И 11, элемент ИЛИ 12 и двоично-десятичные дешифраторы 13;,-13з.

Задатчик максимального уровня выходного сигнала содержит весовой резистор 14, элемент ИЛИ 15 и диод 16.

Устройство работает следующим образом. - ,

Двоично-десятичный входной код поступает по шине 1 на входы регистра 2. При коде старших-разрядов, отличном от нуля, на выходе элемента ИЛИ 12 устанавливается единичный сигнал, которьй поступает на первые управляющие входы двоично-десятичных дешифраторов и управляюпяй вход задатчика 8 максимального уровня выходного сигнала. Единичные сигналы на управляющих входах дешифраторов запрещают их работу и вызьшают появление единичных сигналов на их выхо, дах, которые, в свою очередь, запре4i

СО

о

00 ел

147

щают формирование токовых сигналов на выходах кодоуправляемых матриц ,. Единичный сигнал, поступающий на управляющий вход задатчика 8, раз решает прохождение тока с шины 4 с . опорного напряжения через весовой резистор 14 и диод 16 на инвертирующий вход преобразователя 6, в результате чего на шине 7 формируется максималь ный урЪвень выходного аналогового сигнала.

Минимальное значение входного - двоично-десятичного кода, вызывающего появление на выходе элемента И 12 единичного сигнала, а на шине 7 устройства - максимального уровня аналогового сигнала, задается подключением к входу элемента ИЛИ 12 отдельных разрядов четвертой группы входов пре- образователя 5 с большими весами передаваемых по ним сигналов, например с весами 800 или 800 и 400 и т.д.

При подключении к входу, элемента ИЛИ 12 разряда с весом передаваемого кода, равным 800 устройство работает следующим образом.

В процессе уменьшения входного двоично-десятичного кода до значения его десятичного эквивалента, равного 800, на выходе 7 устройства поддерживается максимальный уровень аналогового сигнала. Дальнейшее уменьшение входного кода сопровождается появлением на выходе элемента ИЛИ 12 нуле- вого сигнала, который через элемент ИЛИ 15 шунтирует ток, проходящий через весовой резистор 14, и запрещает поступление тока с выхода задатчика 8 сигнала на вход преобразователя 5; разрешает работу дешифратора снимает запрет работы по первым управляющим входам дешифраторов 13( и 13

чв процессе изменения входного ко- да в диапазоне от 799 до 100 его десятичного эквивалента, на выходе нулевого кода дешифратора 13 сохраняется единичный сигнал, а на остальных выходах (кроме выхода единичного кода в данном случае) последовательно возникает нулевой сигнал, управляющий соответствующим последовательным-г. включением весовых резисторов кодоуправляемой матрицы 3). Единичный сиг- нал с выхода нулевого кода дешифратора 3з запрещает работу дешифратора 13 по его второму управляющему входу, разрешает прохождение на выход

коммутатора 9 кода второй декады младших разрядов регистра 2 и через элемент НЕ 10 совместно с единичным сигналом на втором входе элемента И 11 снимает запрет работы по второму управляющему входу с дешифратора 13, который Формирует, на выходах, соответствующих значениям кода второй декады младших разрядов регистра 2, нулевой сигнал, управляющий величиной тока, поступающего на инвертирующий вход преобразователя 6 с выхода кодоуправляемой матрицы 3,. Т.е. в преобразовании входного кода в диапазоне от 799 до 100 его десятичного эквивалента одновременно участвуют дешифраторы 13, и 13,, в результате чего устройство реализует преобразование вида

У k(

).

которое позволяет аппроксимировать преобразование вида

у kC-AJABc k JA-lO +В-10 +С при условии, что

R;

Rr

где А, В, С - десятичные эквиваленты младших разрядов входного кода)

i l:,2,.. .,9 - номер весового резисто ра в кодоуправляемой матрице, начиная с младшего разряда ; ,2,3 -номер матрицы,

Rj - сопротивление i-ro резистора матрицы.

Последующее уменьшение входного . кода сопровождается появлением нулевого кода третьей декады младших разрядов регистру 2, что вызывает появление на выходе нулевого кода дешифратора 13J нулевого сигнала, который разрешает работу дешифратора 13 по его второму управляющему входу, переключает на выход коммутатора 9 код первой декады младших разрядов регистра 2; через элемент НЕ 10 и элемент И 11, на втором входе которого присутствует единичный сигнал с выхода нулевого кода дешифратора 132, запрещает работу дешифратора 13,.

При изменении входного кода в пределах от 99 до 1-0 его десятичного эквивалента Дешифратор I3,j последовательно формирует на своих выходах нулевой сигнал, который управляет включением весовых резисторов матрицы 3. Устройство при этом реализует преоб разование вида

При ненулевом коде только первой декады младших разрядов регистра 2 на управляющих входах дешифратора 13 , присутствуют нулевые сигналы, разрешающие его работу. Дешифратор 13, управляет при этом поочередным включением весовых резисторов матрицы 3,, в результате чего устройство реализует преобразование вида

у k.

Рассмотренный вариант реализации устройства предназначен для использования в позиционных устройствах числового программного управления, от которых требуется обеспечить перемещение при больших рассогласованиях на максимальной постоянной скорости, а при позиционировании в точку - дни жение с постоянным ускорением. При этом максимальная абсолютная точност преобразования необходима при подходе к заданной координате, а в начале торможения достаточно обеспечить небольшую величину относительной погрешности преобразования.

Формула изобретения

1. Функциональный цифроаналоговый преобразователь двоично-десятичного кода для следящих систем, содержащий шину опорного напряжения, входной регистр, входы которого являются вход- ной шиной, а выходы декад старших разрядов соединены соответственно с первой группой входов преобразователя входной код - позиционный код, выходы первой группы которого соединены соответственно с управляющими входами первой кодоуправляемой матрицы весовых резисторов, о тличаю- щ и и с я тем, что, с целью повьш1е- ния точности преобразования малых значений входного кода, в него введены две крдоуправляемые матрицы весовых резисторов, преобразователь ток - напряжение, задатчик максимального уровня выходного сигнала и цифровой коммутатор, информационные входы первой группы которого соединены . с выходами первой декады младших разрядов входного регистра, информацион0

15

0

5

ные входы второй группы объединены соответственно с одноименньми входами второй группы преобразователя . входной код-позиционный код и подключены соответственно к выходам второй декады младших разрядов входного регистра, управляющий вход и выход цифрового коммутатора соединены с первым выходом и соответствующими входами третьей группы преобразователя входной код-позиционный код соответственно, входы четвертой группы которого подключены к соответствующим выходам третьей декады разрядов входного регистра, второй выход преобразователя входной код- позиционньй код соединен с управляющим входом задатчика максимального уровня выходного сигнала, вьпсоды второй и третьей групп соединены соответственно с управляющими входами второй и третьей кодоуправляемых матриц весовых резисторов, выходы которых, выход первой кодоуправляемой мат- матрицы весовых резисторов и выход задатчика максимального уровня выходного сигнала объединены и соединены с инвертирующим входом преобразовате- 0 ля ток-напряжение, неинвертирующий вход которого подключен к шине нулевого потенциала, а выход является выходной шиной, информационные входы первой, второй и третьей кодоуправ- jg ляемых матриц весовых резисторов и задатчика максимального уровня выходного сигнала подключены к шине опорного напряжения , при этом преобразователь входной код-позиционный код 0 выполнен на трех двоично-десятичных дешифраторах, элементе И, элементе НЕ и элементе ИЛИ, п групп входов которого являются первой группой входов преобразователя, входной код-позици- 5 онный код, (п+1)-я группа входов и информационные входы первого двоич- но-десятичного дешифратора являются четвертой группой входов преобразователя входной код-позиционный код, вы- Q ход элемента ИЛИ является вторым выходом преобразователя входной код- позиционный код и срединен с первыми управляющими входами первого, второ- го и третьего двоично-десятичных де- 5 шифраторов, информационные входы второго и третьего из которых являются соответственно второй и третьей группами входов преобразователя входной код-позиционный код, а выходы являются соответственно второй и третьей группами выходов преобразователя входной код-позиционный код, выход нулевого кода первого двоично-десятичного дешифратора является первым выходом преобразователя входной код- позиционный код и соединен с вторым управляющим входом второго двоично- десятичного дешифратора и через элемент НЕ - с первым входом элемента И, второй вход которого соединен с выходом нулевого кода второго двоично-десятичного дешифратора, а выход соединен с вторым управляющим входом

третьего двоично-десятичного дешифратора.

2. Преобразователь по п.1, отличающийся тем,.что задат- чик максимального уровня выходного сигнала содержит элемент ИЛИ, диод и весовой резистор, первый вьшод которого является информационным входом задатчика, второй вьшод соединен с выходом элемента ИЛИ и анодом диода, катод которого является выходом задатчика, вход элемента ИЛИ является управлякицим входом задатчика.

| название | год | авторы | номер документа |

|---|---|---|---|

| Двоично-десятичный цифроаналоговый преобразователь | 1987 |

|

SU1575313A1 |

| АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1995 |

|

RU2106009C1 |

| Устройство индикации измерительного прибора | 1984 |

|

SU1262395A1 |

| УСТРОЙСТВО ДЛЯ ТЕКУЩЕГО КОНТРОЛЯ И СТАТИСТИЧЕСКОГО АНАЛИЗА ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1997 |

|

RU2130199C1 |

| Аналого-цифровой преобразователь | 1981 |

|

SU970680A1 |

| СТАТИСТИЧЕСКИЙ АНАЛИЗАТОР ОТКЛОНЕНИЙ НАПРЯЖЕНИЯ | 1992 |

|

RU2041497C1 |

| Фазоимпульсный сумматор | 1980 |

|

SU885996A1 |

| Умножитель числа импульсов | 1988 |

|

SU1499458A1 |

| Устройство для логарифмирования | 1977 |

|

SU708343A1 |

| Устройство для программного счета изделий | 1983 |

|

SU1113824A1 |

Изобретение относится к вычислительной технике и может быть использовано в следящих системах ,в частности, в позиционных устройствах числового программного управления. Преобразователь обеспечивает формирование выходного аналогового сигнала, изменяющегося по закону монотонной функции, с максимальной точностью преобразования малых значений входного кода, что позволяет обеспечить необходимое для управления сервоприводами позиционных механизмов возрастание точности преобразования кода в аналоговый сигнал по мере приближения к заданной координате и снижения скорости перемещения. 1 з.п.ф-лы, 2 ил.

Iл

f

Фа.1

OtaS

| Функциональный преобразователь цифровой величины в непрерывную | 1960 |

|

SU131108A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Видоизменение прибора для получения стереоскопических впечатлений от двух изображений различного масштаба | 1919 |

|

SU54A1 |

Авторы

Даты

1989-04-15—Публикация

1986-04-07—Подача