Изобретение относится к вычислительной технике и может быть использовано в устройствах дистанционного ввода информации в цифровые приборы, работающие в условиях воздействия электромагнитных помех и разрядов статического электричества.

Цель изобретения повышение достоверности шифрации за счет восстановления искаженного символа выходного кода.

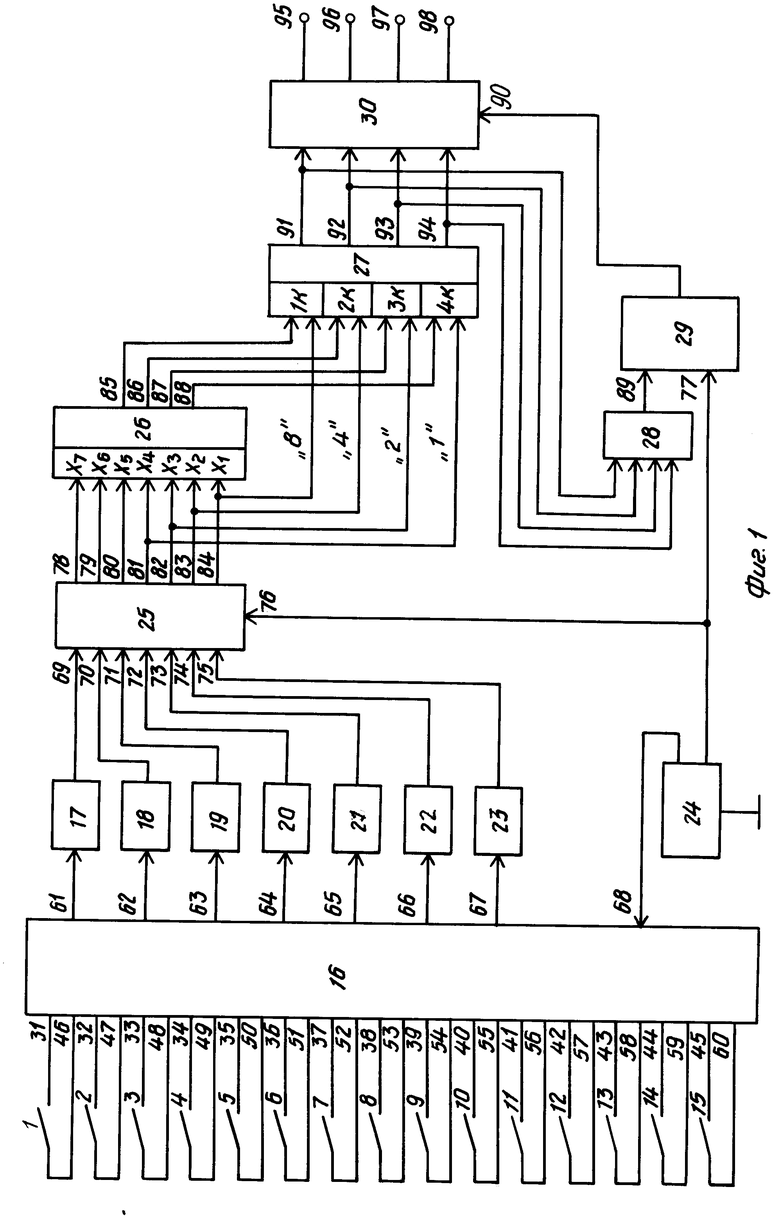

На фиг. 1 приведена схема шифратора с пятнадцатью ключами (K 4); на фиг. 2.10 приведены схемы его функциональных элементов.

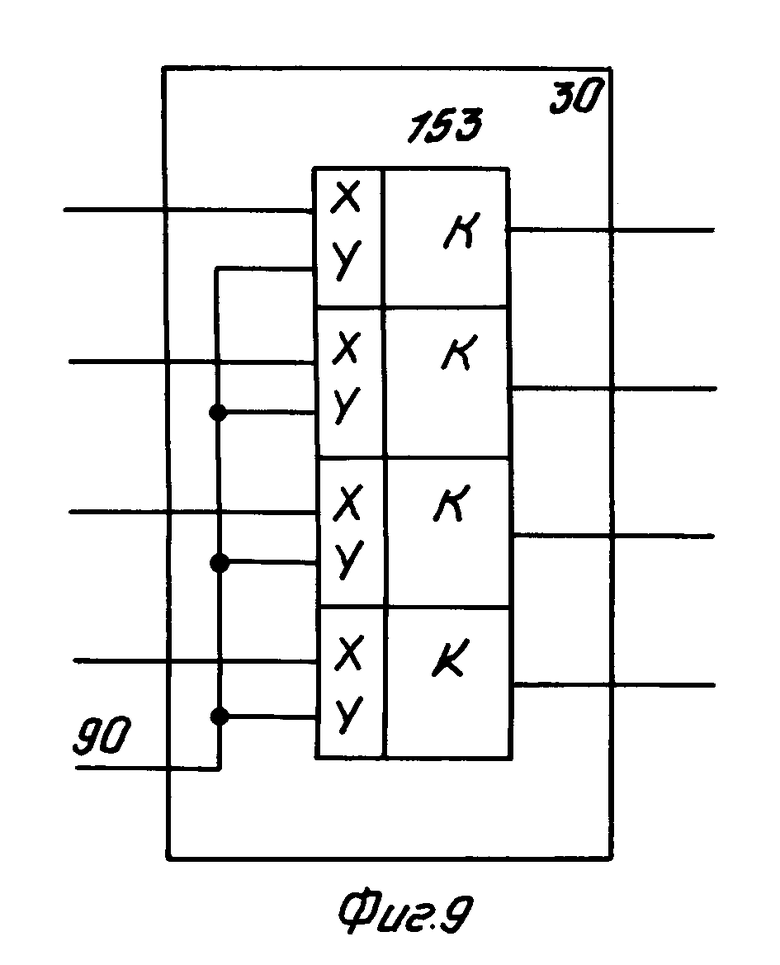

Шифратор содержит ключи 1.15, трансформаторный преобразователь 16 единичного кода в корректирующий код, аналоговые элементы 17.23 памяти, формирователь 24 импульсов считывания, блок 25 оперативной памяти, блок 26 анализа кода, блок 27 коррекции выходного кода, обнаружитель 28 кодового слова, формирователь 29 одиночного импульса и блок 30 коммутаторов. Первые и вторые выводы ключей 1.15 соединены с соответствующими информационными входами 31. 45 и 46.60 соответственно трансформаторного преобразователя 16, выходы 61.67 которого соединены с входами соответствующих элементов 17.23 памяти, а тактовый вход 68 подключен к первому выходу формирователя 24. Выходы элементов 17.23 памяти соединены с соответствующими информационными входами 69.75 блока 25, тактовый вход 76 которого объединен с тактовым входом 77 формирователя 29 и подключен к второму выходу формирователя 24, а выходы 78.84 соединены с одноименными входами блока 26. Первые четыре входа (первые входы каналов) блока 27 подключены к одноименным выходам 81.84 блока 25, вторые четыре входа (вторые входы каналов) к одноименным выходам 85.88 блока 26. Управляющий вход 89 формирователя 29 подключен к выходу обнаружителя 28 кодового слова, выход соединен с управляющим входом 90 блока 30 коммутаторов, информационные входы которого объединены с входами обнаружителя 28 кодового слова и подключены к соответствующим выходам 91.94 блока 27, а выходы являются выходами 95.98 шифратора.

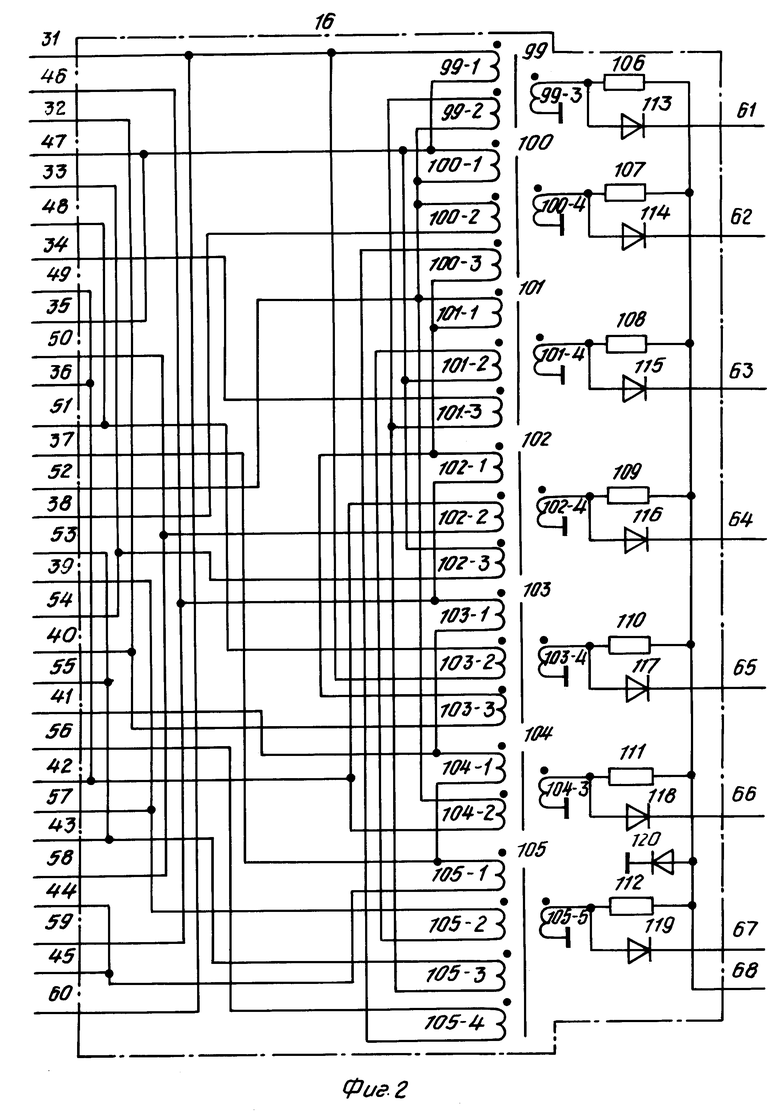

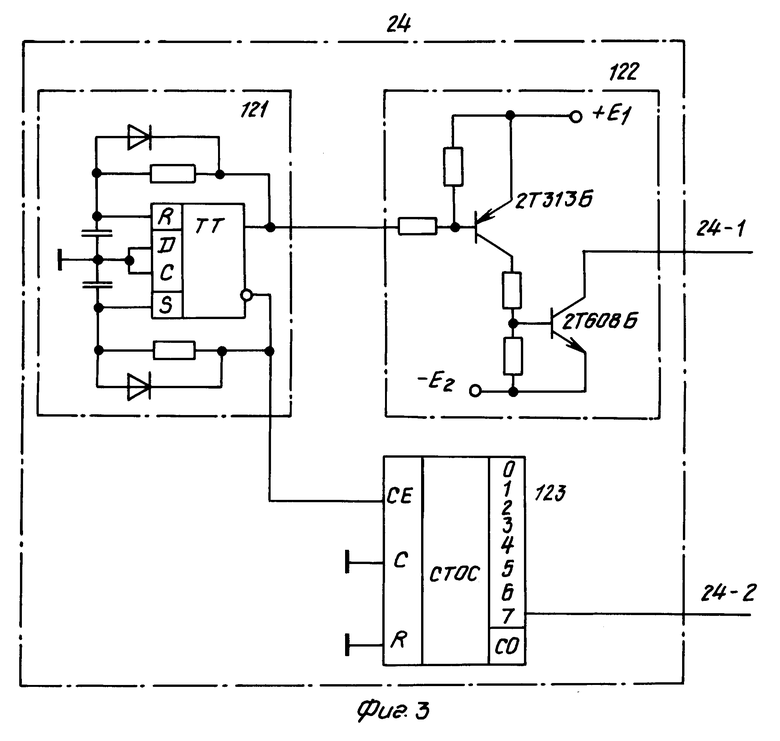

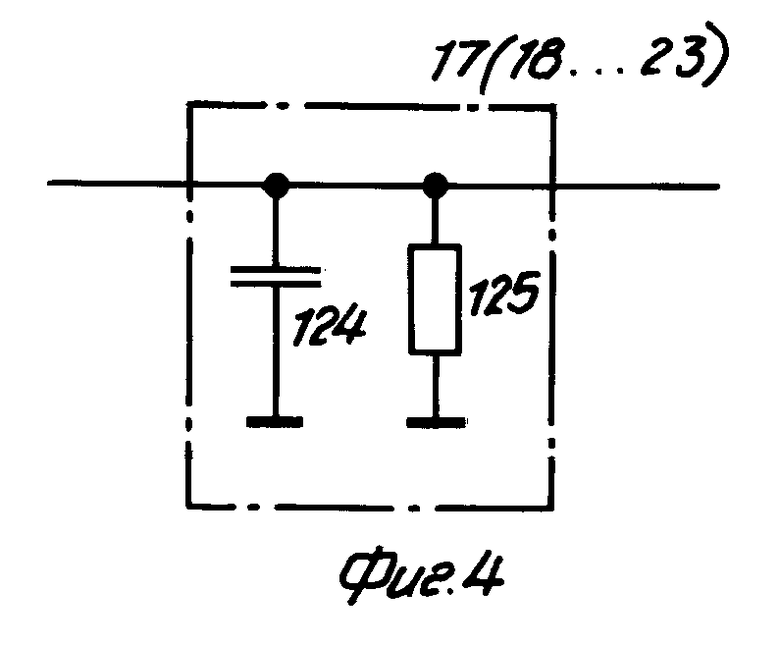

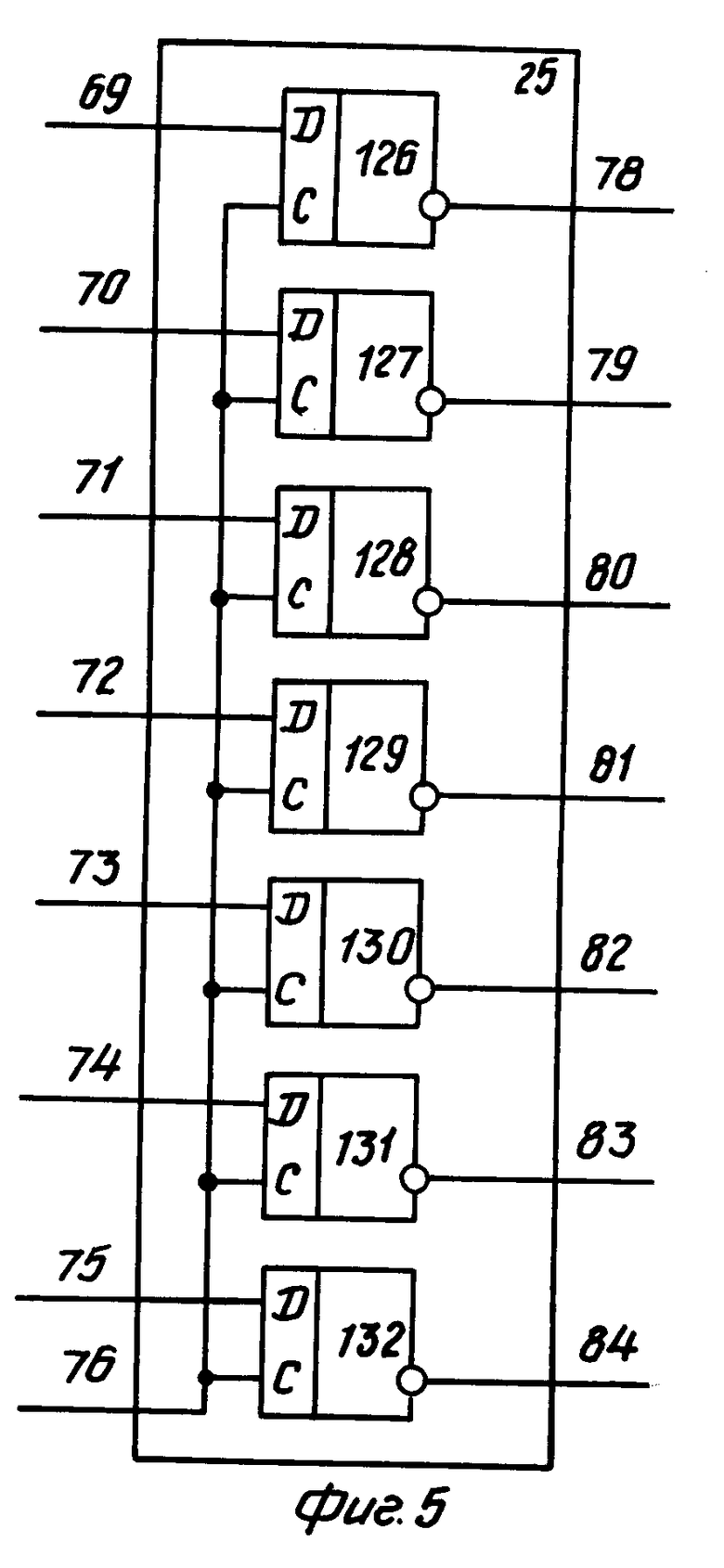

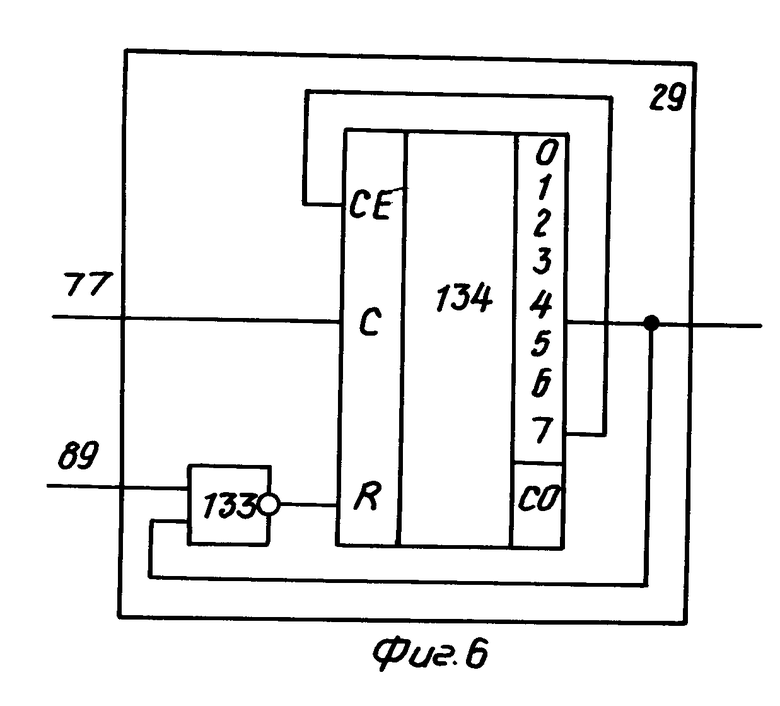

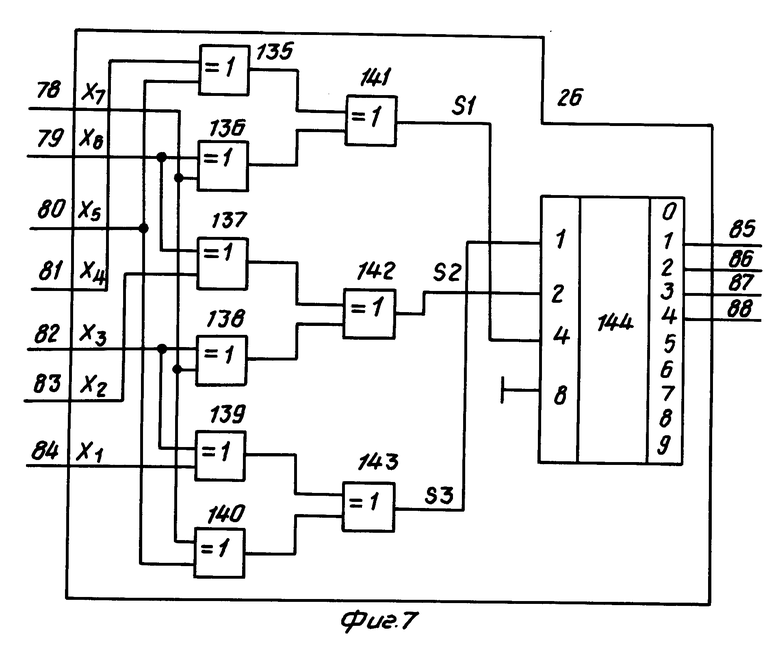

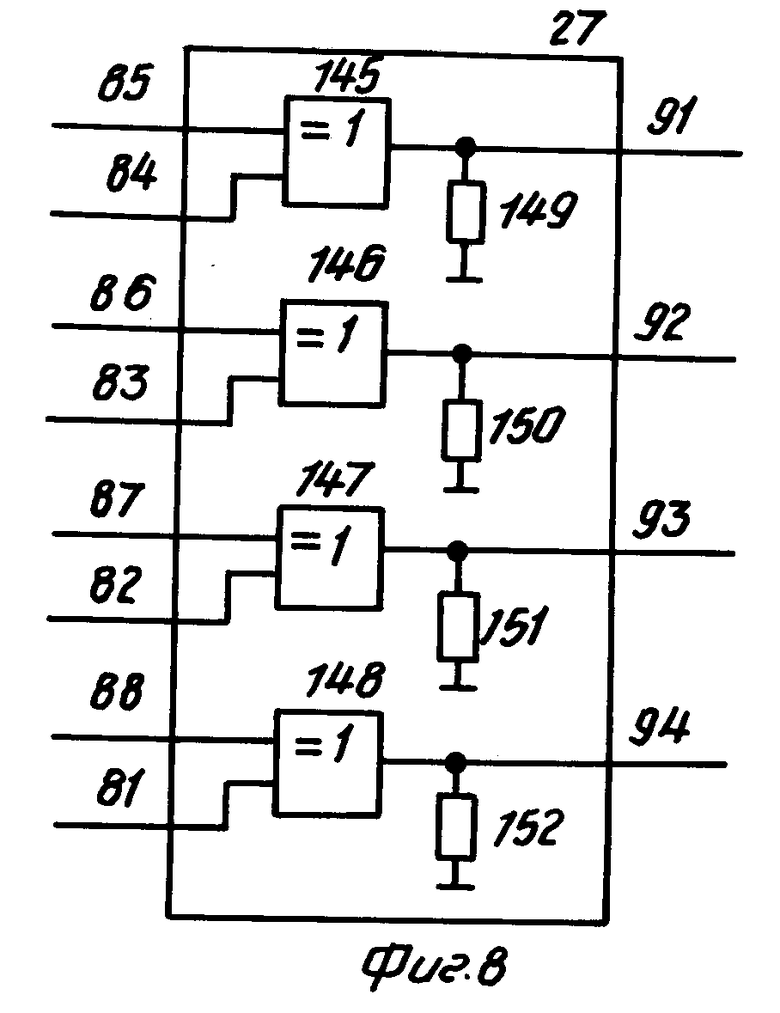

Преобразователь 16 (фиг. 2) содержит трансформаторы 99.105, резисторы 106.112 и диоды 113.120. Формирователь 24 импульсов считывания (фиг. 3) состоит из блоков 121, 122 и 123. Элемент 17 (18.23) памяти (фиг. 4) содержит конденсатор 124 и резистор 125. Блок 25 оперативной памяти (фиг. 5) состоит из D-триггеров 126.132. Формирователь 29 одиночного импульса (фиг. 6) содержит элементы 133 и 134. Блок 26 анализа кода (фиг. 7) состоит из элементов 135.143 и дешифратора 144. Блок 27 коррекции выходного кода (фиг. 8) содержит элементы 145.148 и резисторы 149.152. Блок 30 состоит из коммутаторов 153 (фиг. 9) или коммутатора 154 (фиг. 10).

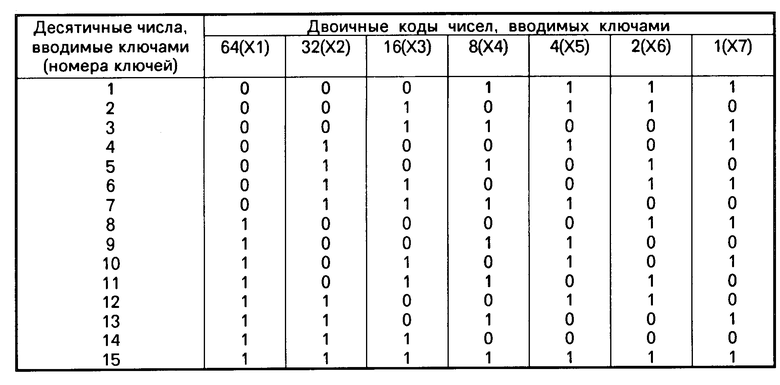

Ключами 1.15 в преобразователь 16 вводятся десятичные числа, совпадающие с порядковыми номерами ключей. Двоичные коды этих чисел, формируемые в преобразователе 16 с помощью трансформаторов 99.105 в соответствии с требованиями к коду Хэмминга длины семь с четырьмя информационными разрядами, приведены в таблице.

Как видно из таблицы, четыре слева символа (X1, X2, X3, X4) самиразрядных двоичных кодов ключей представляют собой четырехразрядные двоичные коды (8421) десятичных чисел, вводимых ключами 1.15. Остальные три символа (X5, X6, X7) указанных кодов ключей 1.15 подобраны в соответствии с требованиями к коду Хэмминга из следующих соотношений:

X5 X2 + X3 + X4;

X6 X1 + X3 + X4;

X7 X1 + X2 + X4. (1)

Блок 26 проверяет для семиразрядных двоичных кодов ключей, формируемых в преобразователе 16 в соответствии с требованиями к коду Хэмминга, выполнение следующих проверочных соотношений (сумм):

S1 X4 + X5 + X6 + X7;

S2 X2 + X3 + X6 + X7;

S3 X1 + X3 + X5 + X7. (2)

Когда все суммы (по модулю два) равны нулю, на выходах блока 26 сигналы отсутствуют, и это означает, что в коде ошибки нет. Если какая-либо из указанных сумм не равна нулю, т.е. равна единице, то это означает, что в анализируемом коде есть ошибка. При этом номер выхода блока 26, где появляется выходной сигнал, указывает разряд выходного кода шифратора, где имеется ошибка.

Работает шифратор следующим образом.

В исходном состоянии ключи 1.15 разомкнуты, формирователь 24 формирует на своем первом выходе последовательность импульсов отрицательной полярности, на втором выходе положительной полярности с меньшей частотой следования. Импульсами с первого выхода данного формирователя через резисторы 106.112 (фиг. 2), выходные обмотки трансформаторов 99.105 преобразователя 16 "опрашиваются" состояния ключей 1.15. Пpи этом магнитные сердечники трансформаторов 99.105 при разомкнутых ключах насыщаются, на выходах дифференцирующих цепей, образованных последовательно соединенными резисторами 106.112 и выходными обмотками соответствующих трансформаторов 99.105, формируются разнополярные импульсы на фронте и срезе каждого импульса формирователя 24. Импульсы положительной полярности, формируемые на срезе импульсов, поступающих с первого выхода указанного формирователя, через диоды 113.119 проходят на элементы 17.23 памяти, конденсаторы которых заряжаются до уровня логической "1". Этот уровень поступает на информационные входы блока 25, запоминается D-триггерами 126.132 (фиг. 5) последнего и подтверждается каждым последующим импульсом на его тактовом входе 76. При этом на выходах данного блока поддерживается уровень логического "0", который поступает на входы блока 26 и на вторые входы каналов блока 27. На выходах блока 26 сохраняется уровень логического "0". При этом на первых входах всех каналов блока 27 поддерживается уровень логического "0", поэтому на его выходах 91.94 уровень логического "0". Формирователь 29 поддерживается в исходном состоянии уровнем логического "0" с выхода обнаружителя 28 кодового слова, и на его выходе уровень логического "0". На выходах блока 30 коммутаторов также сохраняется уровень логического "0". Указанные исходные состояния функциональных блоков шифратора сохраняются до замыкания какого-либо из ключей 1.15.

Рассмотрим работу шифратора при отсутствии каких-либо отказов элементов.

При замыкании какого-либо из ключей 1.15 происходит закорачивание последовательно включенных соответствующих входных обмоток трансформаторов 99.105 преобразователя 16 (фиг. 1 и 2) в соответствии с приведенной таблицей. Например, при замыкании ключа 3 закорачиваются входные обмотки 102-3, 99-1 и 103-2 трансформаторов 102, 99 и 103 с весовыми коэффициентами 8,1 и 16 соответственно. При этом входные сопротивления выходных обмоток 102-4, 99-3 и 103-4 соответствующих трансформаторов для импульсов формирователя 24 резко уменьшаются, и все напряжение импульсов указанного формирователя практически падает на резисторах 109, 106 и 110 соответствующих дифференцирующих цепей, на выходах последних исчезают импульсы, формируемые на фронте и срезе импульсов формирователя 24. Поэтому после замыкания ключа 3 прекращается поступление импульсов положительной полярности на входы элементов 20, 17 и 21 памяти, а на входы элементов 18, 19, 22 и 23 они продолжают поступать. В результате на выходах элементов 20, 17 и 21 памяти устанавливается потенциальный сигнал с уровнем логического "0", а на выходах элементов 18, 19, 22 и 23 сохраняется исходный уровень логической "1". При этом на выходах 78, 81 и 82 блока 25 устанавливается уровень логической "1", а на выходах 79, 80, 83 и 84 сохраняется исходный уровень логического "0", т.е. на выходах блока 25 будет код 0011001 (старшие разряды кода слева).

Указанная комбинация сигналов поступает на входы блока 26, а на вторые входы каналов блока 27 при этом сигналы поступают с выходов четырех старших разрядов блока 25. При указанной комбинации сигналов на входах блока 26 на его выходах сохраняется исходное состояние логического "0", поскольку комбинация удовлетворяет приведенной таблице, и суммы S1, S2 и S3 в соотношениях (2) равны нулю. При наличии уровня логического "0" на одном входе в каждом из каналов блока 27 на выход каждого из его каналов (фиг. 8) выдается уровень сигнала, имеющийся на другом входе канала. Следовательно, в нашем случае, когда замкнут ключ 3, на выходы блока 27 выдается код 0011, т.е. двоичный код десятичного числа 3 (номера замкнутого ключа 3), и сохраняется на все время замкнутого состояния ключа.

Одновременно (после замыкания ключа 3) появление уровня логической "1" на любом из выходов блока 27 приводит к появлению уровня логической "1" на выходе обнаружителя 28 кодового слова, что приводит к запуску формирователя 29. С задержкой, большей времени возможной разновременности появления сигналов на выходах блока 25, формирователь 29 формирует одиночный импульсный сигнал, который поступает на управляющий вход 90 блока 30 коммутаторов. При этом в течение этого импульса на выходы 95.98 шифратора выдается код (в нашем случае 0011), присутствующий на его входах.

При размыкании замкнутого ключа 3 описанное выше исходное состояние шифратора автоматически восстанавливается: входные сопротивления выходных обмоток 99-3, 102-4 и 103-4 трансформаторов 99, 102 и 103 (фиг. 2) резко увеличиваются, на входах элементов 17, 20 и 21 памяти снова появляются импульсы положительной полярности, на выходах 78, 81 и 82 блока 25 восстанавливается исходный уровень логического "0", на выходе обнаружителя 28 кодового слова также уровень логического "0", блокирующий запуск формирователя 29.

При замыкании любого другого из ключей 1.15 шифратор при отсутствии отказов элементов, т. е. когда на выходах блока 25 коды соответствуют приведенной таблице, работает аналогично, при этом на выходы 95.98 шифратора выдаются двоичные коды десятичных чисел, вводимых ключами 1.15.

Рассмотрим теперь работу шифратора при наличии отказа его функциональных элементов, приводящего к искажению одного разряда (так называемый "одиночный отказ") кода замыкаемого ключа, формируемого в соответствии с приведенной таблицей, на выходах блока 25 на примере замыкания того же ключа 3.

Допустим, что в шифраторе имеет место отказ (или отказы), искажающий седьмой (X1, см. таблицу) разряд (который формируется трансформатором 105) двоичного кода ключа (например, обрыв выходной обмотки 105-5 трансформатора 105, обрывы выводов резистора 112 или диода 119, нарушение паек указанных элементов, отказ D-триггера 132 блока 25 и т.д.). Тогда при замыкании ключа 3 на выходах блока 25 вместо двоичного кода 0011001 (см. таблицу) имеет место код 1011001, т.е. на выходе 84 блока 25 вместо требуемого уровня логического "0" будет уровень логической "1". Следовательно, на входах блока 26, выполняющего суммирование слагаемых по модулю два в соответствии с соотношениями (2), слагаемые (X1.X7) имеют следующие значения: X1 1, X2 0, X3 1, X4 1, X5 0, X6 0, X7 1. При таких значениях слагаемых X1.X7 сумма S3 на выходе элемента 143 (фиг. 7) равна единице, суммы S1 и S2 соответственно на выходах элементов 141 и 142 равны нулю. Поэтому на входах дешифратора 144 присутствует двоичный код 001 числа 1, следовательно, выходной сигнал (уровень логической "1") появляется на выходе 85 блока 26 и поступает на первый вход первого канала блока 27. Второй вход первого канала блока 27 соединен с выходом 84 блока 25, где из-за отказа имеется логическая "1" вместо логического "0". При такой комбинации входных сигналов на выходе данного канала блока 27 будет логический "0" (фиг. 8), т.е. исправляется искаженный символ разряда кода на выходе блока 25. Поскольку вторые входы каналов блока 27 подключены к четырем выходам 81.84 старших разрядов блока 25, на выходах блока 27 будет код 0011, т.е. двоичный код числа 3, совпадающего с номером замкнутого ключа 3. Этот код поступает на информационные входы блока 30 коммутаторов, на управляющий вход 90 которого с выхода формирователя 29 поступает импульсный сигнал, задержанный относительно момента появления кода замкнутого ключа 3 на выходах блока 25 и, следовательно, относительно момента появления разрешающего сигнала на выходе обнаружителя 28 кодового слова. В результате на выходы 95.98 шифратора импульсно выдается исправленный двоичный код 0011 замкнутого ключа 3.

Рассмотрим теперь работу шифратора в случае отказов, приводящих к выдаче в одном из разрядов двоичного кода замкнутого ключа 3 на выходах блока 25 вместо логической "1" логического "0". Такая ситуация может быть, например, в случаях, когда какой-либо D-триггер блока 25 не переключается, когда это нужно, в нулевое состояние (исходное состояние D-триггеров 126.132 блока 25 единичное).

Допустим, что при замыкании ключа 3 из-за отказа не переключается D-триггер 126 блока 25 (фиг. 5) в цепи первого разряда двоичного кода ключа. Тогда на выходах блока 25 вместо кода 0011001 присутствует код 0011000. Следовательно, слагаемые (X1.X7) на входах блока 26 имеют следующие значения: X1 X2 0, X3 X4 1, X5X6 X7 0. При таких значениях слагаемых суммы по модулю два S1, S2 и S3 на выходах соответственно элементов 141, 142 и 143 блока 26 (фиг. 7) все равны единице, т.е. к входам дешифратора 144 данного блока приложен двоичный код 111 числа 7. Следовательно, выходной сигнал будет на выходе "7" дешифратора 144 и не проходит на выходы блока 26. Это означает, что в данном случае отказа в шифраторе коррекции какого-либо символа выходного четырехразрядного двоичного кода шифратора нет. Действительно в рассмотренном случае коррекция этого кода и не нужна, поскольку в четырех старших разрядах семиразрядного кода на выходе блока 25, с которых снимается и через блоки 27 и 30 выдается на выходы шифратора четырехразрядный двоичный код замкнутого ключа, ошибки не было: там, несмотря на указанный отказ, был код 0011, т.е. код замкнутого ключа 3, который и выдается на выходы 95.98 шифратора.

При замыкании других ключей при наличии отказов в шифраторе, приводящих к искажению одного символа кода на выходах блока 25 (превращение логической "1" в логический "0" или наоборот), шифратор работает аналогично.

Таким образом, при замыкании любого из ключей 1.15 на выходах блока 25 шифратора появляется (в течение замкнутого состояния ключа) семиразрядный двоичный код в соответствии с приведенной таблицей. Четыре старших разряда этого кода являются информационными, т.е. содержат информацию о порядковых номерах замыкаемых ключей, а три младших разряда (снимаемые с трансформаторов 99.101 преобразователя 16) являются проверочными. Информация о номере замкнутого ключа выдается на выходы 95.98 шифратора кратковременно (в течение импульса формирователя 29) по окончании переходных процессов при замыкании ключей. При этом если в шифраторе имеются отказы, приводящие к искажению одного символа (одиночный отказ) кодов ключей в разрядах, снимаемых с трансформаторов 102.105 преобразователя 16 и выдаваемых на выходы шифратора, то этот искаженный символ восстанавливается.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННЫМ ЗАМКОМ | 2002 |

|

RU2209909C1 |

| РЕГИСТР СДВИГА | 1993 |

|

RU2110099C1 |

| ЭЛЕКТРОННЫЙ ЗАМОК | 2002 |

|

RU2213191C1 |

| СЧЕТНОЕ УСТРОЙСТВО | 1992 |

|

RU2040113C1 |

| ТАЙМЕР С КОНТРОЛЕМ | 1990 |

|

RU2037872C1 |

| УСТРОЙСТВО ДЛЯ СЧЕТА ИМПУЛЬСОВ | 1993 |

|

RU2065250C1 |

| РЕГИСТР ПАМЯТИ | 1993 |

|

RU2106698C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ЭЛЕКТРОННОГО ЗАМКА | 2003 |

|

RU2235178C1 |

| СЧЕТЧИК ИМПУЛЬСОВ, СОХРАНЯЮЩИЙ ИНФОРМАЦИЮ ПРИ ПЕРЕРЫВАХ ПИТАНИЯ | 1991 |

|

RU2047271C1 |

| ЭЛЕКТРОННО-МЕХАНИЧЕСКИЙ ЗАМОК | 2003 |

|

RU2246601C2 |

Изобретение относится к вычислительной технике. Его использование в устройствах дистанционного ввода информации, работающих в условиях воздействия электромагнитных помех и разрядов статического электричества, позволяет повысить достоверность шифрации за счет восстановления искаженного символа выходного кода. Это достигается благодаря введению в шифратор дополнительных элементов аналоговой памяти и блока коррекции выходного кода, а также выполнению трансформаторного преобразователя единичного кода в корректирующий код в виде трансформаторного преобразователя единичного кода в код Хэмминга. 2 з.п. ф-лы, 1 табл., 10 ил.

соединены соответственно с (2i 1)-м и 2i-м информационными входами трансформаторного преобразователя единичного кода в корректирующий код, первый (K + 1)-й выходы которого через соответственно первый (K + 1)-й аналоговые элементы памяти соединены с соответствующими информационными входами блока оперативной памяти, первый (K + 1)-й выходы которого подключены к одновременным входам блока анализа кода, формирователь импульсов считывания, первый выход которого подключен к тактовому входу трансформаторного преобразователя единичного кода в корректирующий код, второй выход формирователя импульсов считывания соединен с тактовыми входами блока оперативной памяти и формирователя единичного импульса, выход которого подключен к управляющему входу блока коммутаторов, информационные входы которого соответственно объединены с входами обнаружителя кодового слова, выход которого соединен с управляющим входом формирователя одиночного импульса, выходы блока коммутаторов являются выходами шифратора, отличающийся тем, что, с целью повышения достоверности шифрации за счет восстановления искаженного символа выходного кода, в шифратор введены (K + 2)-й и n-й аналоговые элементы памяти (n общее число символов корректирующего кода Хэмминга) и блок коррекции выходного кода, а трасформаторный преобразователь единичного кода в корректирующий код выполнен в виде трансформаторного преобразователя единичного кода в код Хэмминга (K + 2)-й n-й выходы которого через соответственно (K + 2)-й n-й аналоговые элементы памяти соединены с одноименными информационными входами блока оперативной памяти, первый K-й входы блока коррекции выходного кода подключены к одновременным выходам блока оперативной памяти, (K + 2)-й n-й выходы которого соединены с одноименными входами блока анализа кода, первый - K-й выходы которого подключены к (K + 1)-му 2K-му входам блока коррекции выходного кода, первый K-й выходы которого соединены с одноименными информационными входами блока коммутаторов.

соединены соответственно с (2i 1)-м и 2i-м информационными входами трансформаторного преобразователя единичного кода в корректирующий код, первый (K + 1)-й выходы которого через соответственно первый (K + 1)-й аналоговые элементы памяти соединены с соответствующими информационными входами блока оперативной памяти, первый (K + 1)-й выходы которого подключены к одновременным входам блока анализа кода, формирователь импульсов считывания, первый выход которого подключен к тактовому входу трансформаторного преобразователя единичного кода в корректирующий код, второй выход формирователя импульсов считывания соединен с тактовыми входами блока оперативной памяти и формирователя единичного импульса, выход которого подключен к управляющему входу блока коммутаторов, информационные входы которого соответственно объединены с входами обнаружителя кодового слова, выход которого соединен с управляющим входом формирователя одиночного импульса, выходы блока коммутаторов являются выходами шифратора, отличающийся тем, что, с целью повышения достоверности шифрации за счет восстановления искаженного символа выходного кода, в шифратор введены (K + 2)-й и n-й аналоговые элементы памяти (n общее число символов корректирующего кода Хэмминга) и блок коррекции выходного кода, а трасформаторный преобразователь единичного кода в корректирующий код выполнен в виде трансформаторного преобразователя единичного кода в код Хэмминга (K + 2)-й n-й выходы которого через соответственно (K + 2)-й n-й аналоговые элементы памяти соединены с одноименными информационными входами блока оперативной памяти, первый K-й входы блока коррекции выходного кода подключены к одновременным выходам блока оперативной памяти, (K + 2)-й n-й выходы которого соединены с одноименными входами блока анализа кода, первый - K-й выходы которого подключены к (K + 1)-му 2K-му входам блока коррекции выходного кода, первый K-й выходы которого соединены с одноименными информационными входами блока коммутаторов. подключены к входам блока в соответствии с j-й строкой проверочной матрицы используемого кода Хэмминга, выходы K 1 сумматоров по модулю два соединены с соответствующими входами дешифратора, выходы которого являются соответствующими выходами блока.

подключены к входам блока в соответствии с j-й строкой проверочной матрицы используемого кода Хэмминга, выходы K 1 сумматоров по модулю два соединены с соответствующими входами дешифратора, выходы которого являются соответствующими выходами блока.

| ШИФРАТОР | 1988 |

|

SU1605892A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1995-04-20—Публикация

1989-12-29—Подача