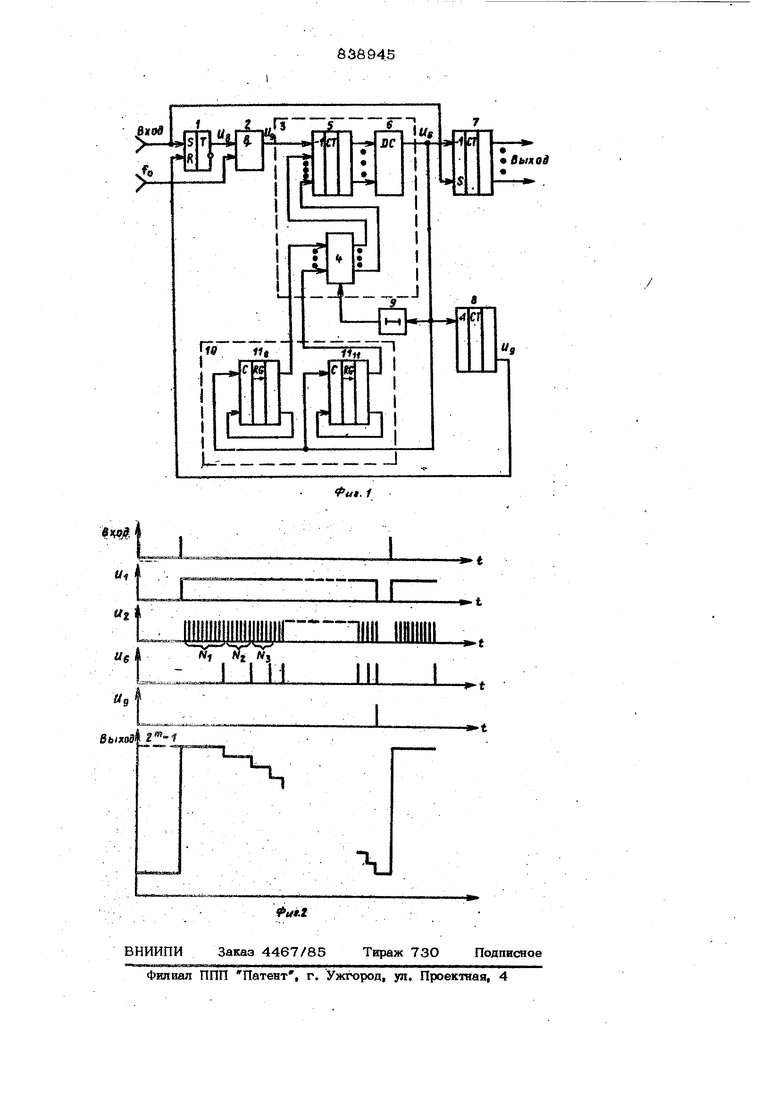

(54) УСТРОЙСТВО ДЛЯ ФОРМИРОВАНИЯ ОПОРНОГО СИГНАЛА вым принципом формирования кусочно линейного напряжения. На точность сущёст-i венно влияют нестабильность источника опорного напряжения и органа сравнения, поцверженность цестабилизируюхйим факторам элементов времязацающих уртройств. Все это в конечном счете приводит к невысокой точности линеаризации статичес- кой регулировд)чной характеристики тиристорного преобразователя. Цель изобретения - повышение точнос-ти ффмирования опорного сигнала. Цель достигается тем, что устройство цля формирования опорного сигнала, содержащее -триггер, S -вход которого соединен с входной шиной, генератор так- говой частоты и связанные с блоком срав нения элемент задержки г времязадающий блок, снабжено элементом U , вычита ющим счетчиком и счетчиком циклов, при- чем прямой выход -триггера соедине через элемент И с тактсеым входом блока сравнения, выход которого соединен со счетным входом вычитающего счетчика и с входом времяаадающего блока, входная шина соединена с установочным входом вычитающего счетчика, а генератор тактовой частоты соепинен со вторым входом элемента И. Блок сравнения вьшолнен в виде вычитающего счетчика, уста- новочные входы которого соединены с коммутатором, а разрядные выходы подключены к вешифратору. Времязадающее устройство выполнено в виде кольцевых регистров сдвига с объединенными тактовыми входами. iHa фиг. I представлена функциональна схема предлагаемого устройства; на фиг. 2 - временные диаграммы импульсов в различных его цепях. Устройство содержит S -триггер 1 соединенный S -входом с шиной Вход, а прямым выходом - со входом элемента И 2, ко второму входу которого подключ на шина тактовой частоты f . Выход элемента И 2 соединен с тактовым входом блока 3 сравнения, выполненного в виде коммутатбра 4, вычитающего счетчика 5 и дешифратора 6. Выход блока 3 сравнения соединен со счетныМи входами вычитающего с ютчика 7 и счетчика 8 циклов, а через элемент 9 задержки с управляющим входом коммутатора 4, Кроме того вход дешифратора 6 подключен ко вхору времязадающего блока Ю, выполненного в виде кольцевых регистррв II сгавига, тактовые входы коорых соединены между собой, а выходы оединены с входами коммутаторов 4. Устройство работает следующим образом. При переходе напряжения, питающего преобразователь, через нуль по входной шине поступает импульс, устанавливающий триггер 1 в единичное состояние, а вычитающий счетчик 7 устанавливается в исходное состояние. При этом на бпок 3 сравнения начинают поступать через элемент И 2 импульсы от генератора тактовой частоты, следующие с частотой в исходном состоянии в счетчик 5 было занесено некоторое число N, и когда на него поступит М тактовых импульсов, записанное в счетчике число станет равным О. Это фиксируется дешифратором 6, который срабатывает и выдает импульс, который уменьшает записанное в счетчике 7 число на единицу, увеличивает записанное в счетчике 5 на единицу, сдви- гает информацию, записанную в времязагдающем блоке 10 на один разряд и через интервал времени, определяемом элементом 9 задержки , разрешает внесение в счетчик 5 нового числа Nr , Число Ni считывается с выходов регистров 11 сдвига времязадающего блока 10 через коммутатор 4. Очерепной импульс на выходе дешифратора 6 появится после того, как на вход счетчика 5 поступит М импульсов от генератора тактовой частоты и процесс описанный выше повторяется. Причем в кольцевых регистрах II сдвига циркулирует код, который при сдвигах разрядов на л -ом шаге обеспечивает поступление на счетчик 5 числа N определяемого соотношением ы. , . i bfoO.f ,sj где ot/ at-ccos число разрядов счетчика 7, m частота сети, питatoщeй тиристйрный преобразователь. Процесс продолжается до переполнения счетчика 8, коэффициент пересчета которого выбирается равным : .t;l()fji-r), где fikf,; - величина нестабильности частоты сети, бпЪ - символ целой части числа. Так например, цля m 8 и Ь,. К 250. Импульс переполнения счетчика 8 устанавливает триггер I в ну1Ь. К этому моменту на выходах верхних разрядов кольцевых регистров сдвига вновь присутствует код Н переписываемый через .время, определяемое моментом зраержки элемента 9 в счетчик 5. Очередной цикл формирования опорного сигнала начикается при поступлении очерерного. импульса по шине Вход, т.е. наличие счетчика 8 с коэффициентом -пересчета К 1 определяет сужение диапазона регулирования. Однако, реальное умень-15

шение диапазона регулирования весьма незначительно. Так , 1Гц диапазон регулирования сужается на 1, 1,95%, Что соизмеримо с аналогичным воздействием на диапазон регулирования углов коммутации мсяцных тиристоров. V

Предлагаемое устройство выгодно отличается от известных устройств точностью формирования опорного сигнала. Последня при стабильной получаемой с помощью кварцевого генератора частоте IQ определяется только разрядностью счетчике и регистров. Кроме того, предлагаемое, устройство удобно использовать в системах прямого цифрового управления, где величина управляющего воздействия задается от цифрового вычислительного yci ройства ( в частности от Ц AM) в виде цифрового кода.

Формула изобретения 1. Устройство для формирования опорного сигнала, содержащее US -триггер. 838

динен со вторым входом элемента И.

2.Устройство по п. I, о т л и чающееся тем, что блок сравнени выполнен в виде вычитающего счетчика, установочные входы которого соединены

с коммутатором, а разрядные выходы подключены к дешифратору.

3.Устройство по п. 1, о т л и ч а ю щ е е с я тем, что времязадающее устройство выполнено в виде кольцевых регистров сдвига с объединенными тактовыми входами.

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР

№ 483756, кл. Н О2 Р 13/16, 1975.

2.Авторское свидетельство СССР

№ 481113, кл. Н 02 Р 13/16, 1975. 56 S -вход которого соединен с вхЫШой шиной, генератор такговой частоты и связанные с блоком сравнения элемент задержки и времяза дающий блок, отличающееся тем, что, с целью nt вышения точности, оно снабжено элементом И, вычитающим счетчиком и счетчиком циклов, причем прямой выход tJS триггера соединен через элемент И с тактовым входом блока сравнения, выход которого соединен со счетным входом вычитающего счетчика и с входом врем задаюшего блока, входная шина соединена с установочным входом вычитающего счегчика, а генератор тактовой частоты сое

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для анализа логических состояний | 1980 |

|

SU1096648A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| УСТРОЙСТВО АВТОМАТИЧЕСКОГО ПОИСКА КАНАЛОВ РАДИОСВЯЗИ | 2011 |

|

RU2450447C1 |

| Преобразователь параллельного кода в число-импульсный код | 1981 |

|

SU1027714A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| ФУНКЦИОНАЛЬНЫЙ ПРЕОБРАЗОВАТЕЛЬ АНАЛОГ - КОД | 1991 |

|

RU2027303C1 |

| УСТРОЙСТВО ДЛЯ СИГНАЛИЗАЦИИ ОТКЛОНЕНИЙ ПАРАМЕТРОВ ПРИ ДОПУСКОВОМ КОНТРОЛЕ | 2016 |

|

RU2617982C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С КАНАЛОМ СВЯЗИ | 1992 |

|

RU2043652C1 |

| Устройство для функционального контроля цифровых блоков | 1989 |

|

SU1656538A1 |

| Устройство для централизованного контроля параметров | 1989 |

|

SU1644092A1 |

Авторы

Даты

1981-06-15—Публикация

1979-09-26—Подача