Изобретение относится к цифровой авто/латике и контрольно-измерительной технике и предназначено для циклического преобразования параллель но кода в ЧИСЛО-ИМПУЛЬСНЫЙ код и временной интервал. Известен преобразователь параллельного двоичного кода в число-импульсный код, содержащий регистр, счетчик, параллельные входы которого соединены с входными шинами, входами регистра и входами элемента ИЛИ выход которого соединен с входом элемента задержки, первый выход которого соединен с первым входом первого элемента И, выход которого соединен с одним из входов элемента ИЛИ и выходной шиной, выход элемента ИЛИ соединен с нулевым входом триггера, и второй элемент И 1. Недостаками данного преобразовате ля являются его сложность и невозмож ность циклического преобразования параллельного кода в число-импульсный код. Наиболее близким к предлагаемому по технической сущности и схемному построению является преобразователь параллельного кода в число-импульсны код, содержащий вычитающий счетчик входы которого соединены с входами элемента ИЛИ, параллельными входами преобразователя и входами регистра,, выходы - с входами дешифратора нуля, а выход вычитания - с одним из входо .элемента ИЛИ, выходом преобразователя и выходом элемента И первый вход которого соединен с выходом триггера вход которого соединен с выходом дешифратора нуля, а вход.- с выходом элемента ИЛИ и входом элемента задержки, первый выход которого соединен с дополнительным входом дешифг ратора нуля, а второй выход - с вторым входом элемента И 2. Недостаток, известного преобразователя состоит в том, что он не позволяет осуществлять циклическое преобразование параллельного кода в число-импульсной код, а также формирование циклических временных интервалов. Цель изобретения - расширение области применения преобразователи путем циклического повторения преоб разования и автоматического изменения частоты тактовых импульсов. Поставленная цель достигается тем, что в преобразователь параллель . ного кода в число-импульсный код, содержащий регистр, вычитающий счет- чик, генератор импульсов, дешифратор нуля, первьай триггер, первый эле мент ИЛИ, первый элемелт И, первый вход которого соединен с единичным выходом триггера, являющимся потенци альным выходом преобразователя, информационные входы которого соединены с входами регистра, выходы которого соединены с информационными входами ззычйтающего счетчика, выходы которого являются разрядными выходами преобразователя и соединены с входа1 да дешифратора нуля., выход которого соединен с первым входом первого элемента ИЛИ, выход которого соединен с .управляющим.входом вычитающего счетчика и R-входом первого триггера, введены, времязадающий блок, второй триггер, второй и третий элементы. ИЛИ и элемент запрета, выход которого соединен с ё-входом первого триггера, заприцающий вход соединен с выходом дешифратора нуля, а разрешающий вход элемента запрета соединен с.выходом второго элемента ИЛИ, первый вход которого.соединение Sвходом второго триггера и является входом пуска преобразователя, второй вход.второго .элемента ИЛИ соединен с информационным выходом времязадающего блока,.тактовый вход которого соединен с выходом генератора импульсов и вторым входом первого элемента И, трети.й вход . которого явл ляется управляющим входом преобразователя и.соединен с управлякадим входом времязадающего блока, тактовый выход которого соединен с третьим входом ВТорого элемента ИЛИ и первым входом третьего элемента ИЛИ, второй вход которого соединен с выходом первого элемента И, а выход соединен с тактовым входом вычитающего счетчигjca и является .тактовым выходом преобразователя, столовый выход которого соединен с R-входом второго триггера, единичный выход.которого.соединен с входом.блокировки.времязадающего блока, а нулевой выход второго триггера соединен с вторым входом первого элемента ИЛИ. .1 Кроме того, времязадающий блок содержит счетчик, два элемента И, два элемента НЕ и элемент ИЛИ, первый и второй входы которого соединены соответственно с выходами первого и второго элементов И, являющимися тактовым и информационным выходами времязадающего блока соответственно, третий вход элемента ИЛИ соединён с выходом первого инвертора, вход которого является входом блокировки времязадающего блока, а выход . элемента ИЛИ соединен с R-входом счетчика, тактовый вход которого являегся тактовым входом времязадакадего блока, управляющий входкоторого соединен с входом второго.элемента НЕ, первые входы первого и второго элементов И соединены соответственно с входом и выходом второfo элемента НЕ, а остальные входы первого и второго элемента И соединены с выходами счетчика.

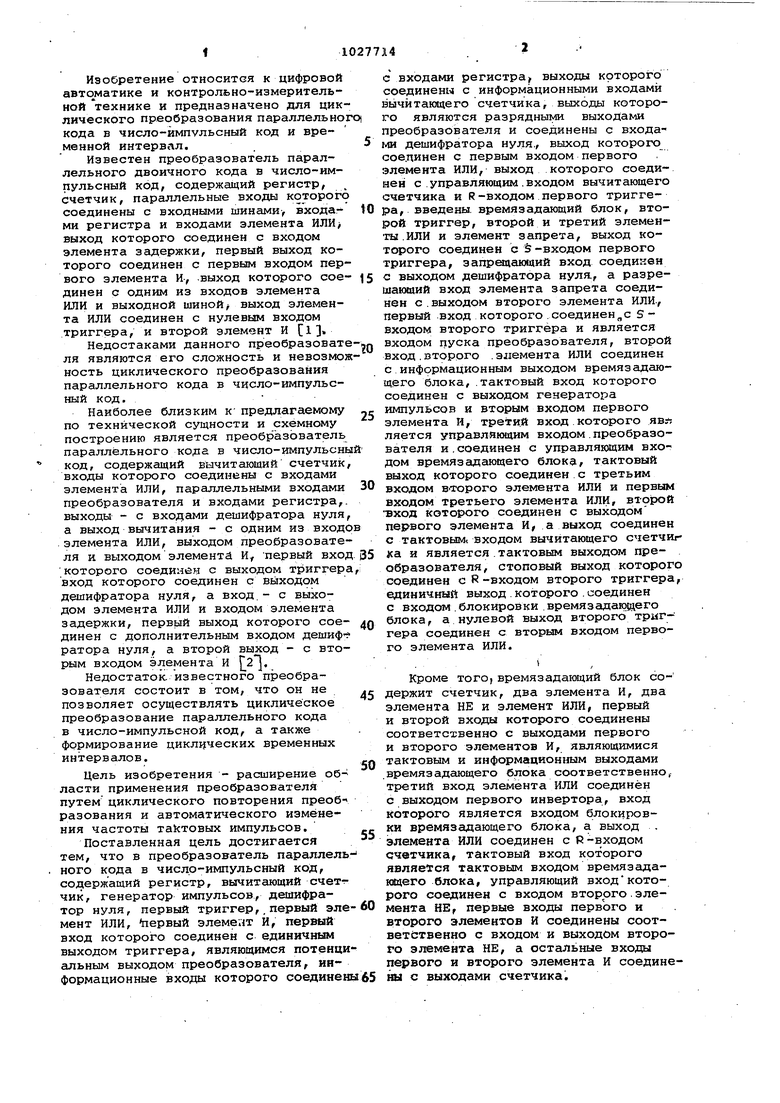

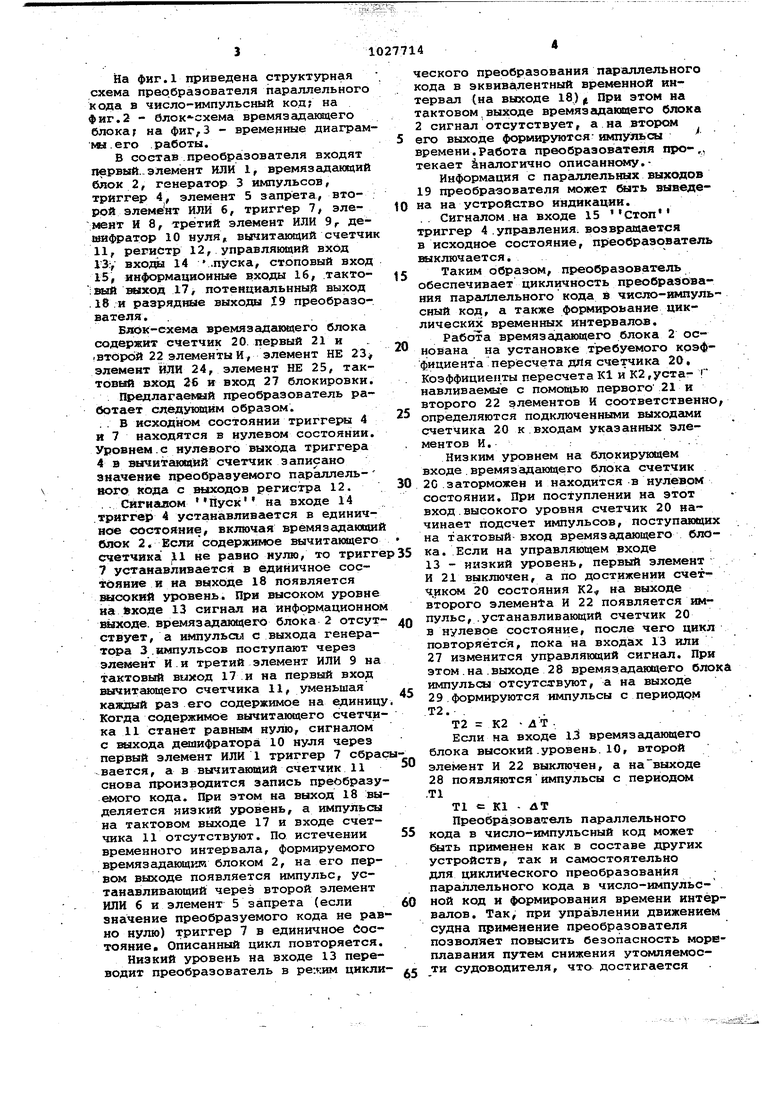

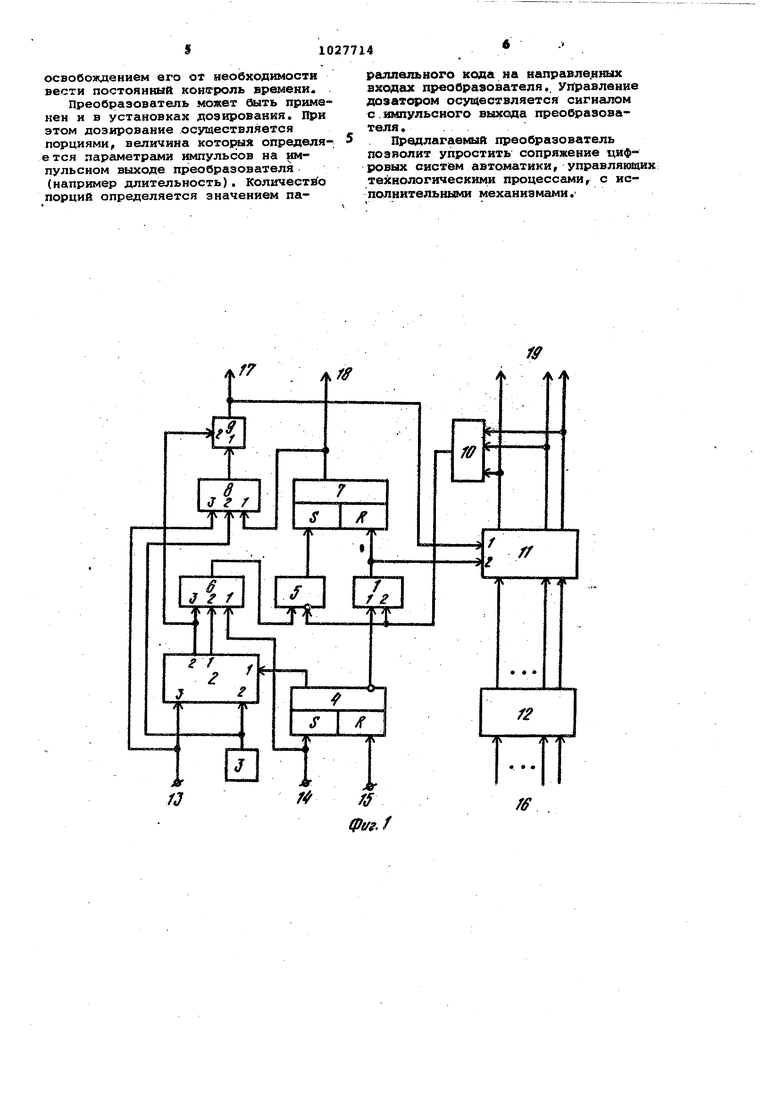

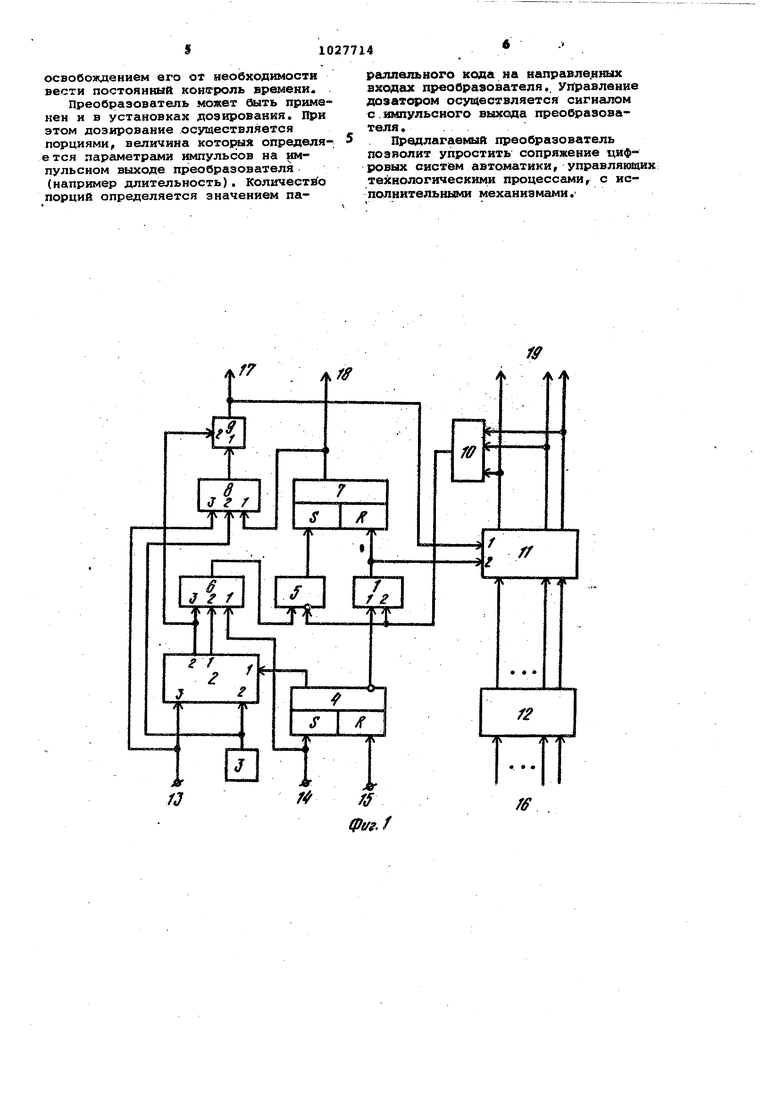

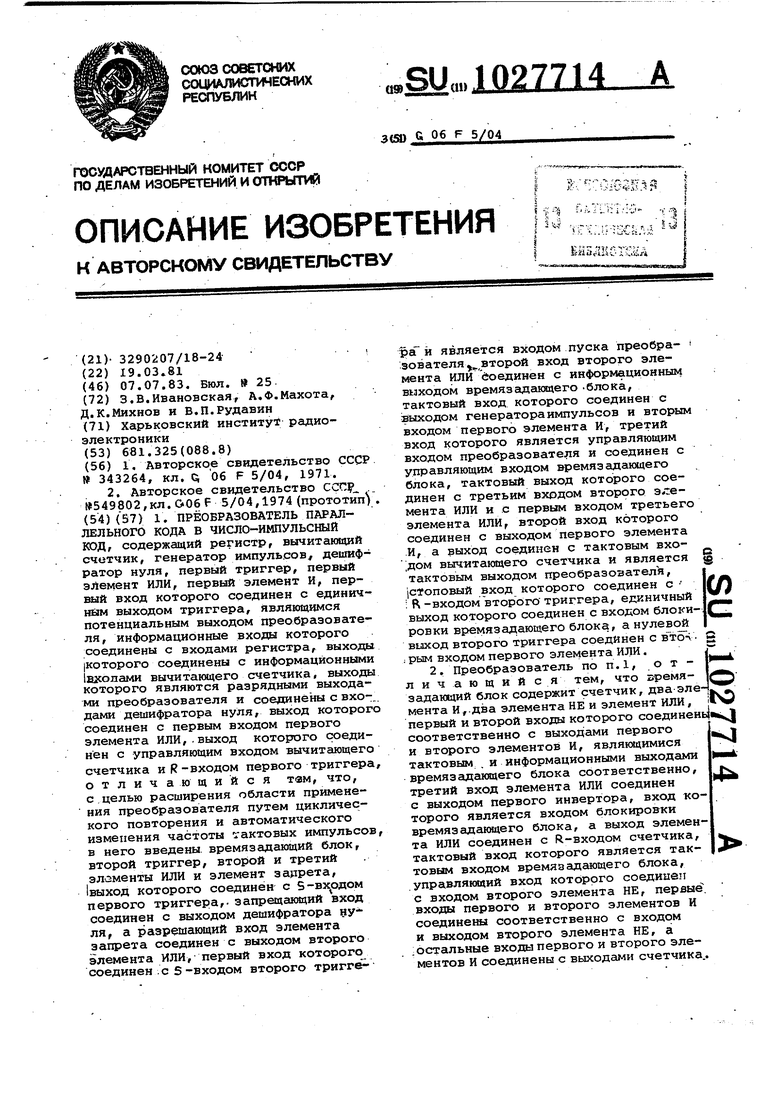

На фиг.1 приведена структурная схема преобразователя параллельного кода в число-импульсный код; на фиг.2 - блок -схема времяэадакнцего блока; на - временные диаграммы, его работы.

В состав преобразователя входят первый., элемент ИЛИ 1, время задающий блок 2, генератор 3 импульсов, триггер 4, элемент 5 запрета, второй элемент ИЛИ 6, триггер 7/ элемент И 8, третий элемент ИЛИ 9г дешифратор 10 нуля, вычитающий счетчик 11, регистр 12, управляющий вход 13.-, входа 14 .пуска, стоповый вход 15, информационные входщ 16, такто;вый выход 17, потенциальнный выход .18 и разрядные выходы J9 преобразователя.

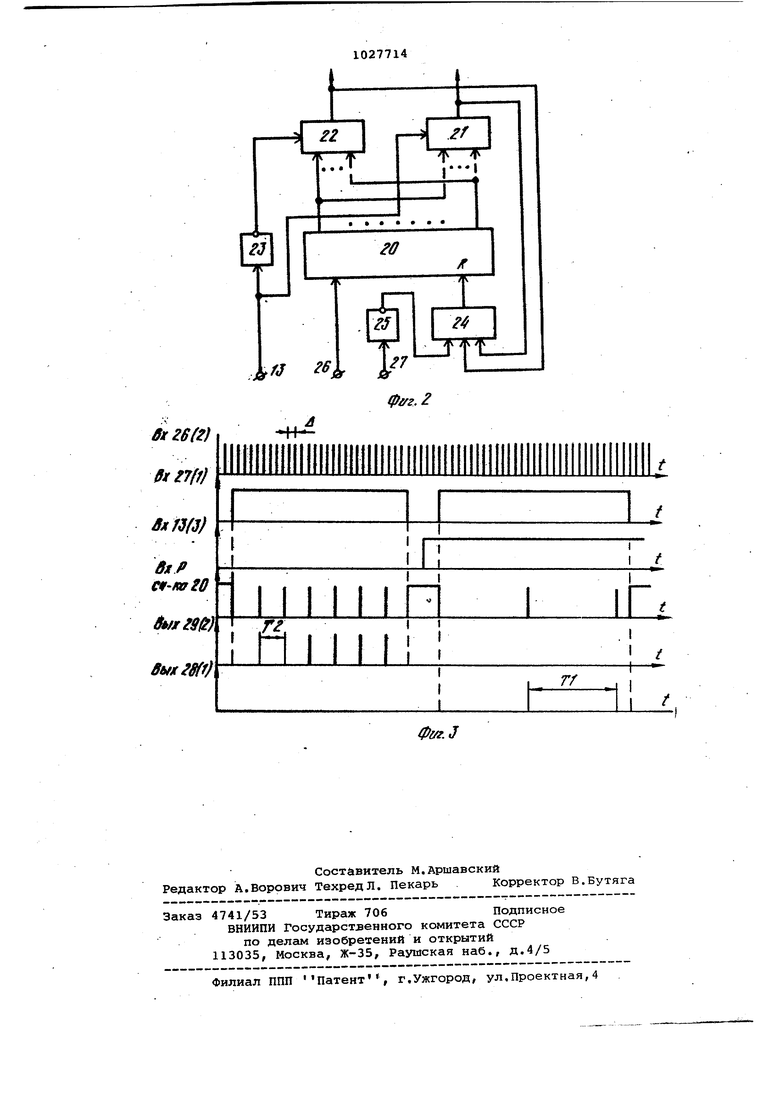

Блок-схема времязадающего блока содержит счетчик 20. первый 21 и .вторсий 22 элементы И, элемент НЕ 23 элемент ИЛИ 24, элемент НЕ 25, тактовый вход 26 и вход 27 блокировки.

Предлагаемый преобразователь работает следующим образом. .. В исходном состоянии триггеры 4 и 7 находятся в нулевом состоянии. Уровнем.с нулевого выхода триггера 4 в вычитающий счетчик записано значение преобразуемого параллельвого кода с выходов регистра 12. ..Сигналом Пуск на входе 14 .триггер 4 устанавливается в единичное состояние, включая времязадаюсдщ блок 2. Если содержимое вычитающего счетчика ,11 не равно нулю, то тригг 7 устанавливается в единичное сос йяние и на выходе 18 появляется высокий уровень. При высоком уровне на бходе 13 сигнал на инфс мационно выходе, времяэадающего блока 2 отсутствует, а импульсы с выхода генератора 3.импульсов поступают через элемент И.и третий элемент ИЛИ 9 на тактовый выход 17:и на первый вход вычитающего счетчика 11, уменьшая каждый раз его содержимое на единиц Когда содержимое вычгстгиощего счетчика 11 станет равным нулю, сигналом с выхода дешифратора 10 нуля через первый элемент ИЛИ 1 триггер 7 сбра вается, а в вычитающий счетчик 11 снова производится запись преобразуемого кода. При этом на выход 18 выделяется низкий уровень, а импульсы на тактовом выходе 17 и входе счетчика 11 отсутствуют. По истечении временного интервала, формируемого времязадакнцкк блоком 2, на его первом выходе появляется импульс, устанавливающий через второй элемент ИЛИ 6 и элемент 5 запрета (если значение преобразуемого кода не равно нулю) триггер 7 в единичное Состояние, Описанный цикл повторяется.

Низкий уровень на входе 13 переводит преобразователь в режим циклического преобразования параллельного кода в эквивалентный временной интервал (на выходе 18) При этом на тактовом выходе времяз гщающего блока 2 сигнал отсутствует, а на втором

. его выходе формируются импульсы времени.Работа преобразователя про-,, текает Аналогично описаннс «у.Информация с параллельных выходов

19преобразователя может быть выведена на устройство индикации.

0

.. Сигналом.на входе 15 Стоп триггер 4.управления, возвращается в исходное состояние, пр еобразователь выключается.

Таким образом, преобразователь

5 обеспечивает цикличность преобразования параллельного кода в число-импульсный код, а также формирование циклических временгагх интервалов.

Работа времязадающего блока 2 ос0нована на установке требуемого коэффициента пересчета для счетчика 20, Коэффициенты пересчета К1 и К2,уста- Г навливаемые с псмощью первого 21 и второго 22 элементов И соответственно,

5 определяются подключенными выход гики счетчика 20 к входам указанных элементов И..

Низким уровнем на блокирующем входе.времязадающего блока счетчик

0

20заторможен и находится в нулевом состоянии. При поступлении на этот вход.высокого уровня счетчик 20 начинает подсчет импульсов, поступающих на тактовый вход времязадающего бло5ка. Если на управляющем входе

13 - низкий уровень, первый элемент И 21 выключен, а по достижении счет4jiKc i 20 состояния К2, на выходе второго 3neMeHta И 22 появляется импульс, .устанавливающий счетчик 20

0 в нулевое состояние, после чего цикл повторяется, пока на входах 13 или

27изменится управляющий сигнал. При этом.на.выходе 28 времязадающего блока импульсы отсутствуют, а на выходе

5

29.формируются импульсы с периодом .Т2.- . .. .

Т2 К2 Д-Т ,

Если на входе IJS времязадающего блока высокий.уровень.10, второй

0 элемент И 22 выключен, а навыходе

28появляются юшульсы с периодсш .Т1

Т1 с К1 - ЛТ

Преобразователь параллельного

5 кода в число-импульсный код может быть применен как в составе других устройств, так и самостоятельно для циклического преобразования параллельного кода в число-импульс0ной код и формирования времени интервалов. Так, при управлении движением судна применение преобразователя позволяет повысить безопасность мореплавания путем снижения утсялляемости судоводителя, что достигается

5

освобождением его of необходимости вести постоянный контроль времени.

Преобразователь может аать приманен и в установках дозирования. При этом дозирование осуществляется порциями, величина которм определяется паргииетрами импульсов на импульсном выходе преобразователя (например длительность). Количество порций определяется значением параллельного кода на направле,ншлх входах преобразователя,, Уп:равлвние дозатором осуществляется сигналом с.импульсного выхода преобразователя. .

Предлагаемый преобразователь позволит упростить сопряжение цифровых CHCTiBM автоматики, управляющ технологическими процессами, с испапнительными механизмами.

| название | год | авторы | номер документа |

|---|---|---|---|

| Многоканальный преобразователь последовательного кода в параллельный | 1990 |

|

SU1751859A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1978 |

|

SU742923A1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Преобразователь двоичного кода в числоимпульсный код | 1986 |

|

SU1383513A1 |

| Устройство для нормализации кодов Фибоначчи | 1980 |

|

SU951291A1 |

| Преобразователь код-временной интервал | 1986 |

|

SU1401589A1 |

| Преобразователь последовательного двоичного кода в параллельный двоично-десятичный код | 1982 |

|

SU1084780A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1981 |

|

SU993244A1 |

| Формирователь кодов | 1985 |

|

SU1264316A1 |

| Декодер сверточного кода (его варианты) | 1985 |

|

SU1320875A1 |

CptfgJ

фуг,3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПАРАЛЛЕЛЬНОГО ДВОИЧНОГО КОДА В ЧИСЛО-ИМПУЛЬСНЫЙ КОД | 0 |

|

SU343264A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Разборный с внутренней печью кипятильник | 1922 |

|

SU9A1 |

Авторы

Даты

1983-07-07—Публикация

1981-03-19—Подача