1

Изобретение относится к вычислительной технике и может быть исполь зовано в системах для ввода информации от дискретных датчиков.

Известно устройство для ввода информации от дискретных датчиков, содержа1цее блок памяти, адресный блок, регистры, ко утаторы, генераторы импульсов и решаницее задачу опроса датчиков и ввода в ЭШ1 адреса датчика, состояние которого изменилось 1..

Недостатком устройства является его сложность.

Наиболее близким по технической сущности к предлагаемому является устройство для ввода информации от дискретных датчиков, содержащее блок управления, генератор импульсо датчики, распределитель, блок памяти, состоящий из- буферных регистров блок формирования адреса с шифраторами и элемент ИЛИ 2. .

В известном устройстве с помощью распределителя производится последовательный опрос всех датчиков как изменяющих, так и неизменяющих свое состояние, причем информация на выходе устройства формируется только для датчиков, изменивших свое состояние. При этом увеличивается время, необходимое для выборки датчиков с измененным состоянием, и снижается быстродействие устройства.

Цель изобретения - повышение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для ввода информации, содержащее датчики, блок

0 памяти, блок формирования адреса, шифратор и генератор импульсов, введены первый и второй регистры, распределитель, импульсов запроса, элементы задержки, коммутатор и блок

s сравнения, причем выходы датчиков подключены к первым входам первого регистра, выходь) которого соединены со входами распределителя импуль-. сов. запроса, выходы которого соеди0нены со входами элементов задержки, выходы элементов задержки соединены со входами шифратора и первыми входгши KOhttiyTaTOpa, выходы ке 1мутатора соединены со вторыми входами

5 первого регистра, а выход шифратора соединен с первым входом блока формирования адреса, выход которого соединен со входом блока памяти и первым входом блока сравнения, второй выход блока памяти соединен с

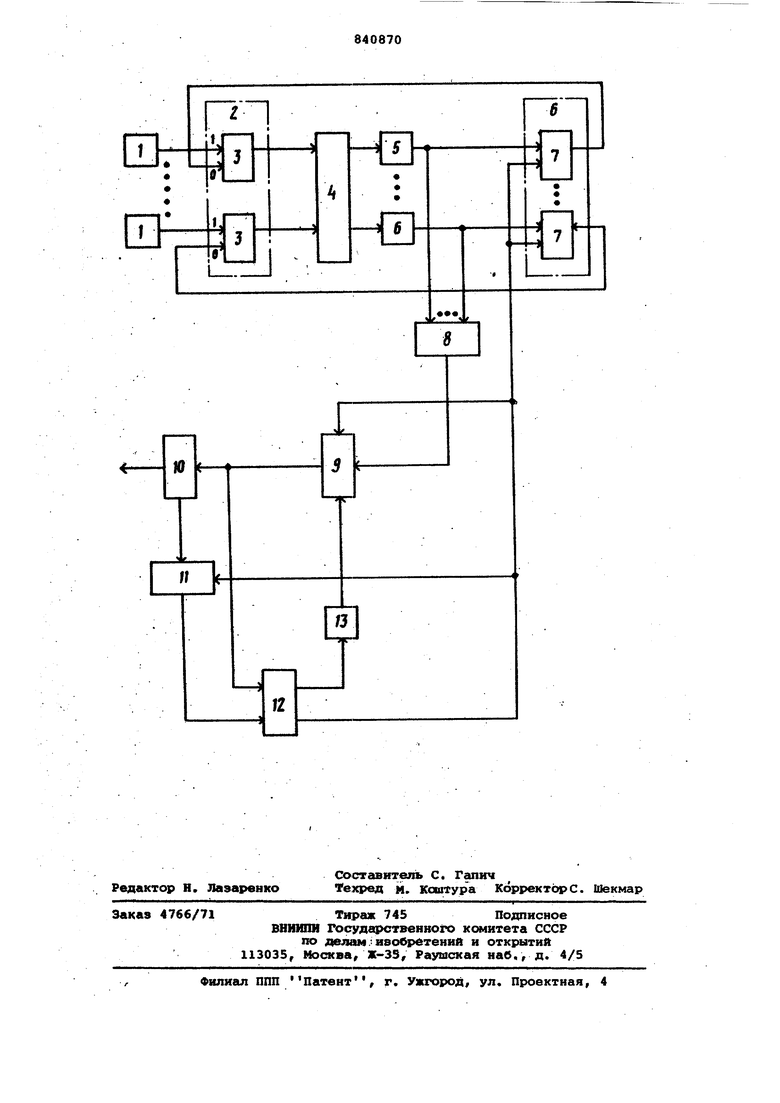

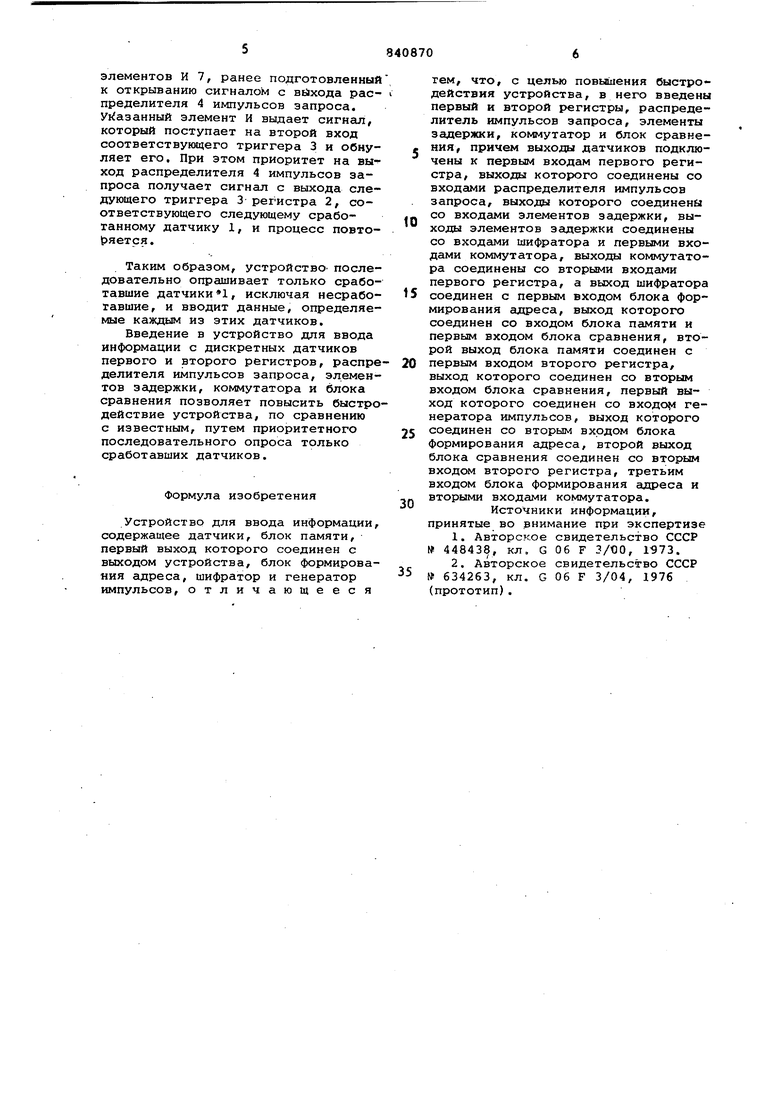

0 первым входом второго регистра, выход которого соединен со вторым входом блока срав«ения, первый выход которого соединен со входом ген ратора импульсов, выход которого соединен со вторым входом блока формирования адреса, второй выход блока сравнения соединен со вторым входом второго регистра, третьим входом блока формирования адреса и вторыми входами коммутатора. -На чертеже изображена схема устройства. Устройство содержит датчики 1, первый регистр 2 с разрядными триггерами 3, распределитель 4 импульсов запроса, элементы 5 задержки, коммутатор б с элементами И 7, шифратор 8, блок 9 формирования адреса блок 10 памяти, второй регистр 11, блок 12 сравнения и генератор 13 импульсов. Выходы датчиков 1 подклю чены к первым входам триггеров 3 первого регистра 2. Выходы триггеро 3 соединены с входами распределителя 4 импульсов запроса, выходы которого через элементы 5 задержки св заны с первыми входами элементов И 7 коммутатора бис входами шифратора 8. Выходы элементов И 7 подключены ко вторым входам соответствующих триггеров 3 регистра 2, Вьлходы шифратора 8 соединены с первыми установочными входами блока 9 формирования адреса, выходы которого связаны с входами блока 10 памяти и первыми входами блока 12 сравнения. Выходы блока памяти подключены к первым входам второго регистра 11, выходы которого соединены со вторыми входами блока 12 сравнения. Первый выход несовпадения блока 12 сравнения подключен к входу гене ратора 13 импульсов, выход которого соединен со вторым счетным входом блока 9. Второй выход совпадения блока 12 сравнения соединен со вто рыми управляющими входами элементов И 7 коммутатора б и входами установ в нулевое положение блока 9 формиро вания адреса и второго регистра II Распределитель 4 импульсов запро са представляет собой логическое статическое устройство, обеспечива ющее на своих выходах приоритетное распределение входных сигналов, например, каждый входной сигнал на предыдущем входе имеет приоритет прохождения на выход по отношению к сигналам на; всех последующих входах. Таким образом, распределит импульсов запроса 4 формирует выхо ной сигнал только на одном выходе, ответствующем входу с большим приоритетом. Элементы 5 задержки обес печивают синхронность работы всех элементов устройства. Каждому из датчиков 1 в блоке 10 памяти сответствует область памяти, которая определяется начальным и конечным адресами соответствукнцих ячеек блока памяти и в которую предварительно записывается соответствующая информация. Устройство работает следующим образом. При вызове информации соответствующие датчики 1 срабатывают и формируют импульсные сигналы, которые поступают на первые входы триггеров 3 регистра 2 и устанавливают их в единичные состояния. С выходов сработанных триггеров сигналы подаются на входы распределителя 4 импульсов запроса, который формирует сигнал только на одном своем выходе, соответствующем сработавшему датчику 1 большого приоритета (по входу), Указанный сигнал с выхода распределителя 4 импульсов запроса через элемент 5 задержки подается на первый вход соответствующего элемента И 7 коммутатора б и подготавливает его к срабатыванию. Кроме того, указанный сигнал возбуждает соответствующий вход шифратора 8, на выходе которого формируется код начального адреса области памяти, соответствующий опрашиваемому датчику 1. Код начального адреса заносится в блок 9 формирования адреса, откуда поступает в режиме чтения информации на адресные входы блока 10 памяти. По указанному адресу из блока 10 памяти выбирается код конечного адреса области памяти , соответствующий первому опрашиваемому датчику 1, и заносится во второй регистр 11. С выходов второго регистра 11 указанный код подается на вторые входы блока 12 сравнения,на первые входы которого поступает код с выходов блока 9 формирования адреса. Так как коды на входах блока сравнения не совпадают, блок 12, сравнения сигналом несовпадения запускает генератор 13 импульсов. Последний выдает импульсы на второй счетный вход блока 9 формирования адреса, который последовательно изменяет значения адресов ячеек памяти и обеспечивает выборку информации из соответствующей области памяти блока 10. По окончании выборки информации адрес конечной ячейки области памяти на выходе блока 9 формирования адреса совпадает со значением адреса, зафиксированным во втором регистре 11. этом блок 12 сравнения вырабатывает сигнал совпгщения, отключает генератор 13 импульсов, обнуляет адресный блок 9 формирования адреса и регистр 11 и подает сигнал совпадения на вторые входщ. элементов И 7 коммутатора 6. Этим сигнсшЬм открывается один из элементов И 7, ранее подготовленный к открыванию сигналом с вйхода распределителя 4 импульсов запроса. Указанный элемент И выдает сигнал, который поступает на второй вход соответствующего триггера 3 и обнуляет его. При этом приоритет на вы ход распределителя 4 импульсов запроса получает сигнал с выхода следующего триггера 3 регистра 2, соответствующего следующему сработанному датчику 1, и процесс повто гяется. Таким образом, устройство последовательно опрашивает только сработавшие датчики, исключая несрабогавшие, и вводит данные, определяемые каждым из этих датчиков. Введение в устройство для ввода информации с дискретных датчиков первого и второго регистров, распре делителя импульсов запроса, элементов задержки, коммутатора и блока сравнения позволяет повысить быстро действие устройства, по сравнению с известным, путем приоритетного последовательного опроса только сработавших датчиков. Формула изобретения Устройство для ввода информации, содержащее датчики, блок памяти, первый выход которого соединен с выходом устройства, блок формирования адреса, шифратор и генератор импульсов, отличающееся тем, что, с целью повышения быстродействия устройства, в него введены первый и второй регистры, распределитель импульсов запроса, элементы задержки, коммутатор и блок сравнения, причем выходы датчиков подключены к первым входам первого регистра, выходы которого соединены со входс1ми распределителя импульсов запроса, выходы которого соединены со входами элементов задержки, выходы элементов задержки соединены со входами шифратора и первыми входами коммутатора, выходы коммутатора соединены со вторыми входг1ми первого регистра, а выход шифратора соединен с первым входом блока формирования адреса, выход которого соединен со входом блока памяти и первым входом блока сравнения, второй выход блока памяти соединен с первым входом второго регистра, выход которого соединен со вторым входом блока сравнения, первый выход которого соединен со входо генератора импульсов, выход которого соединен со вторым входом блока формирования адреса, второй выход блока сравнения соединен со вторым входом второго регистра, третьим входом блока формирования адреса и вторыми входами коммутатора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 448438, кл. G 06 F 3/00, 1973. 2.Авторское свидетельство СССР 634263, кл. G 06 F 3/04, 1976 (прототип).

пп

tr-I

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для ввода информации от датчиков | 1983 |

|

SU1149241A1 |

| Устройство для ввода информации | 1986 |

|

SU1424000A1 |

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Система коммутации | 1985 |

|

SU1317448A1 |

| Устройство для обмена данными | 1985 |

|

SU1297067A1 |

| Устройство для организации очередности приема информации | 1983 |

|

SU1128255A1 |

| Устройство для сопряжения абонентов с ЭВМ | 1986 |

|

SU1410041A1 |

| УСТРОЙСТВО ДЛЯ ПРИЕМА ИНФОРМАЦИИ | 1991 |

|

RU2018970C1 |

| Устройство для сопряжения | 1982 |

|

SU1112359A1 |

-9

tu

:Щ

Авторы

Даты

1981-06-23—Публикация

1979-06-15—Подача