Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля дискретных устройств, работающих с информацией, представленной в виде кодовых комбинаций.

Известно устройство для тестового контроля, содержащее запоминающий блок хранения тестов, блок записи .информации, регистр, коммутато блок управления и блок сравнения ClНедостаток данного устройства за.лючаётся в невозможности формирования различных последовательностей тестов и обусловлен постоянным заданием одного тестового набора в блоке памяти и в постоянной неизменяемой связи блока управления и коммутатора, соединяющего контролируемые цепи с тестовым регистром, что ограничивает возможность использования устройства для проверки различных типов объектов.

Наиболее близким к предлагаемому является устройство для контроля логических блоков, содержащее генератор импульсов, регистр, счетчик, блок сравнения, элементы И и задатчик тестов С2 1.

Недостатком данного устройства является, то, что оно не позволяет изменять последовательность комбинаций в тесте и использовать эти комбинации в различных сочетаниях, т,а, не обеспечивает формирование последовательности различных тестовых наборов. Такие различные последовательности тестов и их комбина ции необходимы при поиске неисправностей, когда их локализация проводится по все более сужающейся области и каждая проверка по данному тесту ограничивает область, в кото-рой проводится следующая проверка. . Таким образом, недостаток известног устройства заключается в ограниченности его функциональных возможноедля локализации неисправностей в проверяемом объекте.

Цель изобретения - расширение функциональных возможностей устройсва путем формирования различных тестовых последовательностей.

Поставленная цель достигается тем, что в устройство для задания тестов, содержащеегенератор импульсов, счетчик, первый элемент И, элемент задержки, регистр и задатчик тестов, причем выход генератора импульсов соединен с первь1М входом первого элемента И,выход которого соединен с входом элемента задержки и с входом обнуления счетчика, введены блок приоритета, блок задержки включения, группа элементов И, шифратор, блок памяти, триггер, второй элемент И, элемент ИЛИ, причем выходы эадатчика тестов соедине ны с единичными входами соответствующих разрядов регистра, единичные выходы которого соединены с входами блока приоритета, выходы блока приоритета через блок задержки включения соединены с первыми входами соответствующих элементов И группы и соответствующими входами шифратора, выходы которого соединены с

0 установочными входами счетчи ка, информационные выходы счетчика соединены с адресньлми входами блока памяти и с входами элеме.нта ИЛИ, выход которого соединен с входом

5 разрешения генератора импульсов, выход генератора импульсов соединен с первым входом второго элемента И, выход которого соединен с входом чтения блока памяти, первый и второй управляющие выходы блока памяти соединены соответственно со счетным входом счетчика и с единичным входом триггера, группа информационных выходов блока памяти является группой информационных выходов устройства, выход элемента задержки соединен с нулевым входом триггера, нулевой и единичный выходы которого соединены соответственно с вторыми входами второго и первого элементов И, выход первого элемента И соединен с вторыми входами элементов И группы, выходы которых соединены с нулевыми входами соответствующих разрядов, регистра.

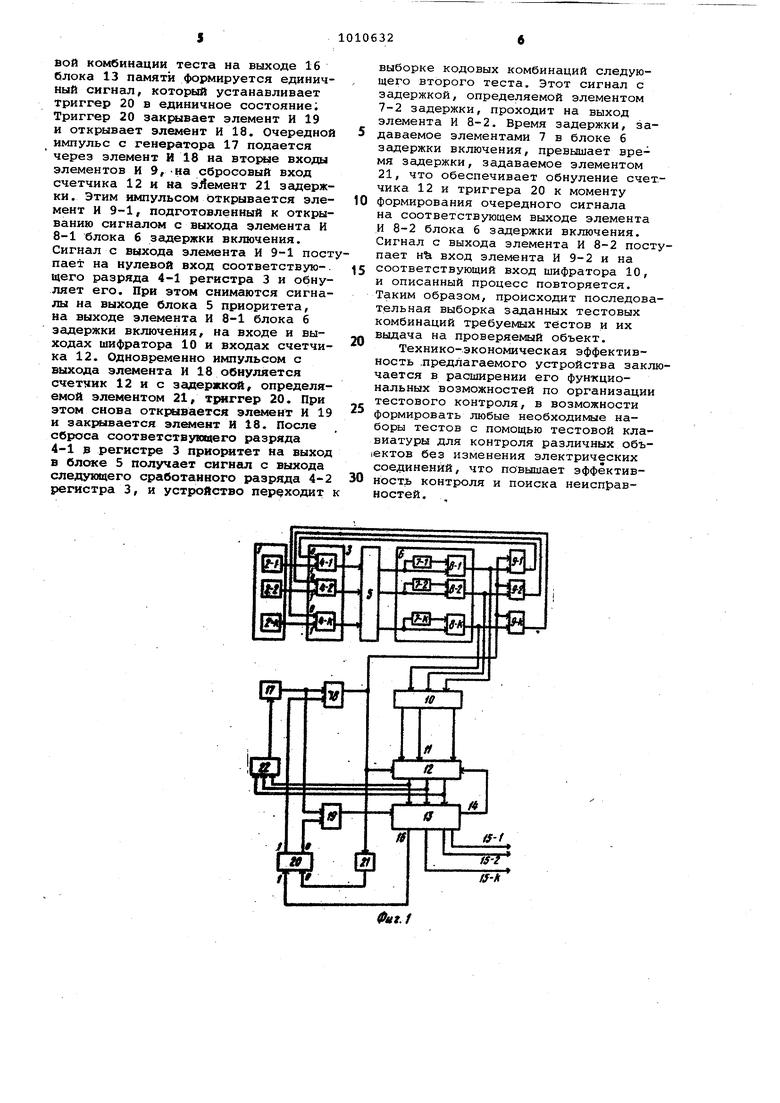

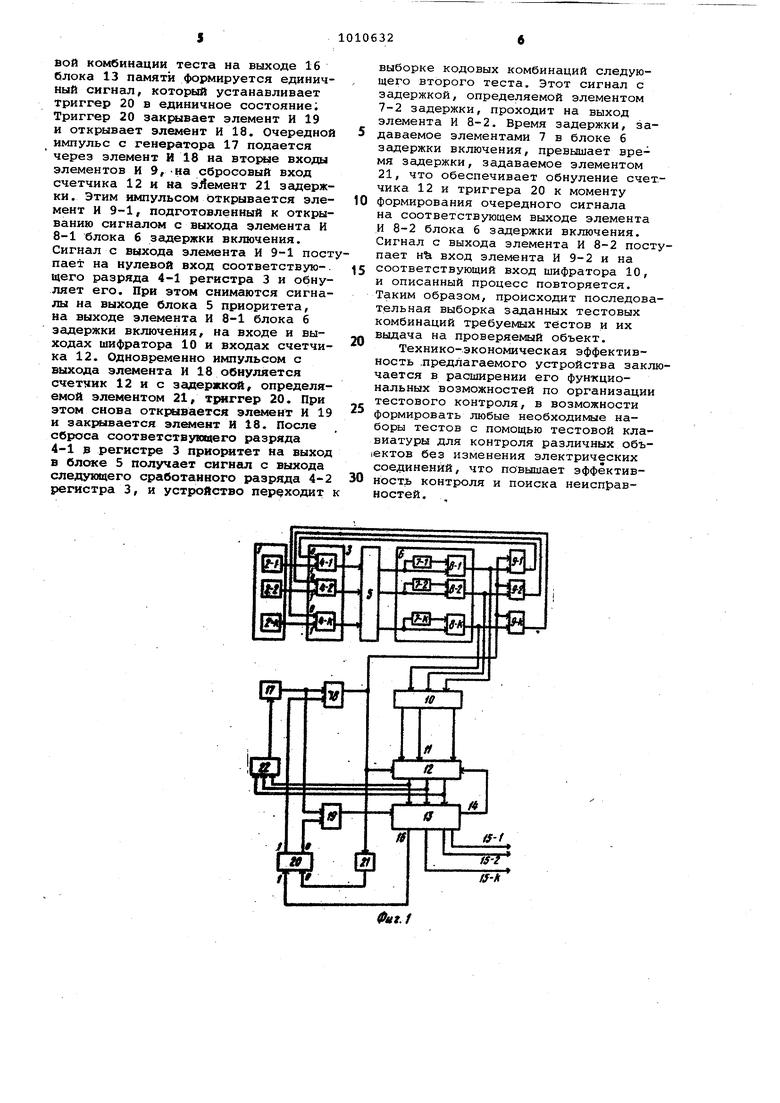

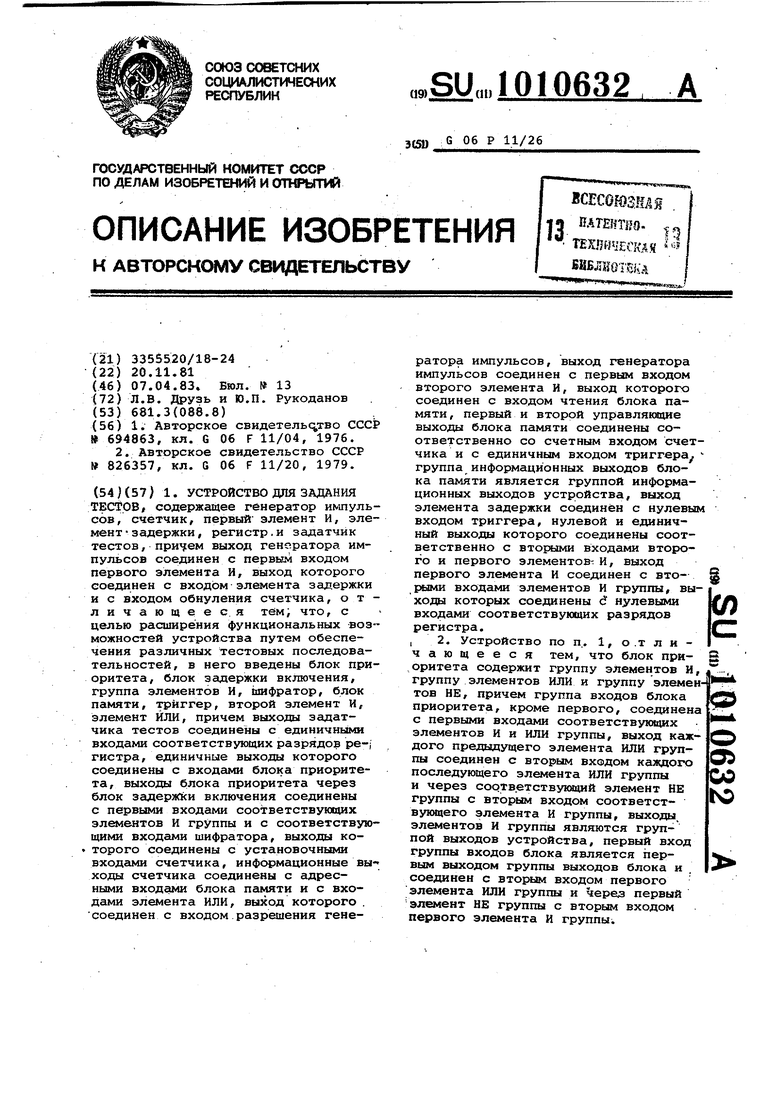

5 Кроме того, поставленная цель достигается тем, что блок приоритета содержит группу элементов И, группу элементов ИЛИ и группу элементов НЕ, причем группа входов блока прид оритета, кроме первого, соединена с первыми входами соответствующих элементов И и ИЛИ группы, выход каждого предыдущего элемента ИЛИ группы соединен с вторым входом каждого последующего элемента ИЛИ группы и через соответствующий элемент НЕ группы с вторым входом соответствующего элемента И группы, выходы элементов И группы являются группой выходов устройства, первый

0 вход группы входов блока является первым выходом группы выходов блока и соединен с вторым входом первого элемента ИЛИ группы и через первый элемент НЕ группы с вторым входом

5 первого элемента И группы.

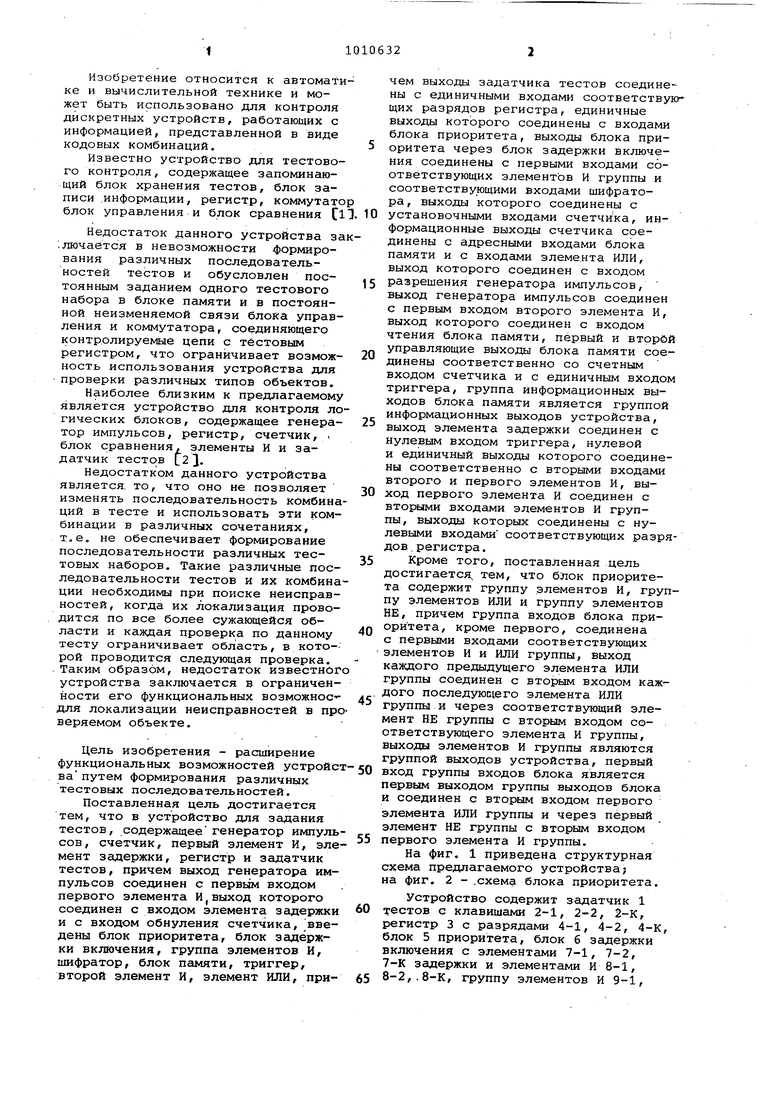

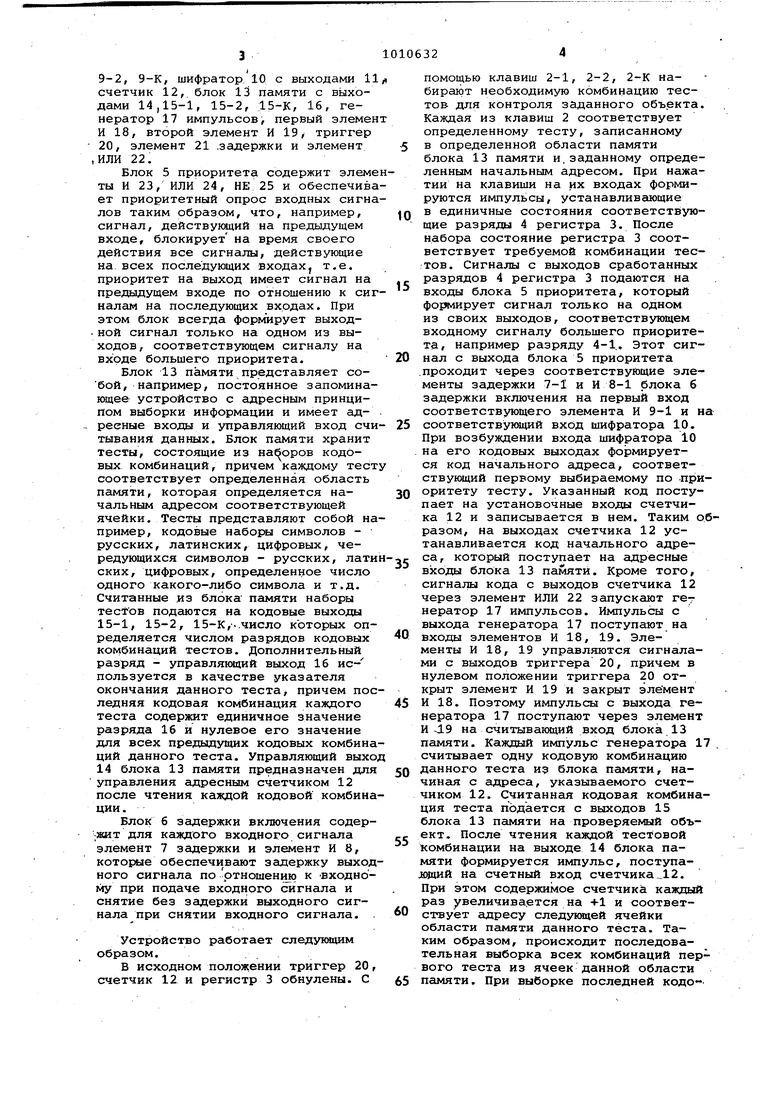

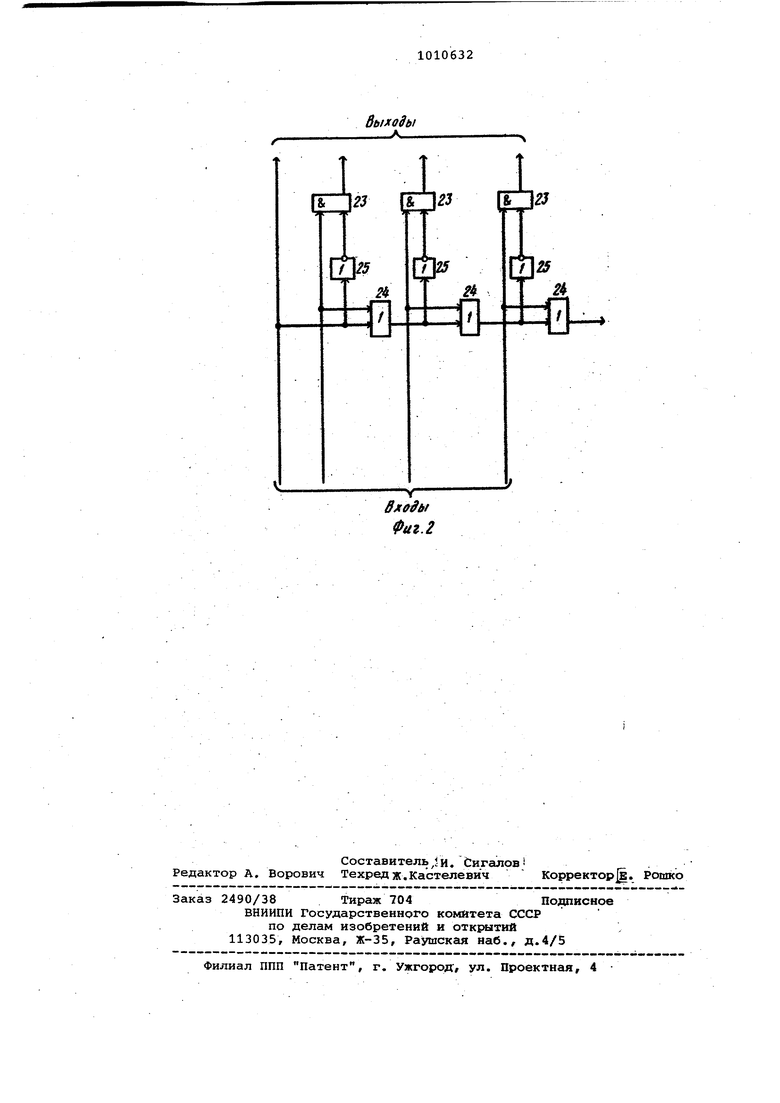

На фиг. 1 приведена структурная схема предлагаемого устройства; на фиг. 2 - .схема блока приоритета.

Устройство содержит задатчик 1 0 тестов с клавишами 2-1, 2-2, 2-К,

регистр 3 с разрядами 4-1, 4-2, 4-к, блок 5 приоритета, блок 6 задержки включения с элементами 7-1, 7-2, 7-К задержки и элементами И 8-1, 5 8-2,.8-К, группу элементов И 9-1, 9-2, 9-К, шифратор 10 с выходами 1 счетчик 12,, блок 13 памяти с выходами 14,15-1, 15-2, 15-К, 16, генератор 17 импульсов, первый элеме И 18, второй элемент И 19/ триггер 20, элемент 21 .задержки и элемент ,ИЛИ 22. Блок 5 приоритета содержит элем ты И 23, ИЛИ 24, НЕ 25 и о&еспечив ет приоритетный опрос входных сигн лов таким образом, что, например, сигнал, действукмций на предыдущем входе, блокирует на время своего действия все сигналы, действунвдие на всех последующих входах, т.е. приоритет на выход имеет сигнал на предыдущем входе по отношению к си налам на последующих входах. При этом блок всегда формирует выход.ной сигнал только на одном из выходов, соответствующем сигналу на входе большего приоритета. Блок 13 памяти представляет собой, например, постоянное запомина ющее устройство с адресным принципом выборки информации и имеет ад-рееные входы и управляющий вход сч тывания данных. Блок памяти хранит тесты, состоящие из наборов кодовых комбинаций, причем каждому тес соответствует определенная область памяти, которая определяется начальным адресом соответствующей ячейки. Тесты представляют собой н пример, кодовые наборы символов русских, латинских, цифровых, чередующихся символов - русских, лати ских, цифровых, определенное число одного какого-либо символа и т.д. Считанные из блока памяти наборы тестов подаются на кодовые выходы 15-1, 15-2, 15-К,--.число которых определяется числом разрядов кодовых комбинаций тестов. Дополнительный разряд - управлякяций выход 16 используется в качестве указателя окончания данного теста, причем пос ледняя кодовая комбинация каждого теста содерясит единичное значение разряда 16 и нулевое его значение для всех предыдущих кодовых комбина ций данного теста. Управляющий выхо 14 блока 13 памяти предназначен для управления адресным счетчиком 12 после чтения каждой кодовой комбина ции . Блок 6 задержки включения содер;жит для каждого входного сигнала элемент 7 задержки и элемент И 8, которые обеспечивают задержку выход ного сигнала по отношению к входному при подаче входного сигнала и снятие без задержки выходного сигнала при снятии входного сигнала. Устройство работает следуннцим образом. Б исходном положении триггер 20 счетчик 12 к регистр 3 обнулены. С помощью клавиш 2-1, 2-2, 2-К набирают необходимую комбинацию тестов для контроля заданного объекта. Каждая из клавиш 2 соответствует определенному тесту, записанному в определенной области памяти блока 13 памяти и.заданному определенным начальным адресом. При нажатии на клавиши на их входах формируются импульсы, устанавливающие в единичные состояния соответствующие разряды 4 регистра 3. После набора состояние регистра 3 соответствует требуемой комбинации тестов. Сигналы с выходов сработанных разрядов 4 регистра 3 подаются на входы блока 5 приоритета, который формирует сигнал только на одном из своих выходов, соответствующем входному сигналу большего приоритета, например разряду 4-1, Этот сигнал с выхода блока 5 приоритета .проходит через соответствующие элементы задержки 7-1 и И 8-1 блока б задержки включения на первый вход соответствующего элемента И 9-1 и на соответствукнций вход шифратора 10. При возбуждении входа шифратора 10 на его кодовых выходах формируется код начального адреса, соответствующий первому выбираемому по -приоритету тесту. Указанный код поступает на установочные входы счетчика 12 и записывается в нем. Таким образом, на выходах счетчика 12 устанавливается код начального адреса , который поступает на адресные входы блока 13 памяти. Кроме того, сигналы кода с выходов счетчика 12 через элемент ИЛИ 22 запускают гет нератор 17 импульсов. Импульсы с выхода генератора 17 поступают на входы элементов И 18, 19. Элементы И 18, 19 управляются сигналами с выходов триггера 20, причем в нулевом положении триггера 20 открыт элемент И 19 и закрыт элемент И 18. Поэтому импульсы с выхода генератора 17 поступают через элемент И J.9 на считывающий вход блока 13 памяти. Каждый импульс генератора 17 , считывает одну кодовую комбинацию данного теста из блока памяти, начиная с адреса, указываемого счетчиком 12. Считанная кодовая комбинация теста подается с выходов 15 блока 13 памяти на проверяемый объект. После чтения каждой тестовой комбинации на выходе 14 блока памяти формируется импульс, поступаоиий на счетный вход счетчика 12. При этом содержимое счетчика каждый раз увеличивается на +1 и соответствует адресу след5пощей ячейки области памяти данного теста. Таким образом, происходит последовательная выборка всех комбинаций первого теста из ячеек данной области памяти. При выборке последней коде -ВОЙ комбинации теста на выходе 16 блока 13 памяти формируется единичный сигнал, который устанавливает триггер 20 в единичное состояние; Триггер 20 закрывает элемент И 19 и открывает элемент И 18. Очередной импульс с генератора 17 подается через элемент И 18 на второе входы элементов И 9,-на сбросовый вход счетчика 12 и на эЛемент 21 задержки. Этим импульсом открывается элемент И 9-1, подготовленный к открыванию сигналом с выхода элемента И 8-1 блока б задержки включения. Сигнал с выхода элемента И 9-1 постпает на нулевой вход соответствую-. щего разряда 4-1 регистра 3 и обнуляет его. При этом снимаются сигналы на выходе блока 5 приоритета, на выходе элемента И 8-1 блока б задержки включения, на входе и выходах шифратора 10 и входах счетчика 12. Одновременно импульсом с выхода элемента И 18 обнуляется счетчик 12 и с задержкой, определяемой элементом 21, триггер 20. При этом снова отк1Ж1вается элемент И 19 и зак1Я:1вается И 18. После сброса соответствующего разряда 4-1 JB регистре 3 приоритет на выход в блоке 5 получает сигнал с выхода следующего сработанного разряда 4-2 регистра 3, и устройство переходит

выборке кодовых комбинаций следующего второго теста. Этот сигнал с задержкой, определяемой элементом 7-2 задержки, проходит на выход элемента И 8-2, Время задержки, задаваемое элементами 7 в блоке 6 задержки включения, превышает время задержки, задаваемое элементом 21, что обеспечивает обнуление счетчика 12 и триггера 20 к моменту формирования очередного сигнала на соответствующем выходе элемента И 8-2 блока 6 задержки включения. Сигнал с выхода элемента И 8-2 поступает н% вход элемента И 9-2 и на 5 соответствующий вход шифратора 10, и описанный процесс повторяется. Таким образом, происходит последовательная выборка заданных тестовых комбинаций требуемых тестов и их выдача на проверяемый объект.

Технико-экономическая эффективность .предлагаемого устройства заключается в расширении его функциональных возможностей по организации тестового контроля, в возможности формировать любые необходимые наборы тестов с помощью тестовой клавиатуры для контроля различных объleKTOB без изменения электрических соединений, что повышает эффективность контроля и поиска неисправностей.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Устройство для формирования контрольных тестов | 1988 |

|

SU1605208A1 |

| Устройство для формирования тестов | 1988 |

|

SU1543408A1 |

| Устройство для последовательного выделения единиц из двоичного кода | 1984 |

|

SU1208553A1 |

| Устройство для формирования тестов в многорегистровых кодах | 1980 |

|

SU888126A1 |

| Устройство для контроля однотипных логических узлов | 1984 |

|

SU1223233A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1305687A1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

| Устройство для распределения заданий процессорам | 1987 |

|

SU1462315A1 |

lU

(

I л

а

Р -;.

15-г //-Л

Выходы J

Фаг. 2

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство для тестового контроля цифровых узлов электронных вычислительных машин | 1976 |

|

SU694863A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| 1979 |

|

SU826357A1 | |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1983-04-07—Публикация

1981-11-20—Подача