1

Изобретение относится к вычислительной технике и может быть использовано для контроля передачи данных.

Известно устройство для обнаружения ошибок, содержащее регистр,распределитель, коммутатор, блок управления, блок памяти и блок сравнения

Устройство включается в режим поиска при наличии сигналов .неисправностей на своих входах и обеспечивает последовательный опрос всех контролируемых цепей с помогдью распределителя .

Недостаток его заключается в том, что длительность контролируемых сигналов неисправностей ограничивается длительностью цикла опроса устройства. .Кроме того устройство имеет низкое {быстродействие, связанное с опросом всех без исключения контролируемых цепей, независимо от наличия или отсутствия в них сигналов неисправностей .

Наиболее близким к предлагаемому является устройство для фиксации сбоев, содержащее два регистра,счетчик, дешифратор, генератор импульсов, реле времени, формирователь, элементы И, ИЛИ и НЕ ГЗ.

Недостаток этого устройства низкое быстродействие, обусловленное тем, что в нем с помощью распределителя, состоящего из генератора импульсов, счетчика, и дешифратора,опрашиваются все входные конт1 олируемые цепи независимо от наличия или отсутствия в нух сигналов неисправности. Кроме того, известное устрой10ство позволяет документировать только признаки датчиков неисправностей, например порядковый номер или наименование неисправной цепи, злемента и т.п., без вьщачи рекомендаций для

15 их устранения.

Цель изобретения - повьшение быстродействия и расширение функциональных возможностей устройства.

Указанная цель достигается тем,

20 что в устройство для фиксации сбоев, содержащее первый и второй регистры, группу элементов И, выходы которых соединены со входами установки в О первого регистра, входы установ25ки в 1 которого являются входами сигналов сбоев устройства, генератор импульсов, выход которого соединен со счетным входом счетчика, введены блок приоритета, линия задержки,шиф30ратор, блок памяти и блок сравнения.

причем выходы первого регистра соединены соответственно с входами блока приоритета, выходы которого соединены соответственно со входами линии задержки, выходы линии задержки соединены соответственно со входами шифратора и первыми входами группы элементов И, выходы шифратора соединены со входами установки в 1 счетчика, вькоды которого соединены со входами блока памяти и с первыми входами блока сравнения, первые выходы блока памяти являются информационными выходами устройства, а вторые соединены со входами установки в 1 второго регистра, выходы которого соединены со вторьвми входами блока соединения, первый выход блока сравнения соединен со входом генератора импульсов, а второй - со входами установки в О второго регистра, со входами установки в О счетчика и со вторьвли входами группы элементов И.

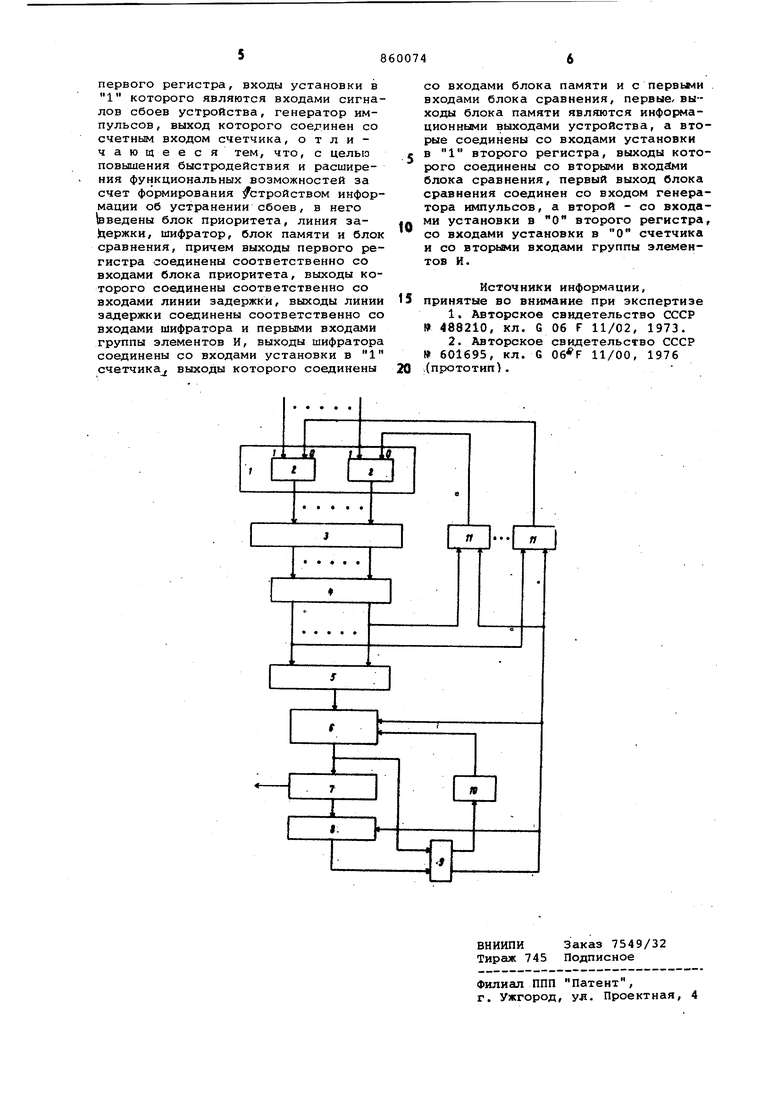

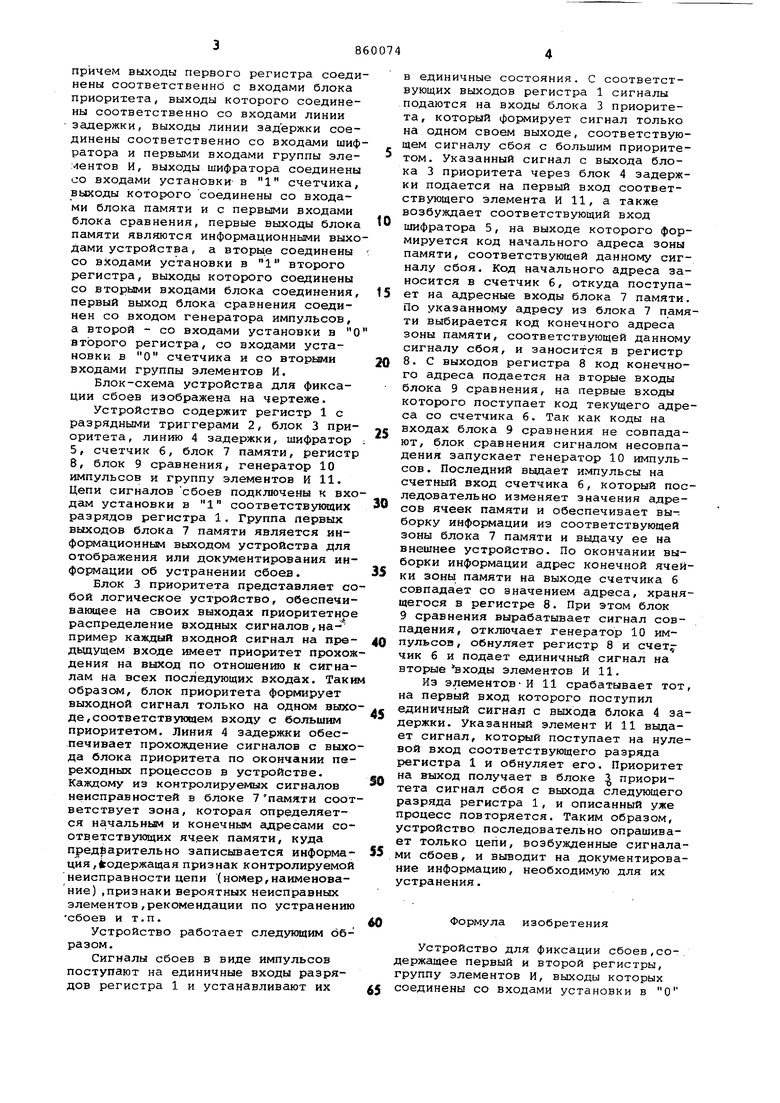

Блок-схема устройства для фиксации сбоев изображена на чертеже.

Устройство содержит регистр 1 с разрядными триггерами 2/ блок 3 приоритета, линию 4 задержки, шифратор 5, счетчик 6, блок 7 памяти, регистр 8, блок 9 сравнения, генератор 10 импульсов и группу элементов И 11. Цепи сигналов сбоев подключены к входам установки в 1 соответствуннцих разрядов регистра 1. Группа первых выходов блока 7 памяти является информационньм выходом устройства для отображения или документирования информации об устранении сбоев.

Блок 3 приоритета представляет собой логическое устройство, обеспечивающее на своих выходах приоритетное распределение входных сигналов,например каждый входной сигнал на предьщущем входе имеет приоритет прохождения на выход по отношению н сигналам на всех последующих входах. Таки образс 1, блок приоритета формирует выходной сигнал только на одном выходе, соответствующем входу с большим приоритетом. Линия 4 задержки обеспечивает прохождение сигналов с выхода блока приоритета по окончании переходных процессов в устройстве. Каждому из контролируемых сигналов неисправностей в блоке 7памяти соответствует зона, которая определяется начальным и конечньм адресами соответствуклцих ячеек памяти, куда предйарительно записывается информация, Содержащая признак контролируемой неисправности цепи (номер наименование) .признаки вероятных неисправных элементов,рекомендации по устранению сбоев и т. п .

Устройство работает следующим образом.

Сигналы сбоев в виде импульсов поступают на единичные входы разрядов регистра 1 и устанавливают их

в единичные состояния. С соответствующих выходов регистра 1 сигналы подаются на входы блока 3 приоритета, который формирует сигнал только на одном своем выходе, соответствующем сигналу сбоя с большим приоритетом. Указанный сигнал с вЕлхода блока 3 приоритета через блок 4 задержки подается на первый вход соответствующего элемента И 11, а также возбуждает соответствующий вход шифратора 5, на выходе которого формируется код начального адреса зоны памяти, соответствующей данному сигналу сбоя. Код начального адреса заносится в счетчик 6, откуда поступает на сщресные входы блока 7 памяти. По указанному адресу из блока 7 памяти выбирается код конечного адреса зоны памяти, соответствующей данному сигналу сбоя, и заносится в регистр 8. С выходов регистра 8 код конечного адреса подается на вторые входы блока 9 сравнения, на первые входы которого поступает код текущего адреса со счетчика б. Так как коды на входах блока 9 сравнения не совпадают, блок сравнения сигналом несовпадения запускает генератор 10 импульсов . Последний выдает импульсы на счетный вход счетчика б, который последовательно изменяет значения алЕ)есов ячеек памяти и обеспечивает выборку информации из соответствующей зоны блока 7 памяти н выдачу ее на внешнее устройство. По окончании выборки информации адрес конечной ячейки зоны памяти на выходе счетчика б совпадает со значением адреса, хранящегося в регистре 8. При этом блок 9 сравнения вырабатывает сигнал совпадения, отключает генератор 10 импульсов , обнуяяет регистр 8 и б и подает единичный сигнал на вторые входы злетиентов И 11,

Из элементов-И 11 срабатывает тот на первый вход которого поступил единичный сигнал с выхода блока 4 задержки. Указанный элемент и 11 вьщает сигнал, который поступает на нулевой вход соответствующего разряда регистра 1 и обнуляет его. Приоритет на выход получает в блоке приоритета сигнал сбоя с выхода следующего разряда регистра 1, и описанный уже процесс повторяется. Таким образом, устройство последовательно опрашивает только цепи, возбужденные сигналами сбоев, и выводит на документирование информацию, необходимую для их устранения.

Формула изобретения

Устройство для фиксации сбоев,содержащее первый и второй регистры, группу элементов и, выходы которых соединены со входами установки в О

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для задания тестов | 1981 |

|

SU1010632A1 |

| Устройство для фиксации сбоев | 1984 |

|

SU1213479A1 |

| Имитатор абонентов | 1986 |

|

SU1325490A2 |

| Устройство для контроля дешифратора | 1984 |

|

SU1179343A1 |

| Устройство для фиксации сбоев | 1983 |

|

SU1151968A1 |

| Устройство для автоматического поиска неисправностей | 1972 |

|

SU467331A1 |

| Устройство для управления процессом передачи сигналов управления в иерархической автоматизированной системе управления | 1988 |

|

SU1525679A2 |

| Программируемый коммутатор | 1985 |

|

SU1287277A1 |

| Устройство для контроля срабатывания клавиш наборного поля | 1985 |

|

SU1297050A1 |

| Устройство для программного управления | 1982 |

|

SU1057927A1 |

Авторы

Даты

1981-08-30—Публикация

1979-08-24—Подача