tc

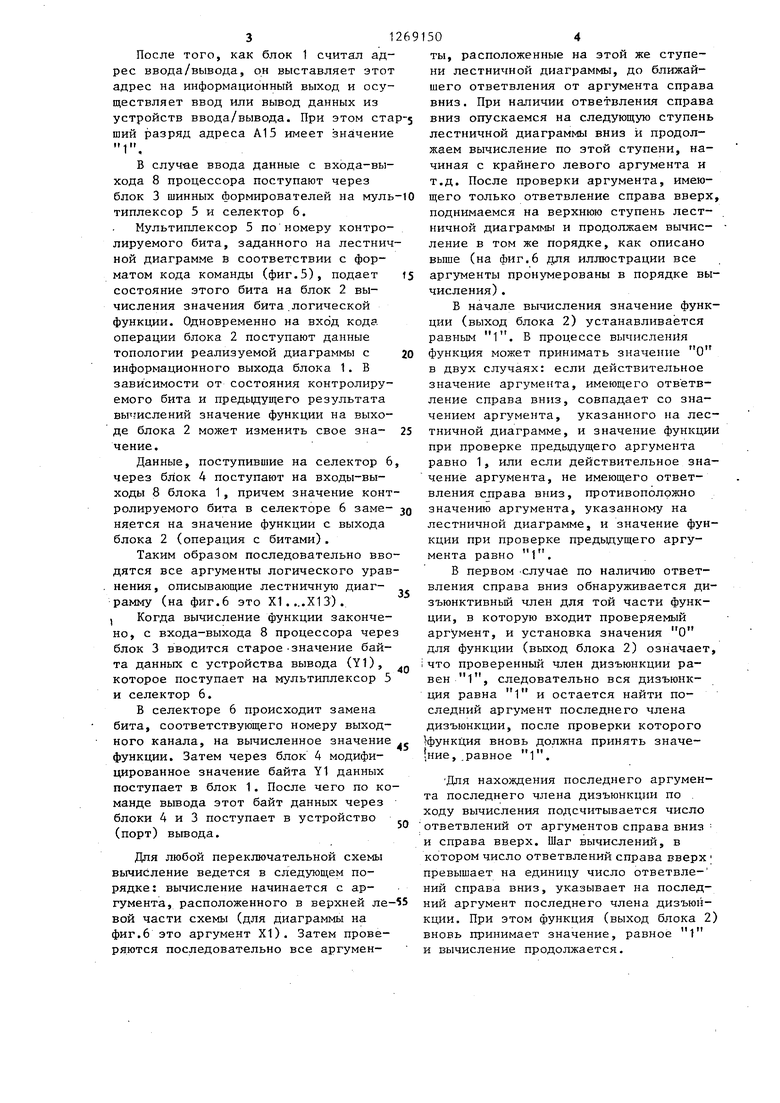

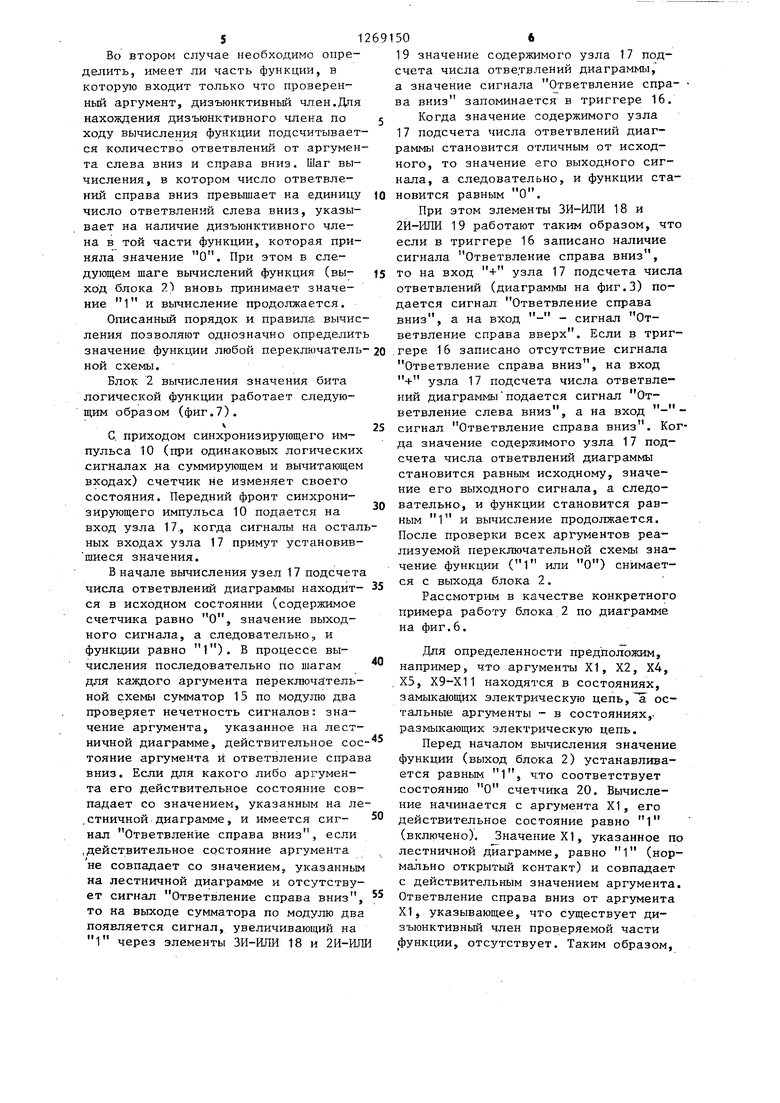

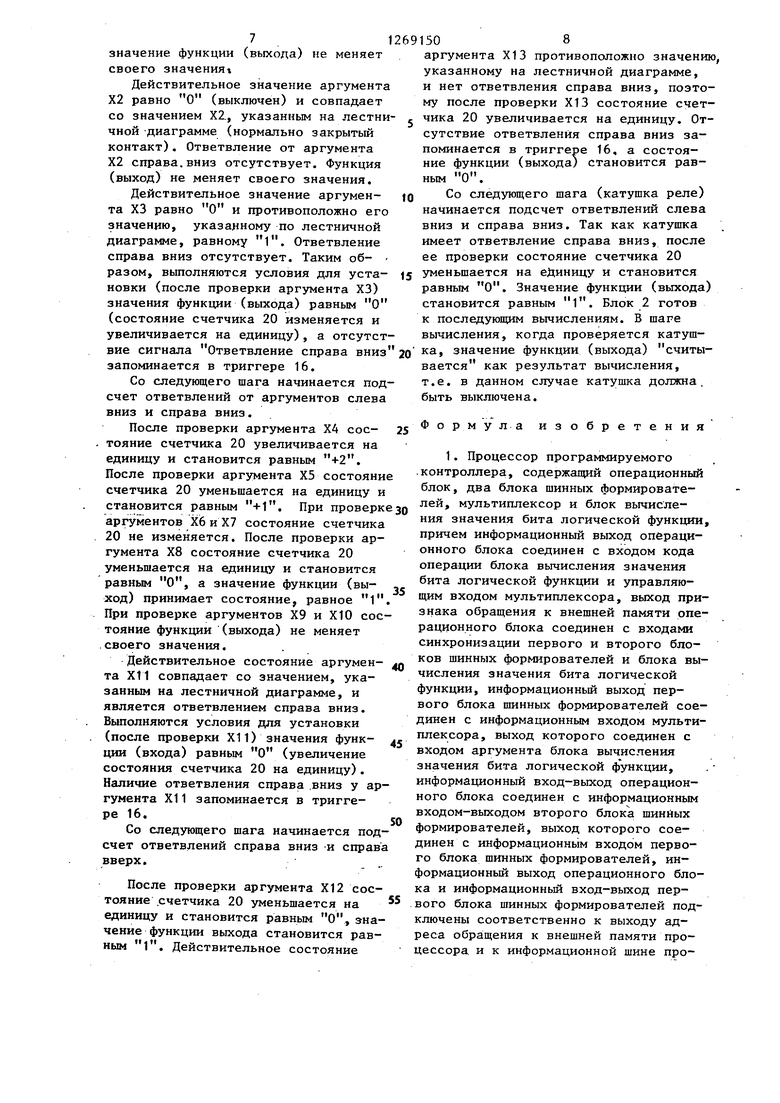

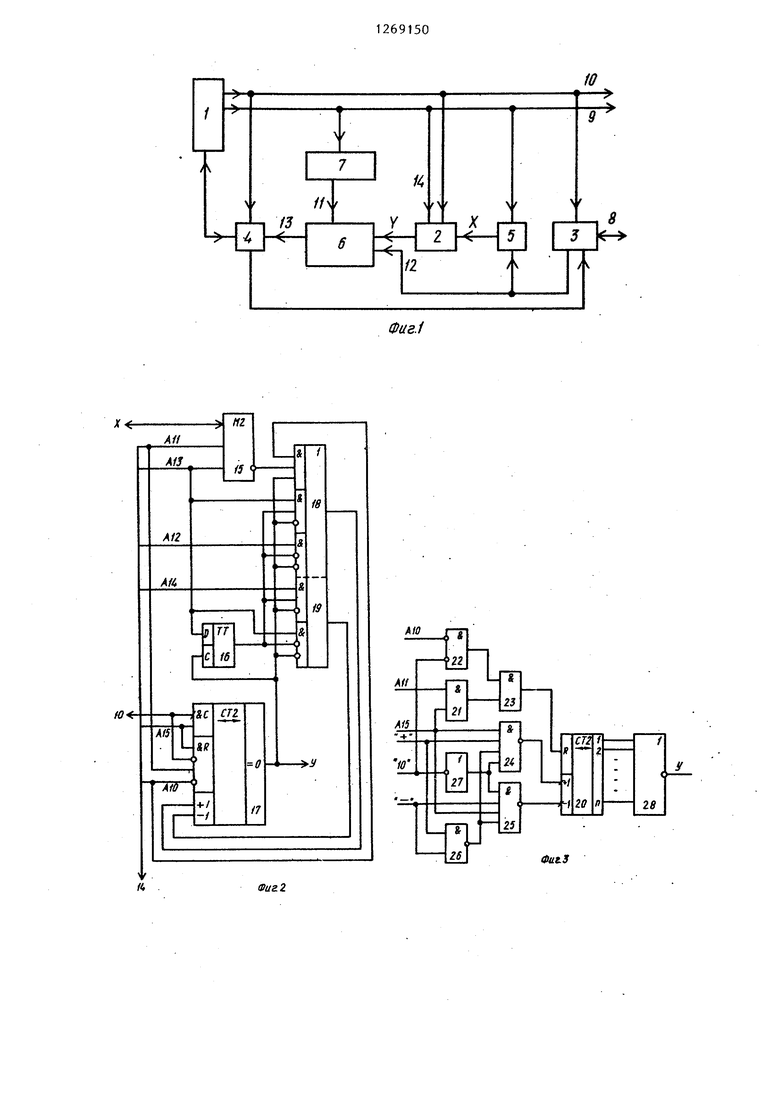

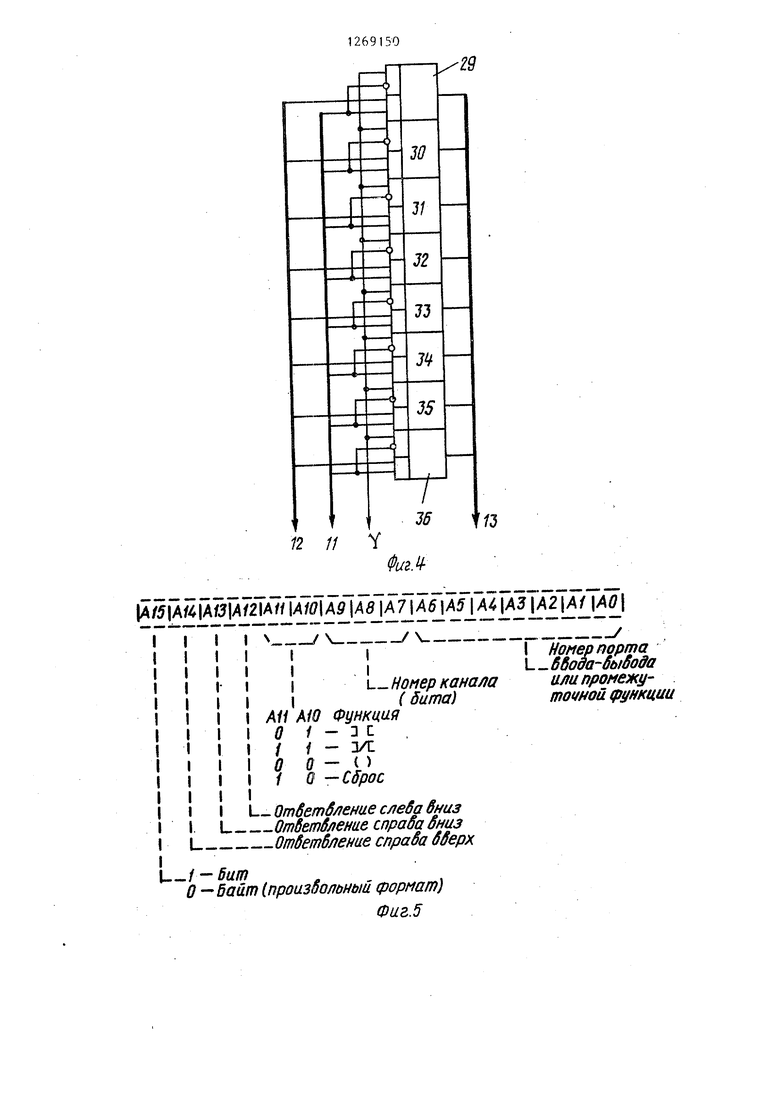

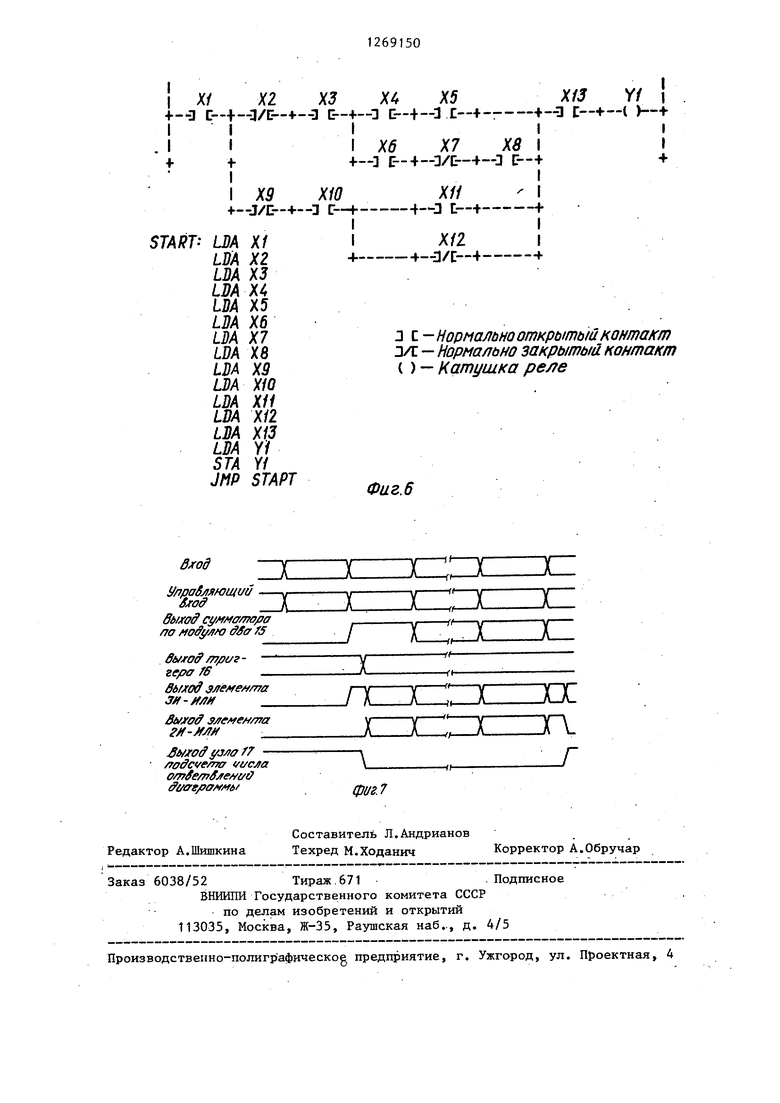

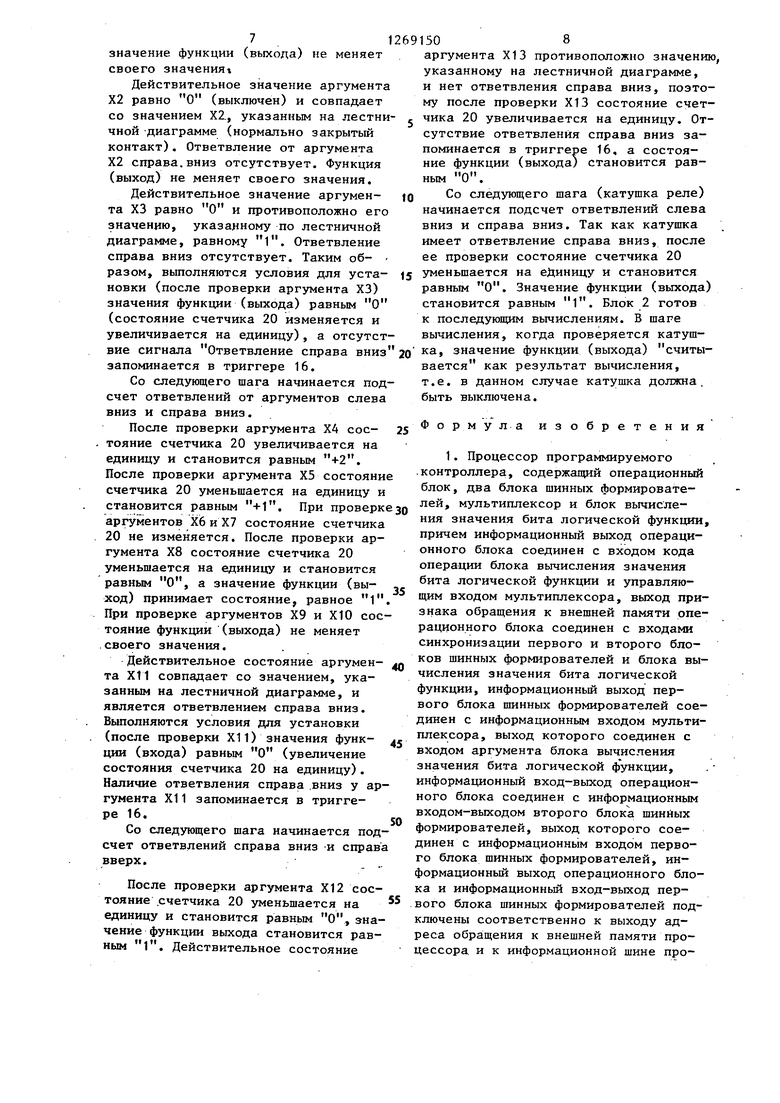

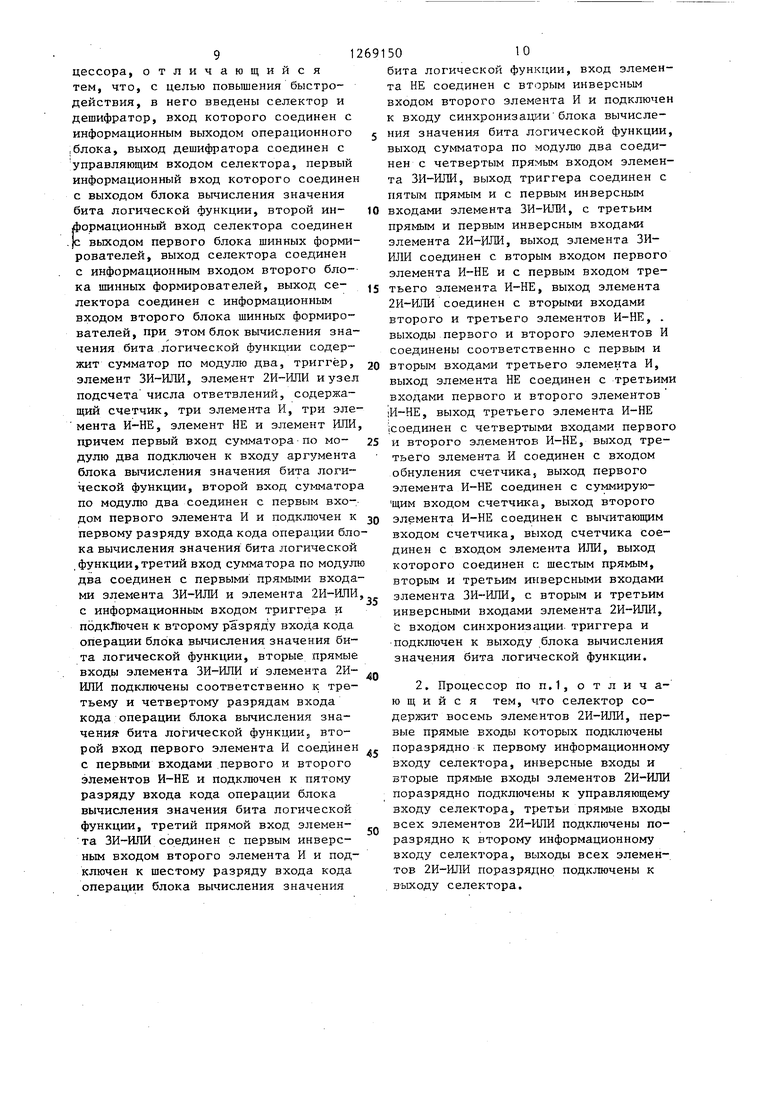

Од СО Изобретение относится к вычислительной технике, в частности к программному управлению технологическим оборудованием, и может быть использовано в программируемых системах уп равления, а именно в программируемых контроллерах, выполненных на базе стан дартного микропроцессора с фиксированной системой команд. Цель изобретения - повышение быст родействия. На фиг.1 представлена структурная схема процессора; на фиг.2 - структурная схема блока вычисления значения бита логической функции; на фиг,3 - структурная схема узла подсчета числа ответвлений; на фиг.4 структурная .схема селектора; на фиг.5 формат кода команды; на фиг,6 переключательная схема и пример программы для вычисления логической функции процессором на языке ассемблер микропроцессора КР 580ИК80А; на фиг.7 - временная диаграмма работы блока вычисления значения бита логической функции. Процессор содержит (.фиг.т; операционньй блок 1, блок 2 вычисления зн чения бита логической функции, первы 3 и второй 4 блоки шинных формирователей, мультиплексор 5, селектор б и дешифратор 7. Входы-выходы первого блока 3 шинных формирователей подключены к информационной шине 8 процессора. Информационный выход операционного бло ка 1 подключен к выходу 9 адреса обращения к внешней памяти процессора. Выход признака обращения к внешней памяти операционного блока соединен с выходом 10 признака обращения к внешней памяти процессора. На фиг.1 обозначены также выход 1 дешифратора, управляющий вход Y селектора, первый информационный вход 12 селектора, выход 13 селектора, вход X аргумента и вход 14 кода операции блока вычисления значения бита Блок вычисления значения бита логической функции содержит (фиг.2) сумматор 15 по модулю два триггер 16 узел 17 подсчета числа ответвлений, элемент ЗИ-ИЛИ 18 и элемент 2И-1ШИ 19. Вход X является входом аргумента вход 14 - входом кода операции, входы А10, All, А12, А14, А15 являются разрядами кода операции, выход 10 является входом синхронизации блока вычисления значения бита логической функции. Узел подсчета числа ответвлений (фиг.З) содержит реверсивный счетчик 20, три элемента И 21-23, три элемента И-НЕ 24-26, элемент НЕ 27 и элемент ИЛИ 28. Входы А10, А11, А15 являются разрядами кода операции, вход 10 является входом синхронизации, вход + - управляющим входом сложения, а вход - - управляющим входом вычитания узла подсчета числа ответвлений. Селектор 6 (фиг.4) содержит восемь элементов 2И-ИЛИ 29-36. Первые прямые входы элементов 29-36 подключены к первому информационному входу Y селектора 6, инверсные и вторые прямые входы элементов 29-36 поразрядно подключены к управляющему входу 11 селектора, третьи прямые входы элементов 2И-Ш1И 29-36 подключены поразрядно к второму информационному входу 12 селектора, выходы элементов 2И-ИЛИ 29-36 подключены к выходу 13 селектора. На фиг.6, представляющей пример переключательной схемы, элементы обозначены символом X с номерами, обозначающими порядок вычисления функции. Катушка реле обозначена символом Y1. Устройство работает следующим образом. Процессор работает на программе, записанной в области внешней памяти, старший разряд адреса А15 которой имеет значение О. При этом осталь|ные разряды адреса могут принимать любые значен:ия:. Адресами со значением старшего разряда А15, равньт 1, адресуется область ввода-вывода программируемого контроллера, при этом код команды соответствует формату, показанному на фиг.5. Выполняя nporpaMify (фиг.6), блок 1 в первом байте команды считывает код операции, затем считывает адрес ввода/вывода, непосредственно заданный во втором и третьем байтах команды. Пр этом на первом информационном выходе блока 1 старший разряд А15 имеет значение О, а данные через блок 3 шинных формирователей, мультиплексор 5 и блок 4 шинных формирователей поступают на входы-выходы блока 1 без изменений (операция с байтами). 3 После того, как блок 1 считал ад рес ввода/вывода, он выставляет это адрес на информационный выход и осу ществляет ввод или вывод данных из устройств ввода/вывода. При этом ст ший разряд адреса А15 имеет значени I) 4 It I В случае ввода данные с входа-вы хода 8 процессора поступают через блок 3 шинных формирователей на мул типлексор 5 и селектор 6. Мультиплексор 5 по номеру контро лируемого бита, заданного на лестни ной диаграмме в соответствии с форматом кода команды (фиг.5), подает состояние этого бита на блок 2 вычисления значения бита.логической функции. Одновременно на вход кода операции блока 2 поступают данные топологии реализуемой диаграммы с информационного выхода блока 1. В зависимости от состояния контролируемого бита и предыдущего результата вышслений значение функции на выходе блока 2 может изменить свое значение. Данные, поступивише на селектор 6 через блок 4 поступают на входы-выходы 8 блока 1, причем значение конт ролируемого бита в селекторе 6 заменяется на значение функции с выхода блока 2 (операция с битами). Таким образом последовательно вво дятся все аргументы логического урав нения , описывающие лестничную диаграмму (на фиг.6 это Х1....Х13). I Когда вычисление функции закончено, с входа-выхода 8 процессора чере блок 3 вводится старое -значение байта данных с устройства вывода (Y1), которое поступает на мультиплексор 5 и селектор 6. В селекторе 6 происходит замена бита, соответствующего номеру выходного канала, на вычисленное значение функции. Затем через блок 4 модифицированное значение байта Y1 данных поступает в блок 1. После чего по ко манде вывода этот байт данных через блоки 4 и 3 поступает в устройство (порт) вьгеода. Для любой переключательной схемы вычисление ведется в следующем порядке : вычисление начинается с аргумента, расположенного в верхней ле вой части схемы (для диаграммы на фиг.6 это аргумент XI). Затем проверяются последовательно все аргумен504ты, расположенные на этой же ступени лестничной диаграммы, до ближайшего ответвления от аргумента справа вниз. При наличии ответвления справа вниз опускаемся на следующую ступень лестничной диаграммы вниз и продолжаем вычисление по этой ступени, начиная с крайнего левого аргумента и т.д. После проверки аргумента, имеющего только ответвление справа вверх, поднимаемся на верхнюю ступень лестничной диаграммы и продолжаем вычисление в том же порядке, как описано выше (на фиг.6 для иллюстрации все аргументы пронумерованы в порядке вычисления) . В начале вычисления значение функции (выход блока 2) устанавливается равным 1. В процессе вычисления функция может принимать значение О в двух случаях: если действительное значение аргумента, имеющего ответвление справа вниз, совпадает со значением аргумента, указанного на лестничной диаграмме, и значение функции при проверке предьщущего аргумента равно 1, или если действительное значение аргумента, не имеющего ответвления справа вниз, противоположно значению аргумента, указанному на лестничной диаграмме, и значение функции при проверке предьщущего аргумента равно 1. В первом -случае по наличию ответвления справа вниз обнаруживается дизъюнктивный член для той части функции, в которую входит проверяемый аргумент, и установка значения О для функции (выход блока 2) означает, что проверенный член дизъюнкции равен 1, следовательно вся дизъюнкция равна 1 и остается найти последний аргумент последнего члена дизъюнкции, после проверки которого функция вновь должна принять значение,.равное 1. Для нахождения последнего аргумена последнего члена дизъюнкции по . оду вычисления подсчитывается число тветвлений от аргументов справа вниз справа вверх. Шаг вычислений, в котором число ответвлений справа вверх ревышает на единицу число ответвлеИИ справа вниз, указывает на последий аргумент последнего члена дизъюнции. При этом функция (выход блока 2) новь принимает значение, равное 1 вычисление продолжается. Во втором случае необходимо определить, имеет ли часть функции, в которую входит только что проверенный аргумент, дизъюнктивньй чл:ен,Для нахождения дизъюнктивного члена по ходу вычисления функции подсчитывает ся количество ответвлений от аргумен та слева вниз и справа вниз. Шаг вычисления, в котором число ответвлений справа вниз превьшает на единицу число ответвлений слева вниз, указывает на наличие дизъюнктивного члена в той части функции, которая приняла значение О. При этом в следующем шаге вычислений функция: (выход блока 2) вновь принимает значение 1 и вычисление продолжае.тся. Описанный порядок и правила вычис ления позволяют однозначно определит значение функции любой переключатель ной схемы. Блок 2 вычисления значения бита логической функции работает следующим образом (фиг.7). С. приходом синхронизирующего импульса 10 (при одинаковых логических сигналах .на суммирующем и вычитающем входах) счетчик Не изменяет своего состояния. Передний фронт синхронизирующего импульса 10 подается на вход узла 17., когда сигналы на остал ных входах узла 17 примут установившиеся значения. В начале вычисления узел 17 подсчета числа ответвлений диаграммы находится в исходном состоянии (содержимое счетчика равно О, значение выходного сигнала, а следовательно., и функции равно 1). В процессе вычисления последовательно по шагам для каждого аргумента переключательной схемы сумматор 15 по модулю два прове ряет нечетность сигналов:; значение аргумента, указанное на лестничной диаграмме, действительное сос тояние аргумента и ответвление справ вниз. Если для какого либо аргумента его действительное состояние совпадает со значением, указанным на ле .стничной диаграмме, и имеется сигнал Ответвление справа вниз, если ,действительное состояние аргумента не совпадает со значением, указанным на лестничной диаграмме и отсутствует сигнал Ответвление справа вниз, то на выходе сумматора по модулю два появляется сигнал, увеличивающий на 1 через элементы ЗИ-ИЛИ 18 и 2И-ИЛ 19 значение содержимого узла 17 подсчета числа ответвлений диаграммы, а значение сигнала Ответвление справа вниз запоминается в триггере 16. Когда значение содержимого узла 17 подсчета числа ответвлений диаграммь становится отличным от исходного, то значение его выходного сигнала, а следовательно, и функции становится равным О. При этом элементы ЗИ-ИЛИ 18 и 2И-ИЛИ 19 работают таким образом, что если в триггере 16 записано наличие сигнала Ответвление справа вниз, то на вход + узла 17 подсчета числа ответвлений (диаграммы на фиг.З) подается сигнал Ответвление справа вниз, а на вход - - сигнал Ответвление справа вверх. Если в триггере 16 записано отсутствие сигнала Ответвление справа вниз, на вход + узла 17 подсчета числа ответвлений диаграммыподается сигнал Ответвление слева вниз, а на вход - сигнал Ответвление справа вниз. Когда значение содержимого узла 17 подсчета числа ответвлений диаграммы становится равным исходному, значение его выходного сигнала, а следовательно, и функции становится равным 1 и вычисление продолжается. После проверки всех аргументов реализуемой переключательной схемы значение функции (1 или О) снимается с выхода блока 2. Рассмотрим в качестве конкретного примера работу блока 2 по диаграмме на фиг.6. Для определенности предположим, например, что аргументы XI, Х2, Х4, Х5, Х9-Х11 находятся в состояниях, замыкающих электрическзто цепь,а остальные аргументы - в состояниях,размыкающих электрическую цепь. Перед началом вычисления значение функции (выход блока 2) устанавливается равным 1, что соответствует состоянию О счетчика 20. Вычисление начинается с аргумента XI, его действительное состояние равно 1 (включено). Значение XI, указанное по лестничной диаграмме, равно 1 (нормально открытый контакт) и совпадает с действительным значением аргумента. Ответвление справа вниз от аргумента XI, указывающее, что существует дизъюнктивный член проверяемой части функции, отсутствует. Таким образом. значение функции (выхода) не меняет своего значениях Действительное значение аргумента Х2 равно О (выключен) и совпадает со значением Х2., указанным на лестни чной диаграмме (нормально закрытый контакт). Ответвление от аргумента Х2 справа.вниз отсутствует. Функция (выход) не меняет своего значения. Действительное значение аргумента ХЗ равно О и противоположно его значению, указанному по лестничной диаграмме, равному 1. Ответвление справа вниз отсутствует. Таким образом, выполняются условия для установки (после проверки аргумента ХЗ) значения функции (выхода) равным О (состояние счетчика 20 изменяется и увеличивается на единицу), а отсутст вие сигнала Ответвление справа вниз запоминается в триггере 16. Со следующего шага начинается под счет ответвлений от аргументов слева вниз и справа вниз. После проверки аргумента Х4 сое- тояние счетчика 20 увеличивается на единицу и становится равным +2. После проверки аргумента Х5 состояни счетчика 20 уменьшается на единицу и становится равным +1. При проверк аргументов Х6иХ7 состояние счетчика 20 не изменяется. После проверки аргумента Х8 состояние счетчика 20 уменьшается на единицу и становится равным О, а значение функции (выход) принимает состояние, равное 1 При проверке аргументов Х9 и XtO сос тояние функции (выхода) не меняет .своего значения. Действительное состояние аргумента XII совпадает со значением, указанным на лестничной диаграмме, и является ответвлением справа вниз. Выполняются условия для установки (после проверки Х11) значения функции (входа) равным О (увеличение состояния счетчика 20 на единицу). Наличие ответвления справа .вниз у ар гумента XI1 запоминается в триггере 16. Со следующего шага начинается под счет ответвлений справа вниз и справ вверх.. После проверки аргумента XI2 состояние счетчика 20 уменьшается на единицу и становится равным О, значение функции выхода становится равным 1, Действительное состояние аргумента Х13 противоположно значению, указанному на лестничной диаграмме, и нет ответвления справа вниз, позтому после проверки Х13 состояние счетчика 20 увеличивается на единицу. Отсутствие ответвления справа вниз запоминается в триггере 16, а состояние функции (выхода) становится равным О. Со следующего шага (катушка реле) начинается подсчет ответвлений слева вниз и справа вниз. Так как катушка имеет ответвление справа вниз, после ее проверки состояние счетчика 20 уменьшается на единицу и становится равным О. Значение функции (выхода) становится равным 1. Блок 2 готов к последующим вычислениям. В шаге вычисления, когда проверяется катуш а, значение функции (выхода) считывается как результат вычисления. т.е. в данном случае катушка должна, быть выключена. Формула изобретения 1. Процессор программируемого .контроллера, содержащий операционный блок, два блока шинных формировате мультиплексор и блок вьгчисления значения бита логической функции, причем информационный выход операционного блока соединен с входом кода операции блока вычисления значения бита логической функции и управляющим входом мультиплексора, выход признака обращения к внешней памяти операционного блока соединен с входами синхронизации первого и второго блоков шинных формирователей и блока вычисления значения бита логической функции, информационный выход первого блока шинных формирователей соединен с информационным входом мультиплексора, выход которого соединен с входом аргумента блока вычисления значения бита логической функции, информационный вход-выход операционного блока соединен с информационным входом-выходом второго блока шинных формирователей, выход которого соединен с информационным входом первого блока шинных формирователей, информационный выход операционного блока и информационный вход-выход первого блока шинных формирователей подключены соответственно к выходу адреса обра щения к внешней памяти процессора и к информационной шине про91цессора, отличающийся тем, что, с целью повышения быстродействия, в него введены селектор и дешифратор, вход которого соединен с информационным выходом операционного ,блока, выход дешифратора соединен с управляющим входом селектора, первый информационный вход которого соединен с выходом блока вычисления значения бита логической функции, второй инДормационньш вход селектора соединен .)с выходом первого блока шинных формирователей, выход селектора соединен с информационным входом второго блока шинных формирователей, выход селектора соединен с информационным входом второго блока шинных формирователей, при этом блок вычисления значения бита .логической функции содержит сумматор по модулю два, триггер, элемент ЗИ-ИЛИ, элемент 2И-ИЛИ и узел подсчета числа ответвлений, содержащий счетчик, три элемента И, три эле мента И-НЕ, элемент НЕ и элемент ИЛИ причем первый вход сумматора по модулю два подключен к входу аргумента блока вычисления значения бита логической функции, второй вход cyt-iMaTop по модулю два соединен с первым входом первого элемента И и подключен к первому разряду входа кода операции бло ка вычисления значения бита логической .функции,третий вход сумматора по модул два соединен с первыми прямыми входа ми элемента ЗИ-ИЛИ и элемента 2И-ИЛИ с информационным входом триггера и подключен к второму разряду входа кода операции блока вычисления значен:ия бита логической функции, вторые прямые входы элемента ЗИ-ИЛИ и элемента 2ИИЛИ подключены соответственно к третьему и четвертому разрядам входа кода операции блока вычисления значения бита логической функции; второй вход первого элемента И соединен с первыми входами первого и второго элементов и подключен к пятому разряду входа кода операции блока вычисления значения бита логической функции, третий прямой вход элемента ЗИ-ИЛИ соединен с первым инверсным входом второго элемента И и подключен к шестому разряду входа кода операции блока вычисления значения 5010 бита логической функции, вход элемента НЕ соединен с вторым инверсным входом второго элемента И и подключен к входу синхронизацииблока вычисления значения бита логической функции, выход сумматора по модулю два соединен с четвертым прямым входом элемента ЗИ-ИЛИ, выход триггера соединен с пятым прямым и с первым инверсным входами элемента ЗИ-ИЛИ, с третьим прямым и первым инверсным входами элемента 2H-HnHj выход элемента ЗИИЛИ соединен с вторым входом первого элемента И-НЕ и с первым входом третьего элемента И-НЕ, выход элемента 2И-ИЛИ соединен с вторыми входами второго и третьего элементов И-НЕ, . выходы первого и второго элементов И соединены соответственно с первым и вторым входами третьего элемента И, выход элемента НЕ соединен с третьими входами первого и второго элементов ;И-НЕ, выход третьего элемента И-НЕ (Соединен с четвертыми входами первого и второго элементов И-НЕ, выход третьего элемента И соединен с входом обнуления счетчикаS выход первого элемента И-НЕ соединен с суммирующим входом счетчика, выход второго элемента И-НЕ соединен с вычитающим входом счетчика, выход счетчика Соединен с входом элемента ИЛИ, выход которого соединен с шестым прямым, вторым и тр€;тьим инверсными входами элемента ЗИ-ИПИ, с вторым и третьим инверсными входами элемента 2И-ИЛИ, с входом синхронизации триггера и подключен к выходу блока вычисления значения бита логической функции. 2. Процессор по п.1, о т л и ч аю щ и и с я тем, что селектор содержит восемь элементов 2И-ИЛИ, первые прямые входы которых подключены поразрядно к первому информационному входу селектора, инверсные входы и вторые прямые входы элементов 2И-ИЛИ поразрядно подключены к управляющему входу селектора, третьи прямые входы всех элементов 2И-Ш1И подключены поразрядно к 3 торому информационному входу селектора, выходы всех элементов 2И-ИЛИ поразрядно подключены к въосоду селектора.

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1986 |

|

SU1328815A1 |

| Устройство для подсчета числа ответвлений диаграммы | 1983 |

|

SU1160391A1 |

| Устройство для программной реализации переключательных схем | 1990 |

|

SU1836679A3 |

| Устройство для программной реали-зАции пЕРЕКлючАТЕльНыХ CXEM | 1978 |

|

SU813413A1 |

| Устройство для подсчета числа ответвлений диаграммы | 1988 |

|

SU1539766A1 |

| Цифровой преобразователь координат | 1981 |

|

SU960834A1 |

| Способ тестирования накопителей на магнитных дисках и устройство для его осуществления | 1989 |

|

SU1615793A1 |

| Устройство для измерения частоты гармонического сигнала | 1987 |

|

SU1525607A1 |

| Устройство для вычисления булевых функций | 1982 |

|

SU1049898A1 |

| Процессор программируемого контроллера | 1985 |

|

SU1406595A1 |

Изобретение относится к области вычислительной техники, в частности к программному управлению технологическим оборудованием, и может быть использовано в программируемых контроллерах, выполненных на базе стандартного микропроцессора с фиксированной системой команд. Цель изобретения - повьпиение быстродействия, достигаемое тем, что в устройство, содержащее операционный блок, два блока шинных формирователей, мультиплексор и блок вычисления-значения бита логической функции, введены дешифратор и селектор, а блок вычисления значения бита логической функции со- . держит сумматор по модулю два, триггер, элемент ЗИ-ИЛИ, элемент 2И-ШШ ги узел подсчета числа ответвлений, е -содержащий реверсивный счетчик, три (Л элемента И, три элемента И-НЕ, элемент НЕ и элемент ИЛИ. 1 з.п.ф-лы, 7 кл.

(t,

(Риг 2

12 11 Y

|Д/5|А/4|А/5И/21А//|Д/(7|АР Д5|А7|Д5И5|Д4|А5|Д2И/И(|

NJ / V.

IНомер канала

(бита)

Функция

3L

3/L

О

Сброс

- Отбетб/гение слеба вниз

LОтбетбленае спраба бниз

IОтбетбление спраба бберк

-i-Bum

О - байт (произоолиныи формат)

/3

ФигЛ

/

Номер порта ббода-быбода илипронежуmowou (рункции

Фиг.З

| Устройство для логического управления | 1981 |

|

SU993260A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Патент CUA № 4303990, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1986-11-07—Публикация

1984-12-24—Подача