Иэ1:бретение относится к вычислительной технике,

и.ель изобретения - сокр.пщение об-: ема блока памяти програм-1ируемого ;оитроллера,

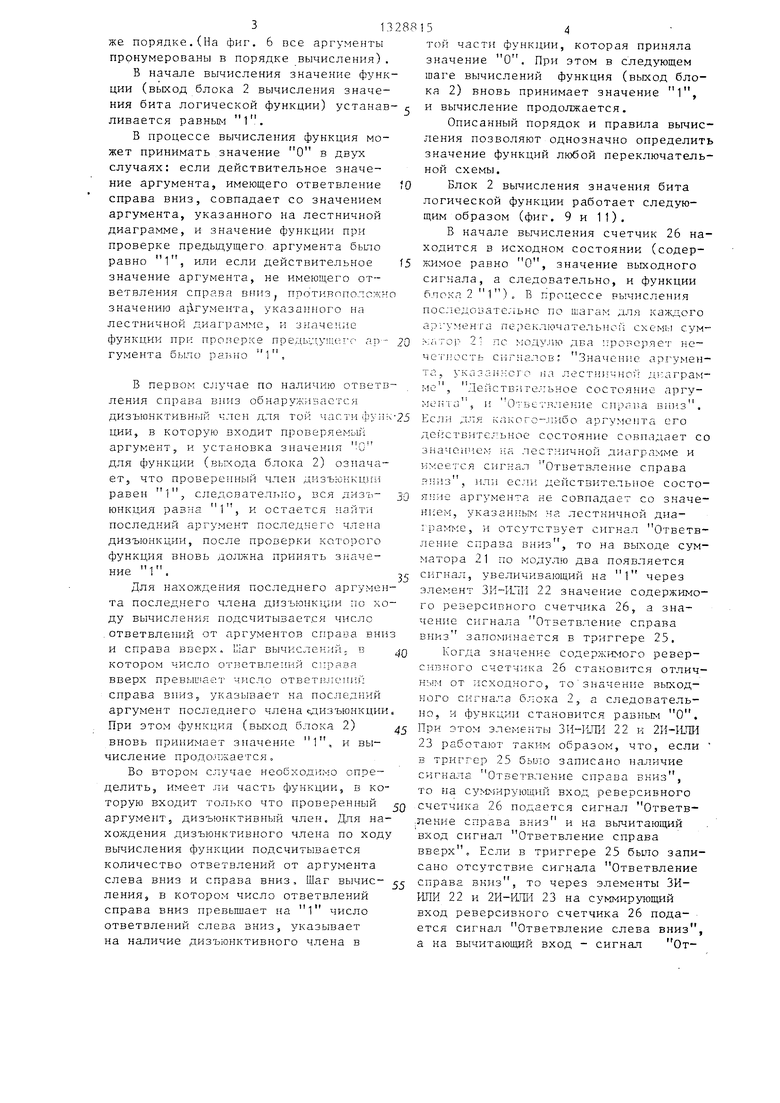

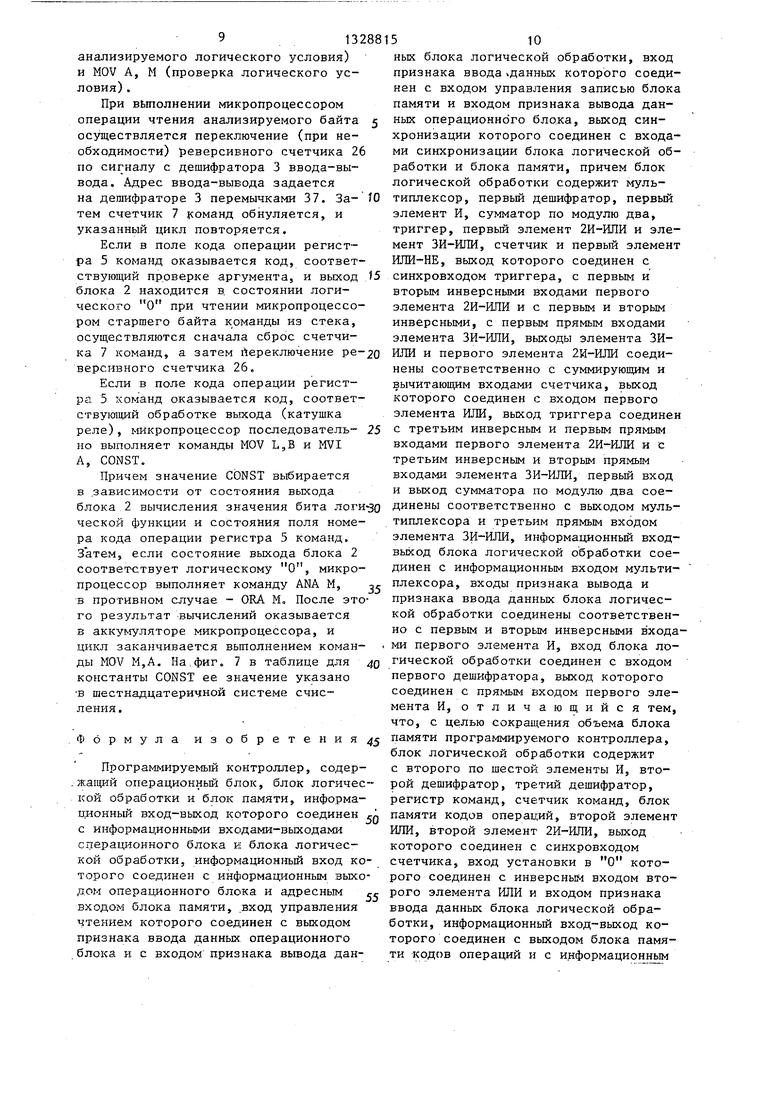

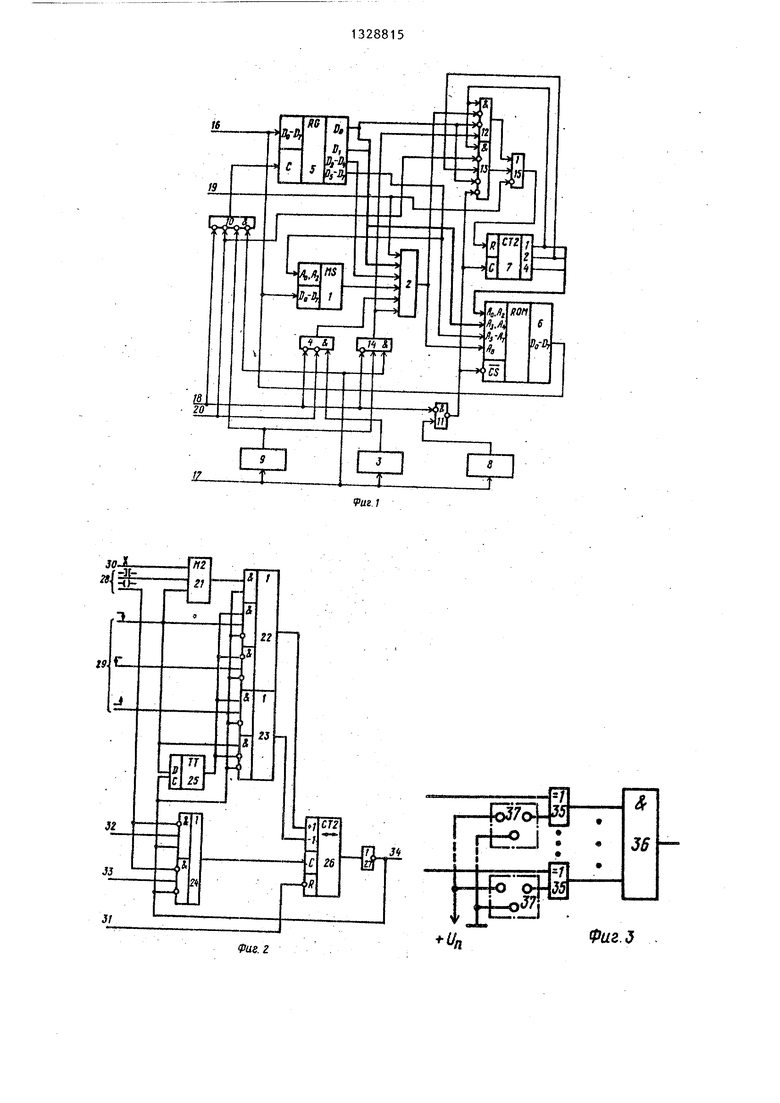

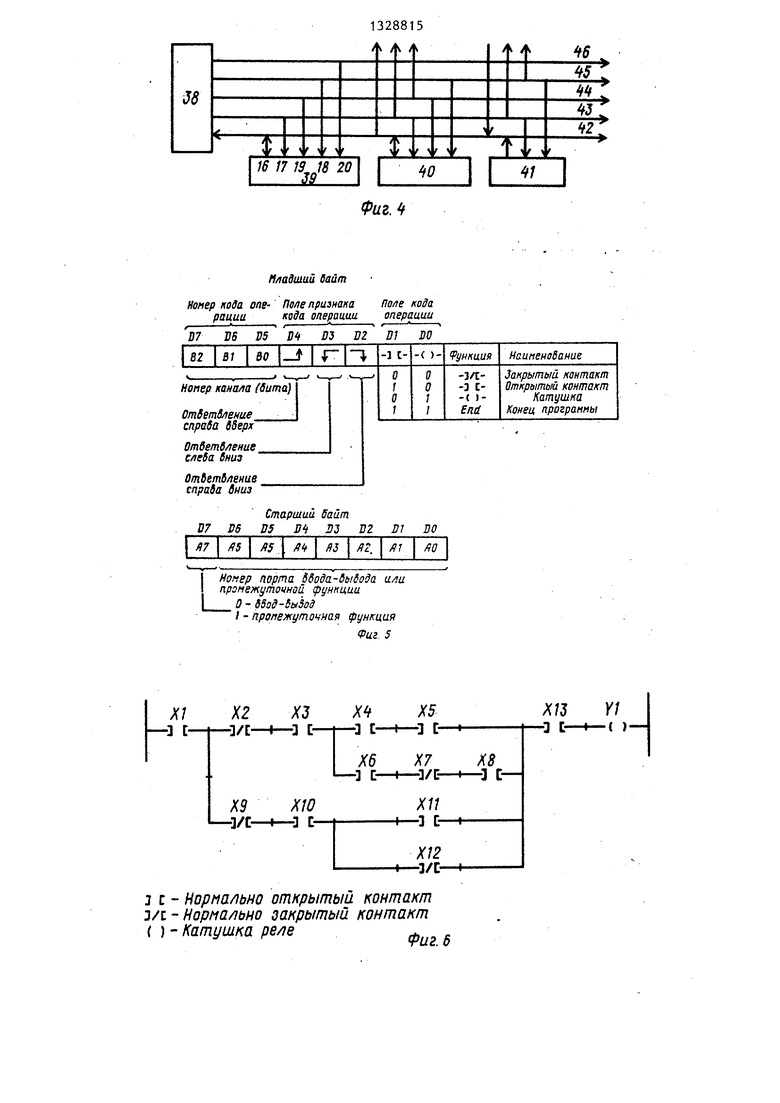

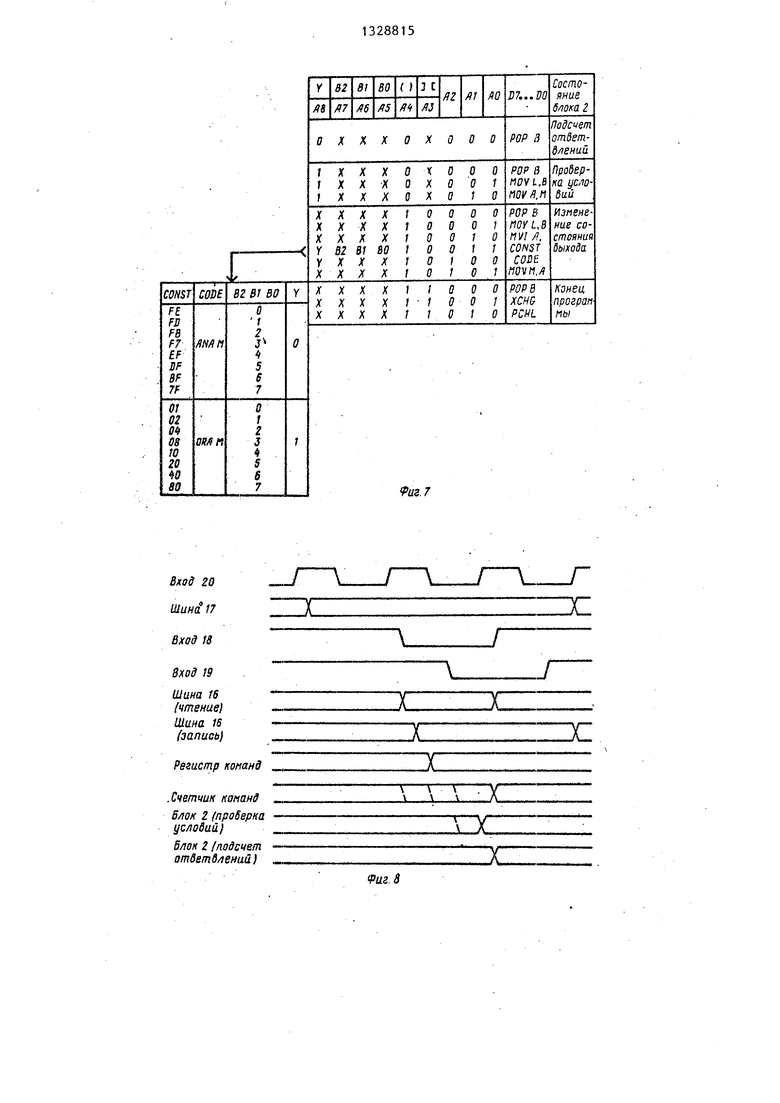

На фиг, 1 представлена схема блока Логической обработки; ка фиг 2 днональ ная схема блока .слеиия Ч2НИЯ бита логической функи.ии на урС В- ме стандарт.чых функционалы- ьж элеиен:- тов; а 3 - фyiIкциoнaJ:ьнaя с лемз. да1аифраторов на уровне стагщартных функционапьпых элементов; ка фиг, j, - с груктура программируемого контро: - Л2ра| на фиг. 5 - формат команд бло-- ка ло1 ической обработки; иг фиг, ( - конкретна нереключательная схема ( i видя лестничной диаграмак) ; на

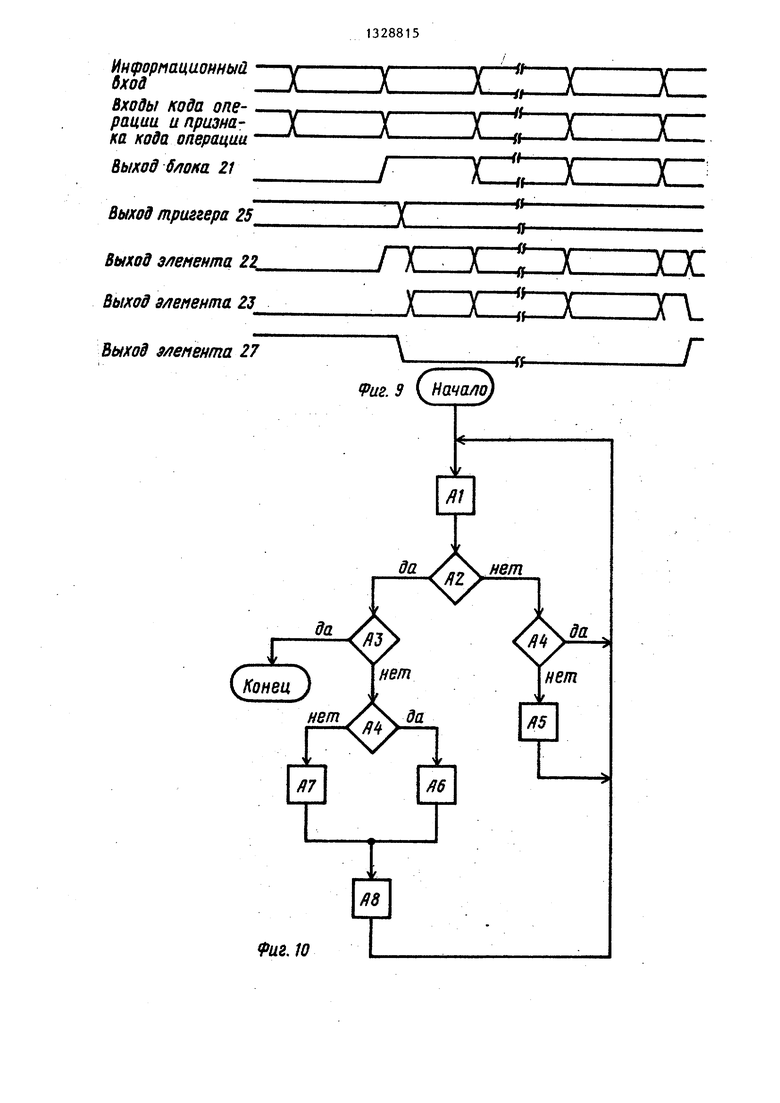

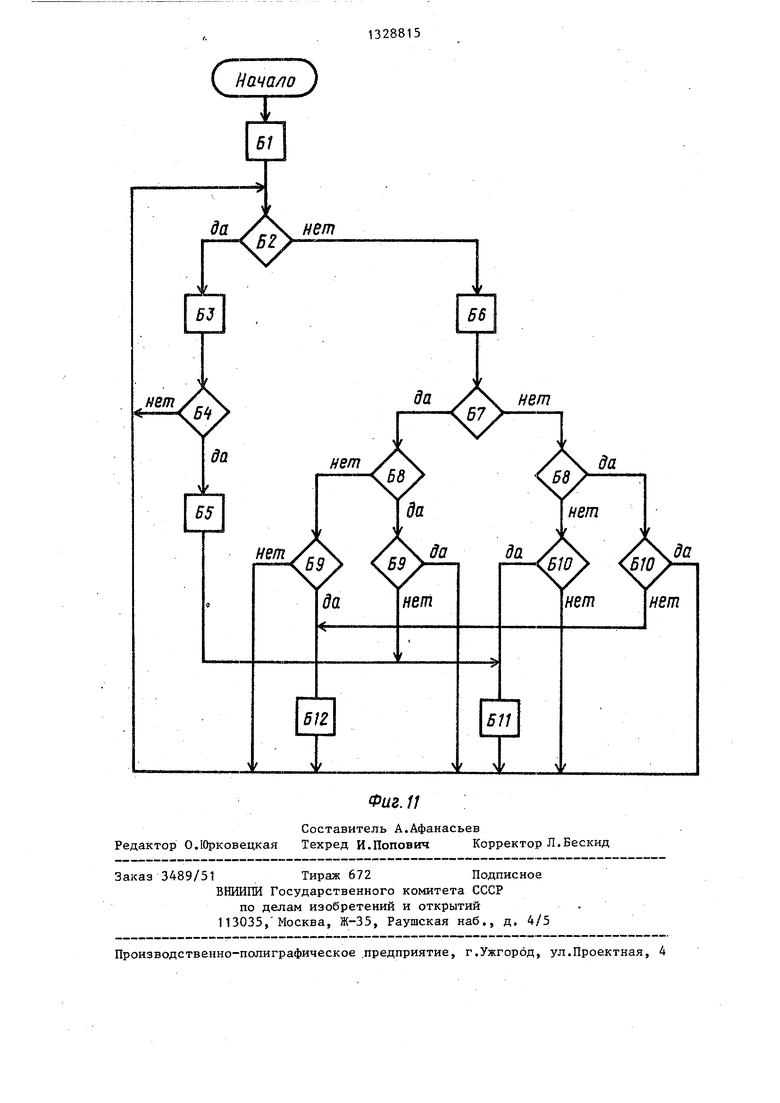

ческая V: О - логический X - б езр.а; личное состояг ие) , на фиг, 8 - 1гремсн;- ая диаграмма работы блока лог И- г;еской (Обработки; на 1Ьиг - времен- ная диаграмма работы блока вычислсгния з:-1аченл- Я бита логической функции; на (Ь -1Г- .I) - гиггсфлтм работь блока Л(:) ческой обработки (Л1 - счи /ать два байта команд;,; А2 проверить, ec i-ь ли об раб о гк а вывода; лЗ - г:ровери -ь, есть JH- конец программы; - ripoiie- piiTb состояние зькода блокг: на pajien- лю; А ;

порта I

я

- алгоритг-; работя

li

яец) ; блока

-веской функции - уетагювить сое- тояни : счетчика, oa.BHi;i i Б2 - проверить состояние счетчика на р;:-- венстно Б5 - установит ь значе-- ние .функции, разное - npoiie- рит-: .а.ейстзитехгьно ли значение арг у- мента совпадает со эначекиемз укаеан пьы на лестничной диаг рам - € , и есть ли отоетвление справа вниз; илл Ht совпадает н нет ответвления справг Б5 захюмнить лалргчие или от- r/yrcTBiie сигнала Ответвлекне справа вниз г, триггере; Б6 установить значение функцииj равным Б7 - проверить; зафиксировано ли в триггере ответвление сгфава внкз| Б8 - проверить наличие отве-твления справа вниз| Б9 - проверить наличие ответвления сгграва вверху Б10 - проверить

0

5

.а 11

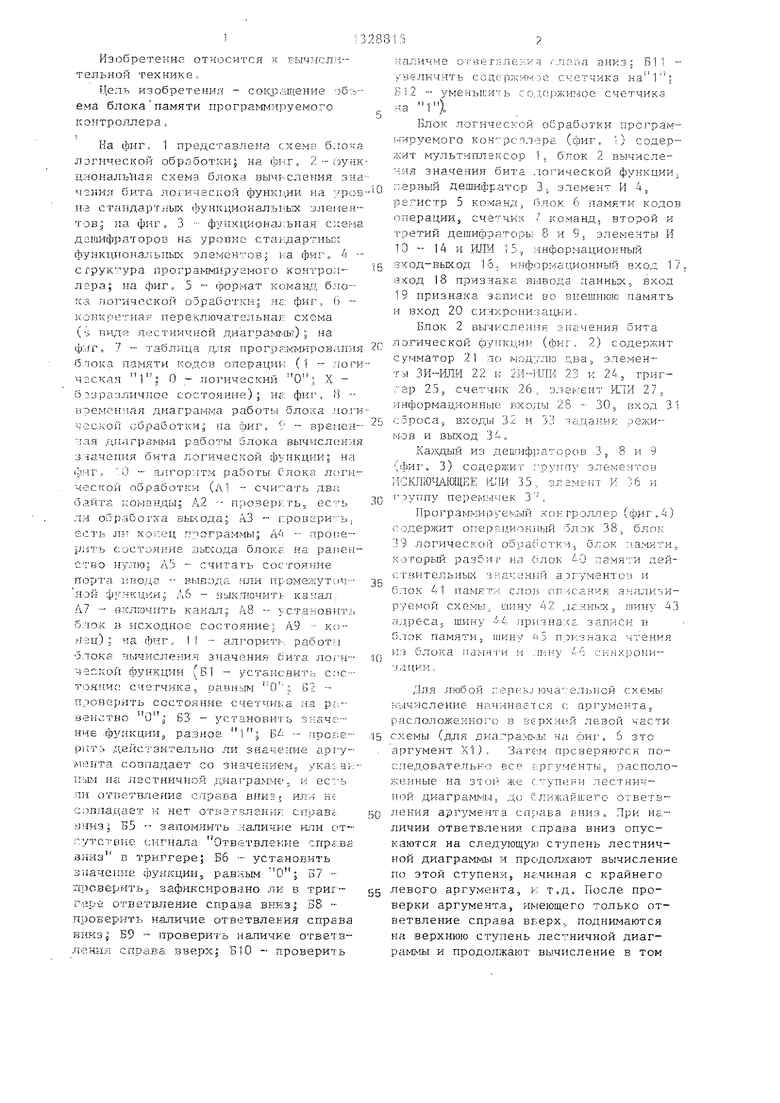

Блок логической обработки програм- | гируемого кон рсал гра (фиг, ) содержит мультиллексор 1 .. блок 2 вычисления значения бита .тогической функции: перзьш дешифратор 3 элемент И 4.. регистр 5 команд, блок 6 памяти кодов операции, счетчик / команд, второй и третий дешифраторь; 8 и 9, элементы И 0 - 14 и ИЛИ 15, информационный вход-выход 16, Ипфг)рмационный вход 17, вход 18 признака в :1зода даннь-х. вход 19 признака записи во внешнюю намять и вход 20 синкрони:;:ации„

Блок 2 вычислен - я значения бита логической фуггкцни Сфиг , 2J содержит сумматор 21 лс) мод:,лю c-is-a, элементы 22 V, 2И-ЧгПИ 23 и 24. триг- г ер 25. счетчик 26. элемент ИЛИ 27, ин формаи,ионн1з1е входы 28 - 30 „ вход 31 сброса, входы 32 и 33 зг дания режи-- мов и выход 34„

Каждый из дешиф1;аторов 3. 8 и 9 (с1)иг, 3) содержит ; руппу элементов ИСКЛЮ ШОЩЕЕ ИГГИ 35,, элемент И 36 и

5

Программир уе х:л Й кон гроллер (фиг . 4) содержит операционный блок 38,, блок 39 логической обработки, блок памяти, к ггорый разбит на блок О ламяч и дей- ствительньЕ-L зкачен ;1Й арг ументов и блок 41 намят:-; опмс;ания анализируемой схемь. айну 42 данных, иину 43 адреса, шину 4 ттризиака записи в б. юк памяти, тину признака чтения и;5 блока памяч И м ...1ину 46 ;;:инхро}П-1 зации.

5

0

D ЭТО

аргумент Х1)„ П15оверяются по- с.1едователько все с:ргу:4енть;5 расположенные на этой лге с.- ушгни лестничной диаграмма;., до С;;ия;айшего ответз-- ления аргумента справа яниз. Hpii наличии ответвления с:лрава вниз опускаются на следующую ступень лестничной диаграммы и продол хают вычисление по этой ступ.ен:и5 нг.чиная с крайнего левого аргумента, к т.д. После проверки аргумента, имеющего только ответвление справа вверх,, поднимаются на верхнюю ступень лестничкой диаграммы и продолжают вычр сление в том

313

же порядке.(На фиг. 6 все аргументы пронумерованы в порядке вычисления).

В начале вычисления значение функции (выход блока 2 вычисления значения бита логической функции) устанав ливается равным 1.

В процессе вычисления функция может принимать значение О в ц,вуу. случаях: если действительное значение аргумента, имеющего ответвление справа вниз, совпадает со значением аргумента, указанного на лестничной диаграмме, и значение функции при проверке предыдущего аргумента бьшо равно 1, или если действительное значение аргумента, не имеющего ответвления справа вниз, противоположн значению аргумента, указанного на лестничной диаграмме, и значе ие функции при проверке предь;;ту1цегс ар- гумента было равно 1,

В первом случае по наличию ответвления справа вниз обнаруживается дизъганктивнг 1й член для той части фупК ции, в которую входит пpoвepяe ьui аргумент, и установка значения О для функции (выхода блока 2) означает, что проверенный член дизъюнкции равен 1, следовател1,1ЮJ вся дизъ- юнкция paBria 1, и остается найти последний аргумент последнего члена дизъюнкции, после проверки которого функция вновь должна принять 3)1аче- ние

Для нахолсдения последнего аргумента последнего члена диз ьюнкции по ходу вычисления подсчитывается число ответвлений от аргументов справа вни и справа вверх. Kiar вычислений; в котором число ответвлений справа вверх превыьчает число ответглеиий справа вниз, указывает на последний аргумент последнего членасдизъюнкции При этом функ1;р-1я (выход блока 2) вновь принимает значение 1, и вычисление продолжается„

Во втором случае необходимо определить, имеет лVI часть функции, в которую входит только что проверенный аргумент, дизъюнктивный член. Для нахождения дизъюнктивного члена по ходу вычисления функции подсчитывается количество ответвлений от аргумента слева вниз и справа вниз. Шаг вычис- ления, в котором число ответвлений справа вниз превышает на 1 число ответвлений слева вниз, указывает на наличие дизъюнктивного члена в

154

ТС5Й части функции, которая приняла значение О. При этом в следующем шаге вычислений функция (выход блока 2) вновь принимает значение 1, и вычисление продолжается.

Описанный порядок и правила вычисления позволяют однозначно определит значение функций любой переключательной схемы.

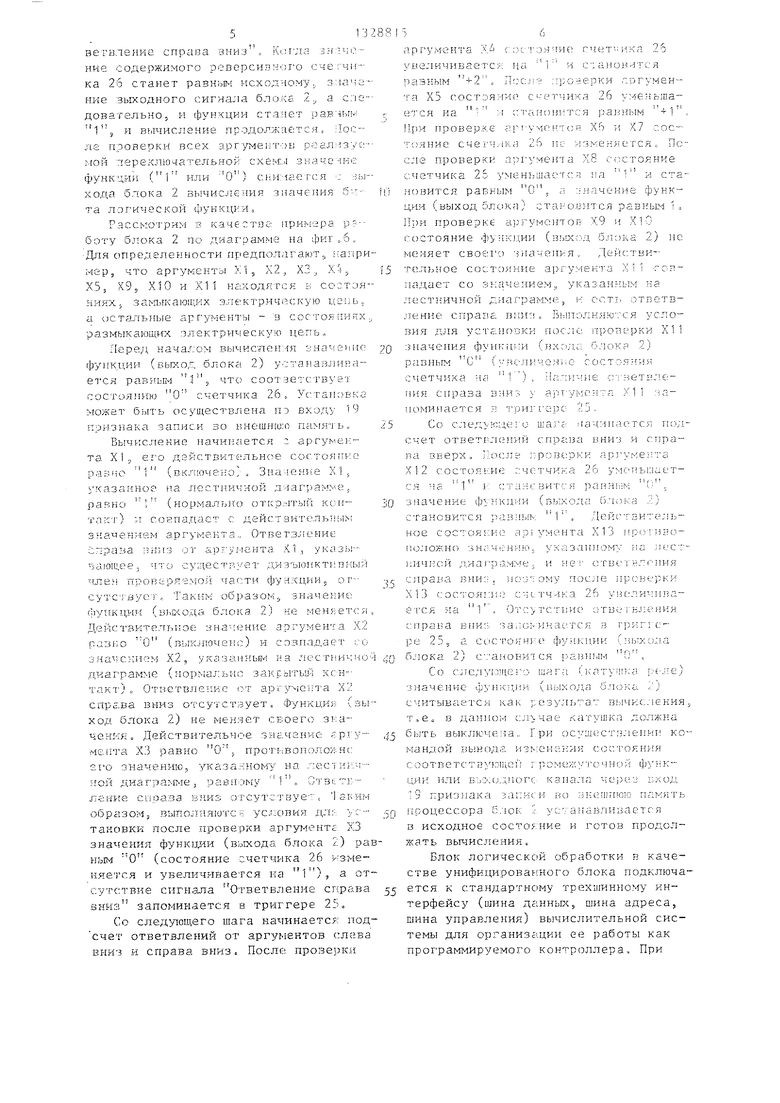

Блок 2 вычисления значения бита логической функции работает следующим образом (фиг. 9 и 11).

В начале вычисления счетчик 26 находится в исходном состоянии (содержимое равно О, значение выходного сигнала, а следовательно, и функции блока 2 1), В процессе вычисления последовательно по для каждого ар; у енга переключательной ;чатор 2 ло :чоду.аю два проверяет не- чс П ость сигналов: Значение аргумента, указанного на лестничной диаграмме, Действительное состояние аргу- мета, и 0 ГБС гв:1ение справа вниз. Если для ка,к огс-м ибо аргумента его де1:ствительное состояние совпадает с значен1 ел на лестг- дтчной диаграмме и -;у;еет ся сигнал Ответвление справа вниз, или ес.чи действительное состояние аргумента не совпадает со значением, указанным на лестничной диа- 1рамме, и отсутствует сигнал Ответвление справа вниз, то на выходе сумматора 21 по модулю два появляется сигнал, увеличивающий на 1 через элемент ЗИ-1-ПН 22 значение содержимого реверсивного счетчика 26, а значение сигнала Ответвление справа вниз запом11нается в триггере 25,

Когда значение содержимого ревер- српзного счетчика 26 становится отличным от исходного, то значение выходного сигнала блока 2, а следовательно, и функции становится равным О. При этом элементы ЗИ-11ТГИ 22 и 2И-11ЛИ 23 работают таким образом, что, если в триггер 25 было записано наличие сигна:аа Ответвление справа вниз, то на суммирующ1п 1 вход реверсивного счетчика 26 подается сигнал Ответв- :Ление спр-ава вниз и на вычитающий вход сигнал Ответвление справа вверх. Если в триггере 25 бьшо записано отсутствие сигна-па Ответвление справа вниз, то через элементы ЗИ- ИПИ 22 и 2И-11га-1 23 на суммирующий вход реверсивного счетчика 26 подается сигнал Ответвление слева вниз, а на вычитаю ций вход - сигнал От5132

вегвлерше справа вниз, idjivia ние содержимого оеверснвног о сче гч1г- ка 26 станет равным исходному. з: а и;-- нке выходного сигнала блоаэ. 2 , а c:ie--- довательно. функции станет равчьп 1 % и вычисление продолжается, Лес-- ле проверки всех аргументов реал тзч с- мой лереключательной схем.1 знaчe Ki;; функции (1 или О } ci-in:-iae гея с :5Ы-- хода блока 2 З1 числения значения б - та лог ической функцги

Рассьютрим в качест зе нримара боту блока 2 по диаграмме на фиг,6 Для определенности пг едполагают , например, что аргукенто Л ; Х2, ХЗ, Хч. Х5з Х9,, Х10 и XI I находятся в состояниях, зам1 гкаю1цих эль ктрическз ю цепь, а остальные аргументы - в состоя: инх., размыкак)аа-{х злектрическую цепь о

Перед началом вь1чиспенчя значеяие фуик11;ии (выход блока 2) У :;танавли ;а ется parUfbiM t , что соотзе гств ет

может быть осуществлена пэ Bxo;i,y 19 поизнака записи зо 1шешн и:о памя-ть.

Вычисление начин;1ется с аргумек-- та XI, ег о действительное состоя л;е ранило 1 (включено). Значение Х1, указагпюе на лестничной д-5аграм е, равно ; (нормалтли) опнф-ггый конзначением арг умента.. Ответвление С:лраза нниз от арг угчента К1, указы-- яаюш.ее, что сл ;деств:/ет дизъюиктипг ый чле г роверяе юй функции, or-- сутс вуегл 1 аким образом, значение ФУНКЦИИ ( блока 2J не меняется Дейс гвкте.ныюе значение аргумента Х2 раз1;о О (пьклгачен ;;) и совпадает г-о зна снием Х2, yKasai-iHbflvi на : естниччо диаграмме (норма1:ы-к:; закрытьи- ксн-- такт) .- Ответвление от аргу.|ента Х2 справа вниз отсутствует. Функция (выход блока 2) не мен. своего зка- . Действительчое значение оргу- мепта ХЗ равно 0 % протр вополойнс его значению, указанном:;; на .сестнг.ч- пой диаграмме. равнс:1му 1. U rstTi:- ление справа вниз о-гсутстауе ;д 1зким обрг13оМэ выполняютс::: ус.::овия дд;:; установки после проверки аргут- ентг X.J значения функш-1И (выхода блока 2) раным О (состояние с-четчика 26 изменяется и увеличивается на I), а o l сутс-.твне сигн.ала Ответвление справа вниз запоминается в тр иггере 25,

Со следующего шага мачинаетск под счет ответвлений от аргументов с:лева вниз и справа вниз. После проверки

R

56

аргумента Х. состояние счет-ика 26 уве:1ичивает сх Pia и C l аног -ггся павным + Псс:л ;1 ;озерки cvsrvMeH та Х5 ( остэя:- ие с - етчика 26 уменьшается иа н ;гтаноиится jjajii biM . При проверле ap y f к тoR Хо и Х7 состояние счегчнка 26 НС зменяется После проверки аргуме1гга Х8 С остоянке счетчика 25 уменьшается па i , гтации (выход блока; ;;та1-ойится р В1;ым , При проверке а гументов М и Х10 1:ч)стояние фуню.ши (вьосод блока 2) не меняет своего значения, Дей|;:тви- тельное состояние а1)гумен а Х11 -гсл- надает со 31-:ачением, указан-;ь м на лестничной диаграм е, и есть ответв5

БИЯ для устан;)вки пос-дс; проверки л значения функции (входа блока 2) равным С ( jiCjuniejinC состояни 1 счетчика на 1 ) , Иа. сг: ветвления справа i Htr у аг}туь:с; та XI 1 запоминается н тч иггерс ;:5Со следуилде: U шатд: нанинаотся подсчет ответЕ -1еиий спргизг вниз и сира- па вверх. Xocj;e проверки арт умента л12 с:остоя -:ие ::четчика 26 умсч1ы;1ает5

зиачение функции (выхода -:/ ста - овится ранны ., ГХ ДеЙ1 гаитель- ное состоянт С аргумента X13 (.1- положно зн,;:л1,, указанному на нес :-1 ИЧ1;ОЙ ;1.ИаГ р13. 5 и не: СГГВ ТНЛГН ИЯ

сирава 1г1и:: , iio:.} :iOMy nocjie проверки Xi3 сос гоя;:ие счетччка 26 у и:ли-н{ва- ется на Г , Отсутствие отвегкле П1Я снтрава вни;;. залоь нас тся в rpt:ri с- ре 25. а состояние функнтп- (н1);хон.а блока 2) c raiiOBJi i СИ paBHiiiH П Д

Со cjH:;ayij r(eHo 1иага Идггупнга г.;е.;;е) значение ( блокг; ,/) с итываетси как ;; езулв ат в;)1чис;ления. т.е в дан11о:м случае к ггушка должна б:нть выклю чеча,. Гри ocyiiiec HiHeJ Ki командой .а из :eвe;;;iя состоян1 я с о о Т в е т С т в у шпк: f l : р ом еж v т с ч н г) и фу н к - ЦИ1- или вьз-ладног с кана:та чс)ез вход :9 признака заггиси во пининюга память процессора блок ,L ус /анавливается в исходное cocTo.t ние и готов продолжать вычисления.

Блок логическс1Й обработки в качестве унифицированного блока подключается к стандартному трехшинному интерфейсу (пдина данных, шина адреса шина управления) вычислительной системы для организгщии ее работы как программируемого контрсэллера. При

этом конфигурация системы может быть такой, как указано на фиг, 4, где операционный блок 38 (микропроцессор) по шине 42 данных, шине 43 адреса и шине управления, включающей разряд j 44 признака записи во внешнюю память, разряд 45 признака чтения внешней па- ,мяти и разряд 46 тактовой частоты микропроцессора, подключен к блоку

щую последовательность для блока 39 логической обработки программа START: LXI SP, RUN MVI Н, ADR LXI D, START

MOV A, M,

MOV M, A IMP LOGPR Объем адресного пространства, за;39 логической обработки программируе-JO нимаемого блоком 39 логической обрамого контроллера и блокам 40. и 41 памяти.

Область ввода-вывода должна быть продублирована в блоке 40 памяти. Тогда блок 39 логической обработки при работе по переключательной схеме может осуществлять обмен информацией только с блоком 40 памяти, где непосредственно за продублированной областью ввода-вывода должна находить- ся область промежуточньсс функций.

Операционный блок 38 может быть реализован на микропроцессоре

КР580И80А. Представленные мнемонические названия команд для определенное-25 после чего содержимое счетчика 7 команд увеличивается на 1, подготавти .даны на языке Ассемблер указанного микропроцессора,. ливая для чтения следующую ячейку

Блок 41 памяти содержит команды блока 6 памяти кодов операции, Микро- для блока 39 логической обработки, процессор устанавливает на шине 43 определяющие работу программируемого зо адреса адрес младшего байта, читае- контроллера при реализации переключательных схем. Каждая команда (фиг. 5) содержит два байта. В старшем байте содержится адресная частв

могр из стека..Этот адрес через шину адреса внешней памяти процессора поступает на дешифратор 9 и с приходом сигнала чтения внешней памяти содер- команды. Младший байт содержит код жимое младшего байта команды записы- операции для блока 39 логической об- вается в регистр 5 команд (фиг. 8). работки,

; Программируемьй контроллер рабо- ;тает следующим образом.

Для инициализации блока 39 логической обработки необходимо устаноАдрес внешней памяти задается на дешифраторе 9 перемычками 37.

Затем микропроцессор заканчивает 40 чтение из области стека, после чего в паре регистров ВС оказывается команда блока 39 логической обработки. Далее, если в поле кода операции регистра 5 команд оказьшается код, совить указатель стека микропроцессора 38 на первую ячейку блока 41, с которой начинается последовательность

команд, описывающих переключательные 45 ответствующий концу программы, микросхемы, в регистр Н микропроцессора процессор последовательно выполняет ввести старшую часть адреса области команды XCHG и PCHL из блока 6 памя- ввода-вывода и промежуточных функций, ти и осуществляет деинициализацию в пару регистров DE ввести адрес воз- блока 39 логической обработки перехо- врата после вычисления всех логичес- 50 Дом по адресу, заданному в паре ре- ких функций, произвести операцию вы- гистров DE. вода (установку в исходное состояние блока 39 логической обработки), осуществить передачу управления в обЕсли в поле кода операции регистра 5 команд оказывается код, соответствующий проверке аргумента (открыласть адресного пространства внешней тый или закрытьй контакт), и выход памяти, занимаемой блоком 39 логичес- блока 2 находится в состоянии логикой обработки (указанная область определяется набором перемычек 37 дешифратора 8), Реализует инициализируюческой 1 , микропроцессор последовательно вьшолняет команды из блока памяти MOV L,В (формирование адреса

щую последовательность для блока логической обработки программа START: LXI SP, RUN MVI Н, ADR LXI D, START

MOV A, M

MOV M, A IMP LOGPR Объем адресного пространства, ботки, должен быть достаточным для отработки всех команд, описывающих переключательные схемы, В обычном случае этот объем не превышает 16 кбайт.

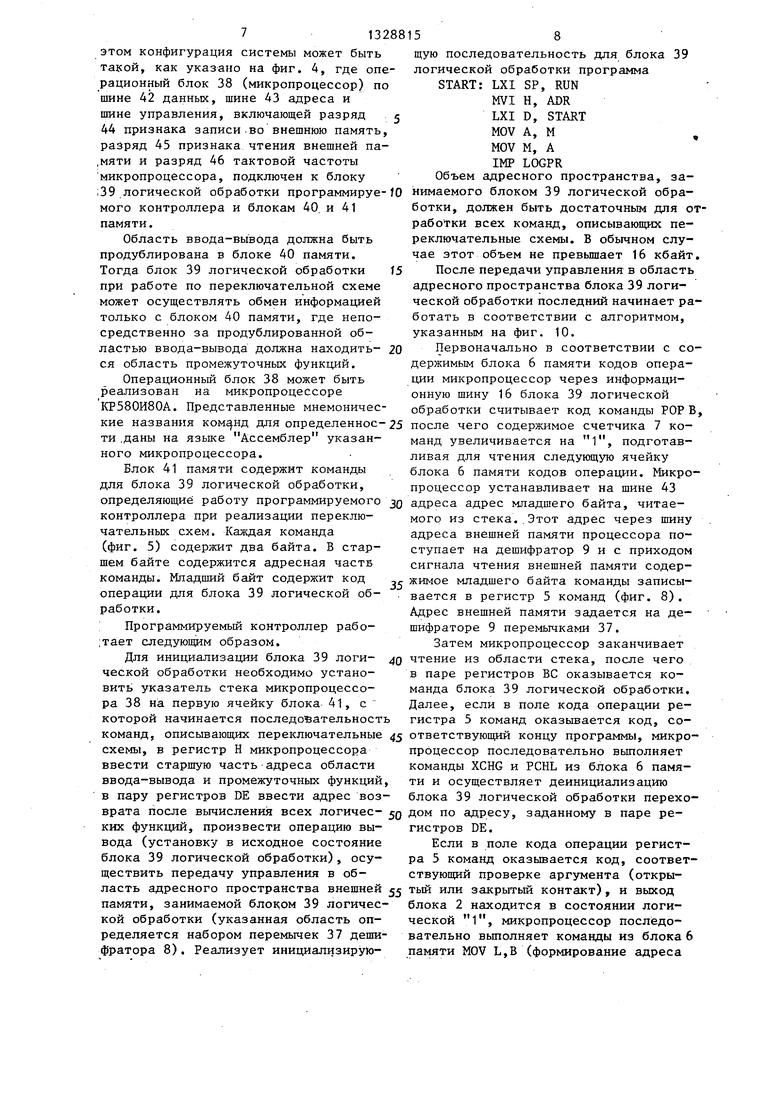

После передачи управления в область адресного пространства блока 39 логической обработки последний начинает работать в соответствии с алгоритмом, указанным на фиг. 10.

Первоначально в соответствии с содержимым блока 6 памяти кодов операции микропроцессор через информационную шину 16 блока 39 логической обработки считывает код команды POP В,

могр из стека..Этот адрес через шину адреса внешней памяти процессора поступает на дешифратор 9 и с приходом сигнала чтения внешней памяти содер- жимое младшего байта команды записы- вается в регистр 5 команд (фиг. 8).

Адрес внешней памяти задается на дешифраторе 9 перемычками 37.

Затем микропроцессор заканчивает 40 чтение из области стека, после чего в паре регистров ВС оказывается команда блока 39 логической обработки. Далее, если в поле кода операции регистра 5 команд оказьшается код, соответствующий концу программы, микропроцессор последовательно выполняет команды XCHG и PCHL из блока 6 памя- ти и осуществляет деинициализацию блока 39 логической обработки перехо- Дом по адресу, заданному в паре ре- гистров DE.

Если в поле кода операции регистра 5 команд оказывается код, соответствующий проверке аргумента (открытый или закрытьй контакт), и выход блока 2 находится в состоянии логической 1 , микропроцессор последовательно вьшолняет команды из блока 6 памяти MOV L,В (формирование адреса

9132

анализируемого логического условия) и MOV А, М (проверка логического условия) .

При вьтолнении микропроцессором операции чтения анализируемого байта осуществляется переключение (при необходимости) реверсивного счетчика 26 по сигналу с дешифратора 3 ввода-вывода. Адрес ввода-вывода задается на дешифраторе 3 перемычками 37. За- тем счетчик 7 у. обнуляется, и указанный цикл повторяется.

Если в поле кода операции регистра 5 команд оказывается код, соответствующий проверке аргумента, и выход блока 2 находится в. состоянии логического О при чтении микропроцессором старшего байта команды из стека, осуществляются сначала сброс счетчика 7 команд, а затем йереключение реверсивного счетчика 26.

Если в поле кода операции регистра 5 команд оказывается код, соответ- ствуюнщй обработке вьжода (катушка реле), микропроцессор последователь- но выполняет команды MOV L,B и MVI А, CONST,

Причем значение CONST выбирается в зависимости от состояния выхода блока , 2 вычисления значения бита логи ческой функции и состояния поля номера кода операции регистра 5 команд. Затем, если состояние выхода блока 2 соответствует логическому О, микропроцессор выполняет команду ANA М, в противном случае - ОКА М, После этого результат вычислений оказывается в аккумуляторе микропроцессора, и цикл заканчивается выполнением команды MOV М,А. На,фиг. 7 в таблице для константы CONST ее значение указано в шестнадцатеричной системе счисления.

Формула изобретения

Программируемый контроллер, содер- . жащий операционный блок, блок логической обработки и блок памяти, информа- ционньй вход-выход которого соединен с информационными входами-выходами операционного блока и блока логической обработки, информационный вход которого соединен с информационным выходом операционного блока и адресным входом блока памяти, вход управления чтением которого соединен с выходом признака ввода данных операционного блока и с входом признака вывода дан510

ных блока логической обработки, вход признака ввода чданных которого соединен с входом управления записью блока памяти и входом признака вывода данных операционного блока, выход синхронизации которого соединен с входами синхронизации блока логической обработки и блока памяти, причем блок логической обработки содержит мультиплексор, первьм дешифратор, первый элемент И, сумматор по модулю два, триггер, первый элемент 2И-ИПИ и элемент ЗИ-Ш1И, счетчик и первый элемент ИЛИ-НЕ, выход которого соединен с синхровходом триггера, с первым и вторым инверсными входами первого элемента 2И-Ш1И и с первым и вторым инверсными, с первым прямым входами элемента ЗИ-ИПИ, вькоды элемента ЗИ- ИЛИ и первого элемента 2И-ИЛИ соединены соответственно с суммирующим и вычитающим входами счетчика, выход которого соединен с входом первого элемента ИЛИ, выход триггера соединен с третьим инверсным и первым прямым входами первого элемента 2И-РШИ и с третьим инверсным и вторым прямым входами элемента ЗИ-ИЛИ, первый вход и выход сумматора по модулю два соединены соответственно с выходом мультиплексора и третьим прямым входом элемента ЗИ-ИЛИ, информационный вход- выход блока логической обработки соединен с информационным входом мультиплексора, входы признака вывода и признака ввода данных блока логической обработки соединены соответственно с первым и вторым инверсными входами первого элемента И, вход блока логической обработки соединен с входом первого дешифратора, выход которого соединен с прямым входом первого элемента И, отличающийся тем, что, с целью сокращения объема блока памяти программируемого контроллера, блок логической обработки содержит с второго по шестой элементы И, второй дешифратор, третий дешифратор, регистр команд, счетчик команд, блок памяти кодов операций, второй элемент ИЛИ, второй элемент 2И-ИЛИ, выход которого соединен с синхровходом счетчика, вход установки в О которого соединен с инверсным входом второго элемента ИЛИ и входом признака ввода данных блока логической обработки, информационный вход-выход которого соединен с выходом блока памяти кодов операций и с информационным

. входом регистра команд, выход счетчика- команд, выход поля кода операции и номера кода операции, регистра команд и выход первого элемента ИЛИ соединены с группой адресных входов блока памяти кодов операции, выход младшего разряда поля кода операции регистра команд соединен с вторыми инверсными входами второго элемента 2И-ИЛИ и с первыми инверсными входами четвертого и пятого элементов И, выходы которых соединены с первым и вторьм прямыми входами второго элемента ИЛИ, выход которого соединен с входом установки в О счетчика команд, нулевой разряд выхода которого соединен с первыми прямыми входами четвертого и пятого элементов И, второй прямой вход которого соединен с первым разрядом выхода счетчика команд, вход синхронизации которого соединен с вторым инверсным входом пятого и выходом шестого элементов И и с входом разрешения чтения блока памяти кодов операций, информационный вход блока логической обработки соединен с входами второго и третьего дешифраторов, выход которого сое«динен с прямым входом шестого элемента И, инверсный вход которого соединен с первым инверсным входом второго и первым входом третьего элементов И и с входом призцака вывода данных блока логической обработки, выход первого элемента И соединен с первым прямым входом второго элемента 2И- ШШ, второй прямой и третий инверсный

.входы которого соединены с выходом

1

10

15

32881512

первого элемента ИЛИ, с синхровходом триггера и вторым инверсным входом четвертого элемента И, второй прямой вход которого соединен с третьим прямым входом второго элемента 2И-ИЛИ и с выходом второго элемента И, первый прямой вход которого соединен с младшим разрядом информационного входа блока логической обработки и вторым входом третьего элемента И, третий вход которого соединен с вторым входом второго элемента И и с выходом третьего дешифратора, четвертый вход третьего элемента И соединен с входом синхронизации блока логической обработки и.с третьим инверсным входом пятого элемента И, выход третьего элемента И соединен с входом синхронизации регистра команд, выход старшего разряда поля кода операции регистра команд соединен с вторым входом сумматора по модулю два, выход младшего разряда поля признака кода операции регистра команд соединен с третьим входом сумматора по модулю два, с третьим прямым входом элемента ЗИ-ШЖ и вторым прямым входом первого элемента 2И-ШШ, и с информационным входом триггера, выходы старшего и среднего разрядов поля признака кода операции регистра команд соединены соответственно с третьим прямым входом первого элемента 2И-ШШ и с четвертьм прямым входом первого элемента 2И-ИПИ, выход поля номера кода операции регистра команд соединен с управляющим входом мультиплексора.

20

25

30

35

)6

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор программируемого контроллера | 1984 |

|

SU1269150A1 |

| Устройство для подсчета числа ответвлений диаграммы | 1983 |

|

SU1160391A1 |

| Устройство для программной реали-зАции пЕРЕКлючАТЕльНыХ CXEM | 1978 |

|

SU813413A1 |

| Специализированный процессор для вычисления элементарных функций | 1985 |

|

SU1330627A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1681297A1 |

| Программируемый контроллер | 1987 |

|

SU1448338A1 |

| Программируемый контроллер | 1985 |

|

SU1352484A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Многоканальное операционное устройство | 1982 |

|

SU1124292A1 |

| ВЫЧИСЛИТЕЛЬНАЯ ОТКРЫТАЯ РАЗВИВАЕМАЯ АСИНХРОННАЯ МОДУЛЬНАЯ СИСТЕМА | 2009 |

|

RU2453910C2 |

Изобретение относится к области вычислительной техники и может быть использовано в системах контроля, .Цель изобретения - сокращение объема блока памяти программируемого контроллера, Программируемьв1 контроллер содержит операционньй блок, блок ло- гргческой обработки и блок памяти. Введение в блок логической обработки двух дешифраторов, регистра команд, счетчика команд, блока памяти кодов операций, пяти элементов И, элемента ИЛ1-1 и элемента 2H-PfflIi приводит к достижению цели, 11 ил.

Фиг. 2

u,

п

M/tadtuuu Saum

Номер KoSa one- Поле признакаполе кода

рации кода oaefanuuоперации

D7 US V5 0 D3 0201 SO

cnpaSa бниз

Старший Вайт D7 D6 D5 J4 JJ Бг 27/ БО

Но ft ер порта SSoda-быбода a/iu промежуточной (рунпции

О- SSsd-быЗод

I - пропежуточная фунщия

Риг. 5

J С - Норма/}ьно открытый контакт з/с - Нормально закрытый контакт ( ) - Катушка pe/fe

Вход го Шин/17

Вход 18

Вход 19

Шина 16 (чтение Шина 16 (запись)

Регистр конанд

.Счетчик команд

S/JOK 2 (проберка услобий)

блок 2 /подсчет ответв/ieHuu)

И

Л

- V

Редактор ОЛОрковецкая

Фиг. 11 .

Составитель А.Афанасьев

Техред И.Попович Корректор Л.Бескид

Заказ 3489/51 Тираж 672Подписное

ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий

113035, Москва, Ж-35, Раушская наб., д, 4/5

Производственно-полиграфическое предприятие, г.Ужгород, ул.Проектная, 4

| Патент США № 4303990, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Процессор программируемого контроллера | 1984 |

|

SU1269150A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1987-08-07—Публикация

1986-03-07—Подача