Изобретение относится к автоматике и вычислительной технике и может быть применено в цифровах вычислительных машинах и устройствах дискретной автсяиатики, работающих в избыточной системе счисления.

Известно устройство для сравнения чисел, содержащее блок вычитания сумматор, триггеры, элементы И, коммутаторы, сумматор по модулю два, узел управления l .

Недостатком этого устройства является невозможность сравнения чисел представленных избыточных кодом. .

Наиболее близким техническим решением к предлагаемому является устройство для сравнения чисел, содержащее блок вычитания, сумматор, два элемента И, сумматор по модулю два, триггеры, коммутаторы, узел управления, в котором входы блока вычитания соединены с шинами операндов, а его прямой и инверсный выходы старшего разряда подключены ко входам первого и второго элементов И соответственно и к информационным входам первого триггера, выходы которого соединены с одним из входов первого и второго элементов И и с управляющими входами первого коммутатора, информационные входы которого подключены к шинам операндов, а выходы к одним из входов сумматора, другие входы которого соединены с выходами второго коммутатора, информационные входы которого подключены к выходам блока вычитания, а управляющие входы - к выходам первого и второго элементов И, один из входов которых

0 соединен с выходом второго триггера и со входом узла управления, другие входы которого подключены к шинам управления и шинам та стовых сигналов, а выходы - ко входам блока вычитания, выходы второго и третьего разрядов которого соединены со входами сумматора по модулю два, управляющий вход которого подключен к шине тактовых сигналов, а выход - ко входу второго триггера Гз.

0

Недостатком известного устройства, является недостаточное быстродействие, так как каждый цикл сравнения чисел содержит три такта работы устройства.

Цель изобретения - увеличение быстродействия устройства.

Поставленная цель достигается тем, что в устройство для сравнения

0 чисел, содержащее триггеры, элементы

И, сумматор, коммутатор, блок вычитания, входы которого, соединены с входными шинами операндов, первый и второй выходы которого подключены к первому и второму входам коммутатора и к первым входам первого и второго элементов И соответственно, инверсные выходы первого и второго триггеров соединены со вторыми входами второго и первого элементов И соответственно, первый и второй выходы коммутатора подключены к первому и второму входам cyzvMaTopa, выходы которого соединены с выходными шинами большего и меньшего чисел введены третий элемент И и регистры сдвига, причем выходы -первого и второго элементов И соединены со счетными входами первого и второго триггеров соответственно, инверсные выходы которых подключены ко входам третьего элемента И, прямые выходы первого и второго триггеров соединены с третьим и четвертым входами коммутатора, управляющие входы которого подключены к управляющим шинам, первая и вторая шины первого операнда соединены со входами первого и второго регистров сдвига соответственно, выходы которых подключены к третьему и четвертому входам суд-матора..

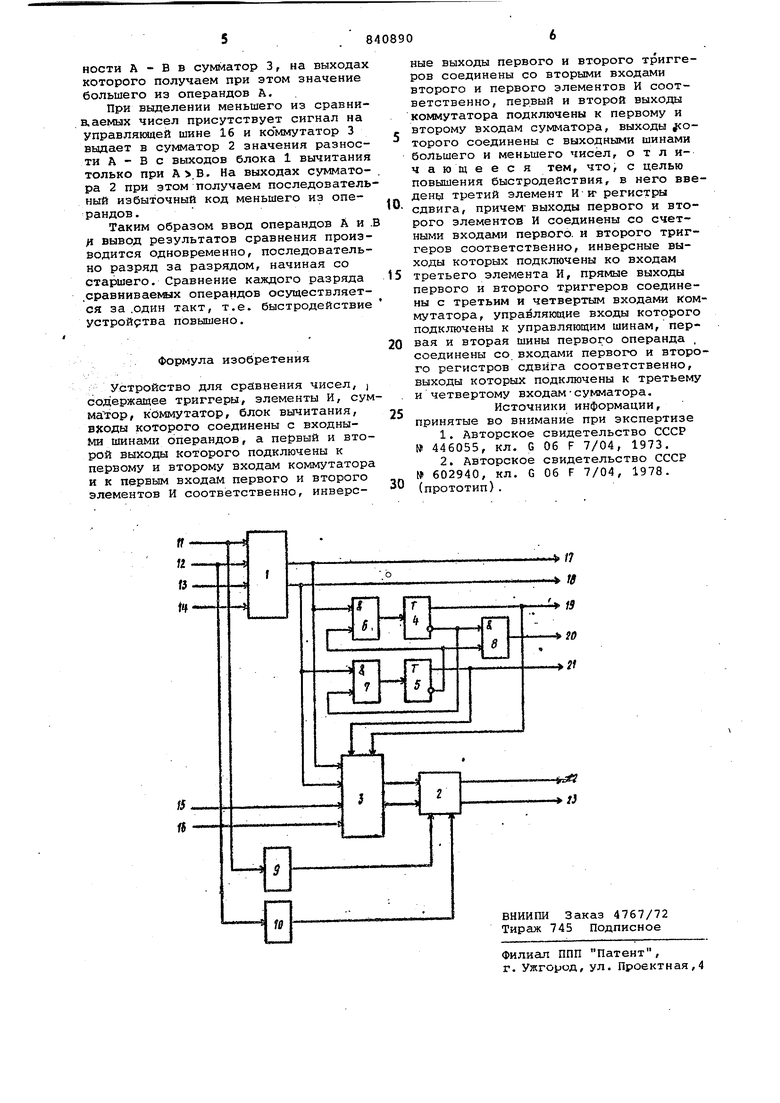

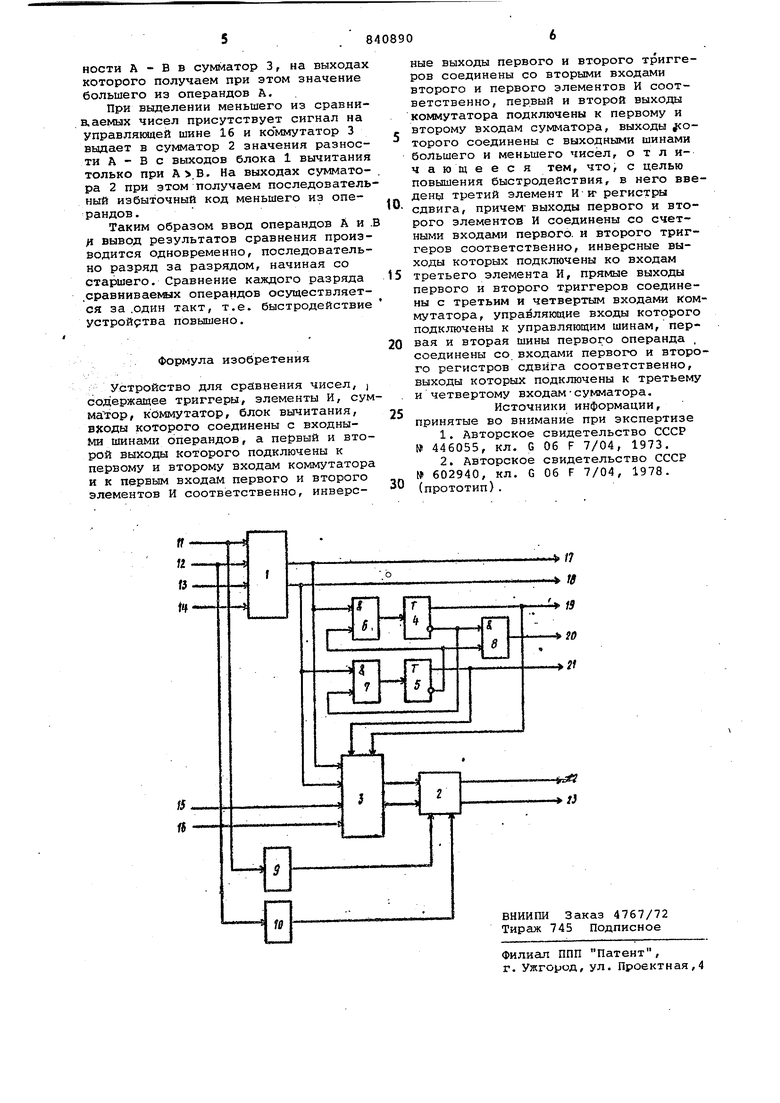

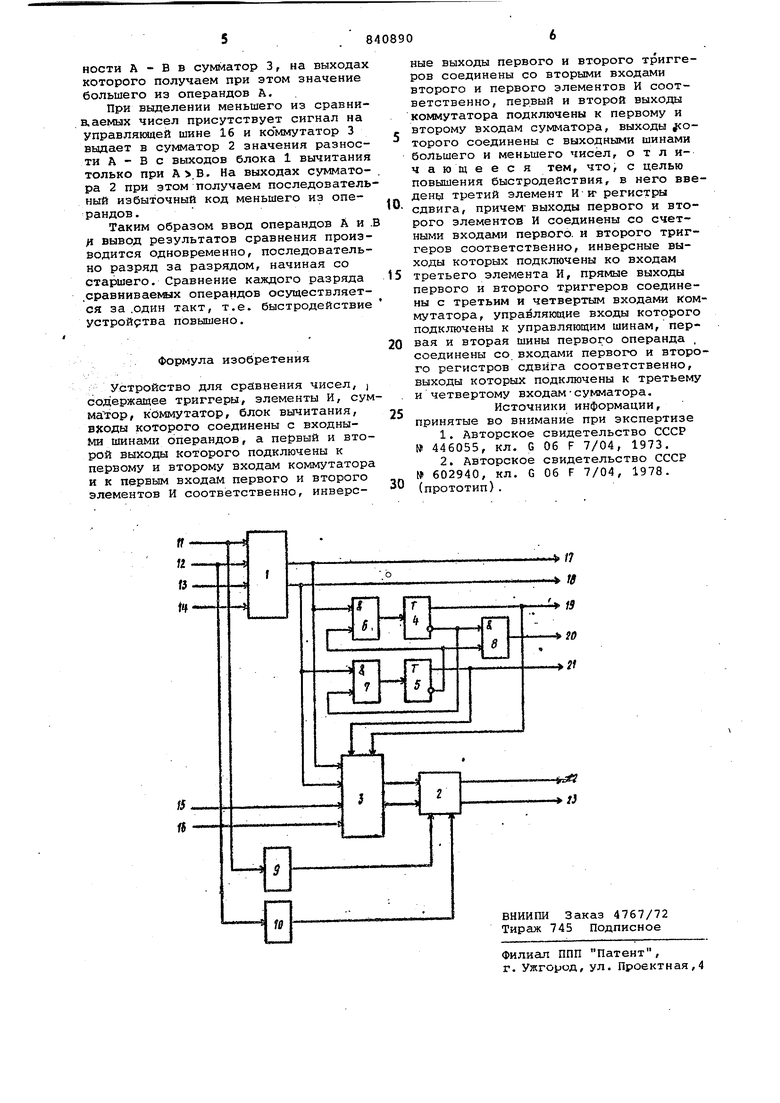

На чертеже представлена функцио-; нальная схемй предлагаемого устройства .

Устройство содержит блок 1 вычитания, сумматор 2, коммутатор 3, триггеры 4 и 5, элементы И 6, 7, 8, регистры 9 и 10 сдвига, шины 11 и 12 первого операнда, шины 13 и 14 второго операнда, управляющие шины 15 и 16, выходные шикы 17 и 18 разнос,ти, выходную шину 19 сигнала А В, выходную шину 20 сигнала А В, выходную шину 21 сигнала А В и выходные шины 22 и 23 большего или меньшего чисел.

Устройство работает следующим образом.

Код первого операнда А и код второго операнда В поступают поразрядно на шины 11-14 одновременно, т.е. в каждый такт работы устройства на шины поступают разряды первого и .второго операндов с одинаковыми весами В исходном состоянии блок вычитания .1, -сумматор 2, регистры 9 и 10 сдвига и зриггеры 4 и 5 установлены в нулевое состояние. Если необходимо определить максимальное из чисел, то на управляющую шину 15 поступает сигнал, который подается на управляющий вход коммутатора 3. Этот сигнал сохраняет свое значение до окончания работы устройства. Если необходимо определить минимальное из чисел, то сигнал поступает на шину 16.

В каждом такте сравнеьзия на шины 11 и 13 поступают положительные значения очередных разрядов, начиная

со старшего п-го разряда, операндов А и В, а на шины 12 и 14 - отрицательные значения. Блок вычитания 1 производит вычисление разности А - В путем последовательного суммирования в избыточной двоичной системе счисления операнда 4 и взятого с обратным знаком операнда В. На выходах блока вычитания образуется последовательный избыточный код разности А - В, положительные значения которой подаются на выходную шину 17 устройства и на первый вход элемента И б, а отрицательные значения подаются на выходную шину 18 устройства и на первый вход элемента И 7. Если операнд А болыае операнда В, то первая значащая единица разности с положительного выхода блока вычитания 1 проходит через элемент И б и перебрасывает триггер 4 в единичное состояние . С выхода триггера 4 сигнал Л В поступает на выходную шину 19 устройства и на один из управляющих входов коммутатора 3. Если, же операн А меньше операнда В, то первая значащая единица разности с отрицательного выхода блока 1 вычитания проходит через элемент И 7 и перебрасывает в единичное состояние триггера 5, с выхода которого сигнал А . Б поступает на выходную шику 21 устройства и на второй управляющий вход коммутатора 3. Одновременно сигналы с инверсньзх выходов триггера 4 или 5 запирают- входы элементов И 7 и 6 соответств.енно. при равенстве оп.ерандов по окончании цикла сравнения с выхода элемента И 8 снимается сигнал А В, который подается на выходную шину 20 устройства..

При выделении максимального из сравниваемых чисел, присутствует сигнал на управляющей шине 15 и отсутствует сигнал на управляющей шине 16. При А В коммутатор 3 подает на первый положительный и на первый отрицательный входы сумматора 2 соответственно отрицательное и положителное значение разности А - В с выходов блока 1 вычитания. На вторые положительный и отрицательный входы сумматора 2 через регистры сдвига 9и 10 подаются соответственно положительное и отрицательное значения первого операнда А с входных шин 11 и 12. Сумматор 2 производит сложение операнда А с разностью А - В в избыточной двоичной системе счисления и Ёыдает на шины 22 и 23 последовательно разряд за разрядом, начиная со старшего разряда, значениебольшего операнда, т.е. значение второго операнда В. Регистры 9 и 10 сдвига служат для компенсации временной задержки блока 1 вычитания, т,е; согласования весов разрядов операнда А и разности А - В. При А В или А В коммутатор 3 не выдает значения разности А - в в сумматор 3, на выходах которого получаем при этом значение большего из операндов А. При вьвделении меньшего из сравниааемых чисел присутствует сигнал на управляюцей шине 16 и коммутатор 3 выдает в сумматор 2 значения разности А - В с выходов блока 1 вычитания только при А.В. На выходах сумматора 2 при этом получаем последователь ный избыточный код меньшего из операндов . Таким образом ввод операндов А и ft вывод результатов сравнения производится одновременно, последовательно разряд за разрядом, начиная со старшего. Сравнение каикдого разряда .сравниваемых операндов осуществляется за .один такт, т.е. быстродействие устройства повышено. Формула изобретения Устройство для сравнения чисел, ) содержащее триггеры, элементы И, сум матор, коммутатор, блок вычитания, входы которого соединены с входными шинами операндов , а первый и второй выходы которого подключены к первому и второму входам коммутатора и к первым входам первого и второго элементов И соответственно, инверсные выходы первого и второго триггеров соединены со вторыми входами второго и первого элементов И соответственно, первый и второй выходы коммутатора подключены к первому и второму входам сумматора, выходы i oторого соединены с выходными шинами большего и меньшего чисел, отличающееся тем, что, с целью повышения быстродействия, в него введены третий элемент Ий- регистры сдвига, причем- выходы первого и второго элементов И соединены со счетными входами первого, и второго триггеров соответственно, инверсные выходы которых подключены ко входам третьего элемента И, прямые выходы первого и второго триггеров соединены с третьим и четвертым входами коммутатора, управляющие входы которого подключены к управляющим шинам,первая и вторая шины первого операнда соединены со входами первого и второго регистров сдвига соответственно, выходы которых подк.шочены к третьему и четвертому входамсумматора. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР № 446055, кл. G 06 F 7/04, 1973. 2.Авторское свидетельство СССР № 602940, кл. G 06 F 7/04, 1978. (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Последовательное арифметическое устройство | 1974 |

|

SU528565A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| УСТРОЙСТВО ВЫРАВНИВАНИЯ ПОРЯДКОВ ОПЕРАНДОВ | 1992 |

|

RU2006910C1 |

| Устройство для умножения двоичных чисел | 1980 |

|

SU981996A1 |

| Устройство для быстрого преобразования фурье | 1981 |

|

SU1018123A1 |

| Устройство для сравнения чисел | 1976 |

|

SU602940A1 |

| Арифметико-логическое устройство | 1983 |

|

SU1176321A1 |

| Суммирующее устройство с плавающей запятой | 1982 |

|

SU1056182A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1985 |

|

SU1315969A1 |

| Устройство для реализации алгоритма Волдера | 1983 |

|

SU1115049A1 |

Авторы

Даты

1981-06-23—Публикация

1979-09-26—Подача