(54) УСТРОЙСТВО ДЛЯ .СРАВНЕНИЯ ЧИСЕЛ

на тины 11 и 12 одновременно, то есть в каждый момент времени на шнны поступают разряды.первого и второго операндов с одинаковыми весами.

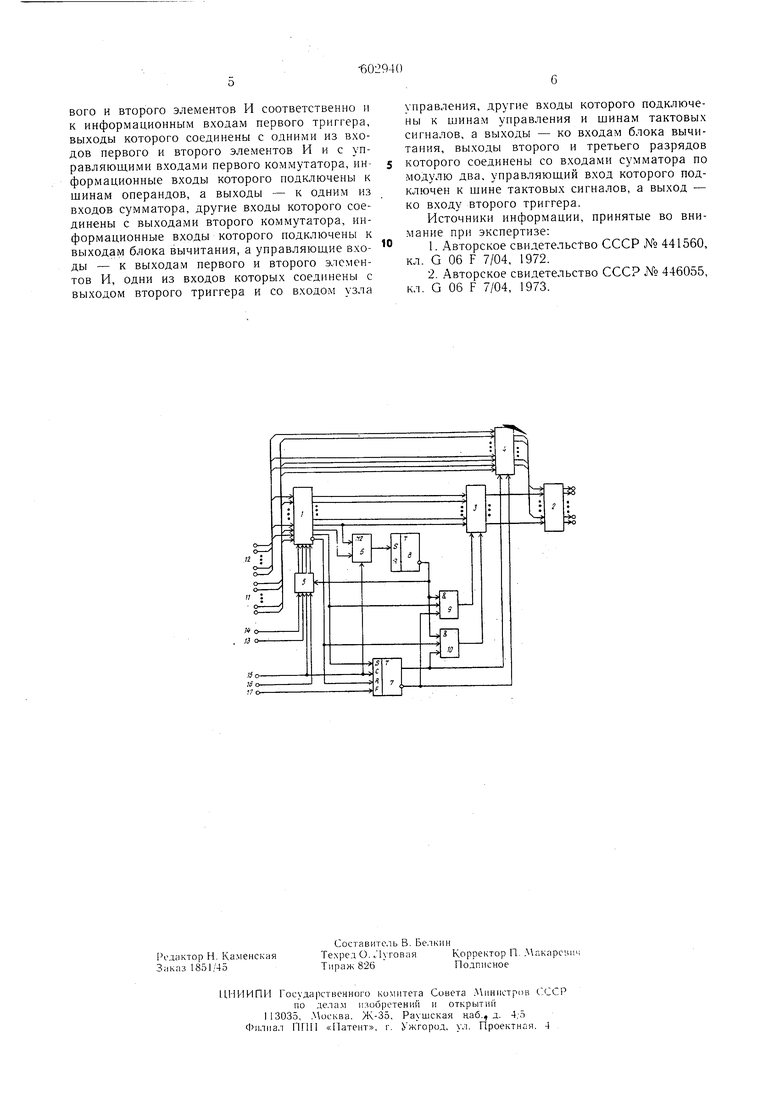

В исходном состоянии блок вычитания и триггеры устройства установлены в нулевое состояние. Если необходимо определить максимальное из двух чисел, то к началу первого цикла вычислений поступает сигнал на шину 13 и через узел управления 5 поступает на пеиь выдачи прямого кода старшего разряда блока вычитания I. Этот сигнал сохраняет свое значение до окончания работы устройства. Таким образом на выходах старшего разряда блока вычитания 1 до окончания работы устройства присутствует прямой код старшего разряда блока вычитания. Если необходимо определит, минимальное из двух чисел, то аналогичньп сигнал подается на шину 14 и через узел управления 5 поступает на цепь выдачи обратного кода CTapinero разряда блока вычитания 1. К началу каждого i-ro цикла вычислений (1 1, 2,..., т), на шины 11 и 12 поступают коды очередных разрядов соответственно а/ и в,, которые сохраняют свое значение до окончания цикла вычислений. В каждом цикле вычислений на тактовые шины 15, 16 и 17 поочередно поступают соответственно тактовые сигналы Yi 2 и Y.J- В перво.м такте цикла вычислений тактовый сигнал с шины 15 поступает на цепь приема кода триггера 7, на управляюииш вход сумматора по модулю два 6 и через узел управления 5 на цепь сдвига блока вычитания 1. При этом происходит прием в триггер 7 кода с выхода старше о разряда блока вычитания 1 (запоминание знака предыдуш.его остатка), суммирование сумматором 6 второго и третьего разрядов блока вычитания 1 и сдвиг содержимого блока вычитания 1 на один разряд влево (одновременный прием кода с блока вычитания 1, анализ разрядов этого блока и сдвиг содержимого блока возможны, так как блок вычнтания 1 является едвигаюшим, а следовательно, каждый разряд блока вычитания 1 должен быть построен на паре триггеров или на триггерах с внутренней задержкой).

Предположим, что в результате суммирования сигнал на выходе сум.матора 6 не появился. В этом случае триггер 8 не изменяет своего исходного состояния. Тогда во втором такте цикла вычислений с шины 16 поступает сигнал на вход узла управления 5, со второго выхода которого поступает сигнал на цепь приема кода блока вычитания 1. В результате этого к содержимому блока вычитания 1 ирибавляетея код разряда а. первого операнда н вычитается код разряда 5/ второго операнда. В третьем такте вычислений с тактовой шины 17 поступает сигнал на цепь выдачи кода триггера 7. В результате этого, в зависимости от еостояния триггера 7 и кода на В1з1ходе старшего разряда блока вычитания (то есть, в зависимости от предыдущего и настоящего знаков остатка), в сумматор 2 через коммутатор 4 передается код разряда а. или кол разряда 0,, а через коммутатор 3 по cnina.iaM с

выходов элементов И 9 и 10 передается соответственно обратный или прямой код с iibixoдов блока вычитания 1, или же при отсутствии сигналов на выходах эле.ментовИ 9 и 10 этот код 5 не передается. При этом, если триггер 7 и код на выходе старшего разряда блока вычнтания 1 имеют значение О, то через коммутатор 4 передается код а/, а через коммутатор 3 код не передается. Если их состояние соответственно О и 1, то коммутатор 4 передает код а,-, а коммутатор 3 - инверсный код блока вычитания 1. Для состояний соответственно 1 и О коммутатор 4 передает код в;, а ком.мутатор 3 - прямой код блока вычитания 1. В результате этого Аа выходе сумматора 2 появляется код разряда С; операнда результата.

Предположим теперь, что в первом такте вычислений в результате суммирования сумматором 6 второго и третьего разрядов блока вычитания 1 на выходе сумматора 6 появился сигнал. Это означает, что разность между числами настолько велика, что последующие разряды не могут изменить соотношения между числами. Поэтому нет необходимости вести вычисления в блоке вычитания 1, а достаточно передавать коды разрядов соответствующего

5 операнда прямо с шины операнда на выход устройства. Сигнал с выхода сумматора 6 поступает на единичный вход триггера 8 и устанав.|ивает его в единичное состояние. В результате этого снимается сигнал с инверсного выхода триггера 8 и, вследствие этого, отсутствуют сигналы на первых входах элементов П 9 и 10 (коды с выходов блока вычитания 1 не передаются) и на управляющем входе узла управления 5 (сигналы на управляющие входы блока вычитания 1 не поступают и он не изменяет в дальнейшем своего состояния, а код на выходы старшего разряда блока вычитания 1 не поступает). Если триггер 7 установлен в нулевое состояние, то ко.ммутатор 4 передает в течение всех поеледуюп1их циклов код а,., а если в единичное состояние - то код в;. Поскольку код на выходе старшего разряда блока вычитания 1 отсутствует, то триггер 7 в дальнейшем не из.меняет своего состояния. На этом заканчивается один цикл вычислений. Ес.чн операнды имеют разност) т. то необходимо выполнить m циклов вычислений.

Таким образом предложенное устройство позволяет производить сравнение чисел нредставленных двоичным избыточным кодом.

Формула изобретения

Устройство для сравнения чисел, содержащее блок вычитания, сумматор, триггеры, элементы И, коммутаторы, сумматор по модулю два, узел управления, отличающееся тем, что, с целью расширения функциональных возможностей в чаети обеспечения сравнения чисел, представленных избыточным кодом, в нем входы блока вычитания соединены с шинами операндов, а его прямой и инверсный выходы старшего разряда подключены ко входам первого и второго элементов И соответственно и к информационным входам первого триггера, выходы которого соединены с одними из входов первого и второго элементов И и с управляющими входами первого коммутатора, информационные входы которого подключены к шинам операндов, а выходы - к одним из входов сумматора, другие входы которого соединены с выходами второго коммутатора, информационные входы которого подключены к выходам блока вычитания, а управляющие входы - к выходам первого и второго элементов И, одни из входов которых соединены с выходом второго триггера и со входом узла

управления, другие входы которого подключены к шинам управления и щинам тактовых сигналов, а выходы - ко входам блока вычитания, выходы второго и третьего разрядов которого соединены со входами сумматора по модулю два, управляющий вход которого подключен к щине тактовых сигналов, а выход - ко входу второго триггера.

Источники информации, принятые во внимание при экспертизе:

1.Авторское свидетельство СССР № 441560, кл. G 06 F 7/04, 1972.

2..Авторское свидетельство СССР № 446055, кл. G 06 F 7/04, 1973.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения чисел | 1979 |

|

SU840890A1 |

| Устройство для сложения и вычитания чисел с плавающей запятой | 1980 |

|

SU959070A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Устройство для деления двоичных чисел | 1990 |

|

SU1783520A1 |

| Устройство для деления двоичного числа на коэффициент | 1982 |

|

SU1072040A1 |

| Устройство для одновременного вычисления двух многочленов | 1980 |

|

SU926650A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для вычисления двумерного быстрого преобразования Фурье | 1986 |

|

SU1408442A1 |

| Устройство для умножения | 1977 |

|

SU662939A1 |

| Устройство для вычисления квадрата числа | 1983 |

|

SU1115051A1 |

Авторы

Даты

1978-04-15—Публикация

1976-04-26—Подача