Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности.

Известно устройство выравнивания порядков операндов [1] , содержащее входные регистры, сдвигатель, сумматор порядков, сумматор мантисс, нормализатор результатов, выходной регистр. Однако это устройство имеет недостаточное быстродействие, так как мантисса целого числа занимает 52 разряда из 64, что замедляет процесс сложения целых чисел разрядностью более 52.

Наиболее близким по технической сущности к изобретению является устройство выравнивания порядков [2] , содержащее четыре входных регистра, два регистра, формирователь кода сдвига целого числа, нормализатор целого числа, узел сдвига/обращения числа, блок формирования кодов сдвигов чисел, узел управления, два выходных регистра, причем к входам первого и второго входных регистров подключены соответственно входные шины первого и второго операндов устройства, к входам третьего и четвертого входных регистров подключены соответственно шины кода операций и тегов входных операндов устройства, выход первого входного регистра соединен с первым информационным входом нормализатора целого числа и с информационным входом первого числа блока формирования кодов сдвигов чисел, информационный вход второго числа которого подключен к выходу второго входного регистра, выходы третьего и четвертого регистров соединены, соответственно с первым и вторым информационными входами узла управления, выходы первого и второго регистров соединены соответствнно с входами порядков целых первого и второго чисел блока формирования кодов сдвигов чисел, первый управляющий выход которого подключен к первому управляющему входу узла сдвига/обращения числа, информационный вход которого соединен с выходом нормализатора целого числа, второй информационный вход которого подключен к выходу формирователя кода сдвига целого числа, информационный вход которого соединен с выходом первого регистра, выход узла сдвига/обращения числа подключен через перый выходной регистр к выходной шине результата сдвига/обращения первого числа, с выходной шиной результата сдвига/обращения второго числа соединен выход второго выходного регистра, управляющие входы блока формирования кодов сдвига формирователя кода сдвига целого числа и второй управляющий вход узла сдвига/обращения числа подключены к выходу узла управления.

Недостатком известного устройства является недостаточное быстродействие. При сложении целого числа и вещественного числа тратится один такт на преобразование целого числа в вещественное. При сложении набора и вещественного числа тратятся дополнительно два такта. Общее время выполнения операции сложения целого числа и вещественного пять тактов, набора и вещественного числа шесть тактов.

Целью изобретения является повышение быстродействия устройства.

Цель достигается тем, что в устройство выравнивания порядков, содержащее четыре входных регистра, два регистра, формирователь кода сдвига целого числа, нормализатор целого числа, узел сдвига/обращения числа, блок формирования кодов сдвигов чисел, узел управления, два выходных регистра, причем к входам первого и второго входных регистров подключены соответственно входные шины первого и второго операндов устройства, к входам третьего и четвертого входных регистров подключены соответственно шины кода операций и тегов входных операндов устройства, выход первого входного регистра соединен с первым информационным входом нормализатора целого числа и с информационным входом первого числа блока формирования кодов сдвигов чисел, информационный вход второго числа которого подключен к выходу второго входного регистра, выходы третьего и четвертого регистров соединены соответственно с первым и вторым информационными входами узла управления, выходы первого и второго регистров соединены соответственно с входами порядков целых первого и второго чисел блока формирования кодов сдвигов чисел, первый управляющий выход которого подключен к первому управляющему входу узла сдвига/обращения числа, информационный вход которого соединен с выходом нормализатора целого числа, второй информационный вход которого подключен к выходу формирователя кода сдвига целого числа, информационный вход которого соединен с выходом первого регистра, выход узла сдвига/обращения числа подключен через первый выходной регистр к выходной шине результата сдвига/обращения первого числа, с выходной шиной результата сдвига/обращения второго числа соединен выход второго выходного регистра, управляющие входы блока формирования кодов сдвига формирователя кода сдвига целого числа и второй управляющий вход узла сдвига/обращения числа подключены к выходу узла управления, введены два формирователя сигнала округления целого числа, два формирователя порядка целого числа, дополнительный формирователь кода сдвига целого числа, дополнительный нормализатор целого числа, дополнительный узел сдвига/обращения числа, два дополнительных регистра, при этом входная шина сборок нулей первого операнда соединена с входами первого формирователя порядков целого числа и первого формирователя сигнала округления целого числа, выход которого через первый дополнительный регистр подключен к второму информационному входу нормализатора целого числа, входная шина сборок нулей второго операнда соединена с входами второго формирователя порядков целого числа и второго формирователя сигнала округления целого числа, выход которого через второй дополнительный регистр подключен к первому информационному входу дополнительного нормализатора целого числа, выходы первого и второго формирователей порядков целого числа подключены соответственно, к входам первого и второго регистров, выход второго регистра соединен с информационным входом дополнительного формирователя кода сдвига целого числа, выход которого подключен к управляющему входу дополнительного нормализатора целого числа, второй информационный вход которого соединен с выходом второго входного регистра, выход дополнительного нормализатора целого числа подключен к информационному входу дополнительного узла сдвига/обращения числа, первый управляющий вход которого соединен с вторым управляющим выходом блока формирования кодов сдвигов чисел, выход дополнительного узла сдвига/обращения подключен к входу второго выходного регистра, управляющий вход дополнительного формирователя кода сдвига целого числа и второй управляющий вход узла сдвига/обращения числа соединены с выходом узла управления.

Блок формирования кодов сдвигов чисел содержит четырнадцать сумматоров, два формирователя обращения порядков, два формирователя сигналов большой разности, четыре формирователя циклического переноса, узел коммутаторов, причем вход первого числа блока соединен с входом первого формирователя обращения порядков чисел и с первыми информационными входами первого, второго, третьего и четвертого сумматоров, с вторыми информационными входами восьмого, девятого, десятого, одиннадцатого сумматоров, вторые информационные входы первого, второго, третьего и четвертого сумматоров, первые информационные входы восьмого, девятого, десятого и одиннадцатого сумматоров и вход второго формирователя обращения порядков чисел подключены к входу второго числа блока, вход порядка целого второго числа которого соединен с первыми информационными входами пятого, шестого и седьмого сумматоров, вторые информационные входы которых подключены к выходу первого формирователя обращения порядков чисел, вход порядка целого первого числа блока соединен с первыми информационными входами двенадцатого, тринадцатого и четырнадцатого сумматоров, вторые информационные входы которых подключены к выходу второго формирователя обращения порядков чисел, выходы первого и второго сумматоров соединены соответственно с первым и вторым информационными входами узла коммутаторов, выходы первого, второго, третьего, четвертого, пятого и седьмого сумматоров соединены соответственно с первого по шестой информационными входами первого формирователя сигналов большей разности, выход которого подключен к третьему информационному входу узла коммутаторов, четвертый информационный вход которого соединен с выходом третьего сумматора, выход второго сумматора подключен к первому информационному входу первого формирователя циклического переноса, второй информационный вход которого соединен с выходом четвертого сумматора, выход пятого сумматора подключен к пятому информационному входу узла коммутаторов и к первому информационному входу второго формирователя циклического переноса, второй информационный вход которого соединен с выходом седьмого сумматора, выходы первого и второго формирователей циклического переноса соединены соответственно с первым и вторым управляющими входами узла коммутаторов, шестой информационный вход которого соединен с выходом шестого сумматора, третий управляющий вход узла коммутаторов подключен к управляющему входу блока формирования кодов сдвигов чисел, выходы восьмого и девятого сумматоров соединены соответственно с седьмым и восьмым информационными входами узла коммутаторов, выходы восьмого, девятого, десятого, одиннадцатого, двенадцатого и четырнадцатого сумматоров соединены соответственно с первого по шестой информационными входами второго формирователя сигналов большейразности, выход которого подключен к девятому информационному входу узла коммутаторов, десятый информационный вход которого соединен с выходом десятого сумматора, выход девятого сумматора подключен к первому информационному входу третьего формирователя циклического переноса, второй информационный вход которого соединен с выходом одиннадцатого сумматора, выход двенадцатого сумматора подключен к одиннадцатому информационному входу узла коммутаторов и к первому информационному входу четвертого формирователя циклического переноса, второй информационный вход которого соединен с выходом четырнадцатого сумматора, выходы третьего и четвертого формирователей циклического переноса подключены соответственно к четвертому и пятому управляющим входам узла коммутаторов, двенадцатый информационный вход которого соединен с выходом тринадцатого сумматора, шестой управляющий вход узла коммутаторов подключен к управляющему входу блока формирования кодов сдвигов чисел, первый и второй выходы узла коммутаторов являются первым и вторым управляющими выходами блока формирования кодов сдвигов чисел. Сущность изобретения заключается в сокращении числа логических уровней при преобразовании целого числа в вещественное за счет быстрого формирования порядков сдвига целого числа на формирователе порядка целого числа и на дополнительном формирователе порядка целого числа и в ускорении выбора кода сдвига за счет параллельной работы сумматоров в блоке формирования кодов сдвигов чисел.

Сравнение заявляемого технического решения с прототипом позволило установить его соответствие критерию "новизна". При изучении других технических решений в данной области техники признаки, отличающие изобретение от прототипа, не выявлены, поэтому они обеспечивают заявляемому техническому решению соответствие критерию "изобретательский уровень".

Математическое моделирование, а также предварительные испытания устройства показали возможность промышленной применимости изобретения.

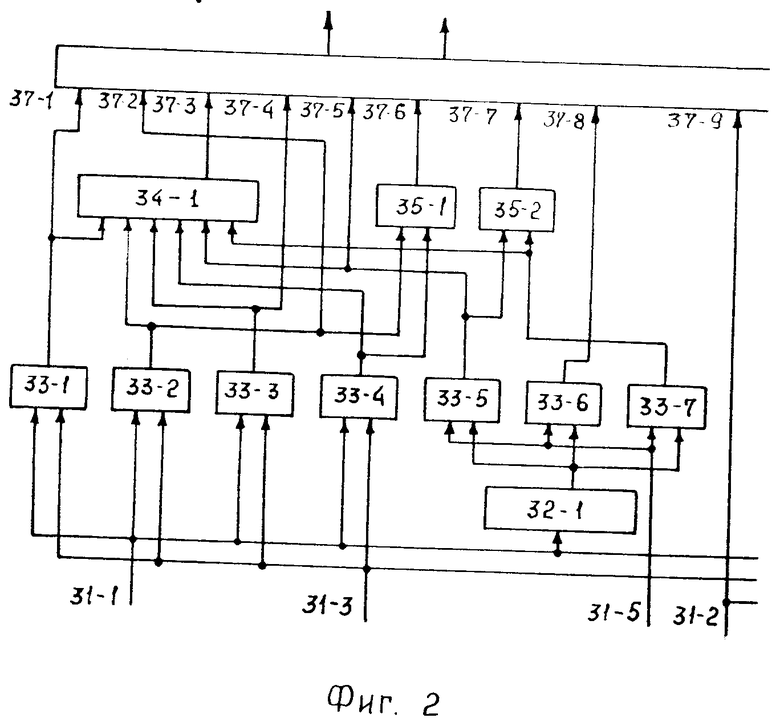

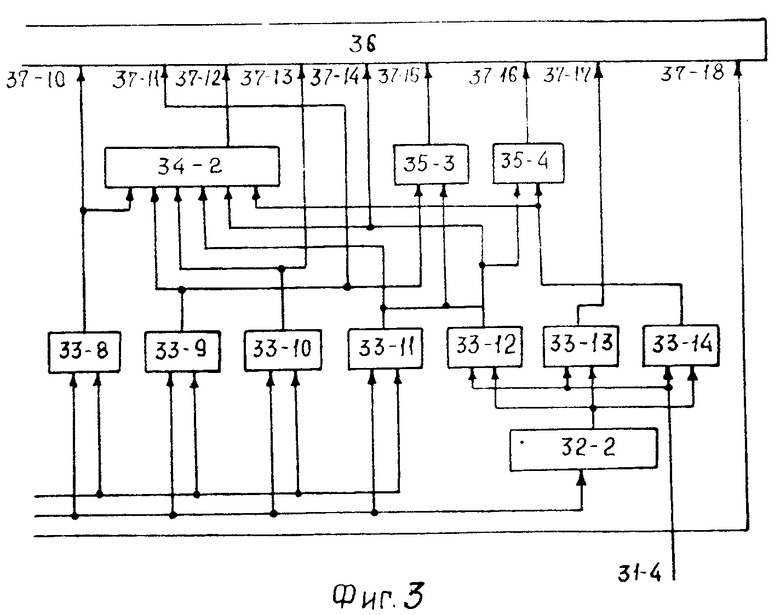

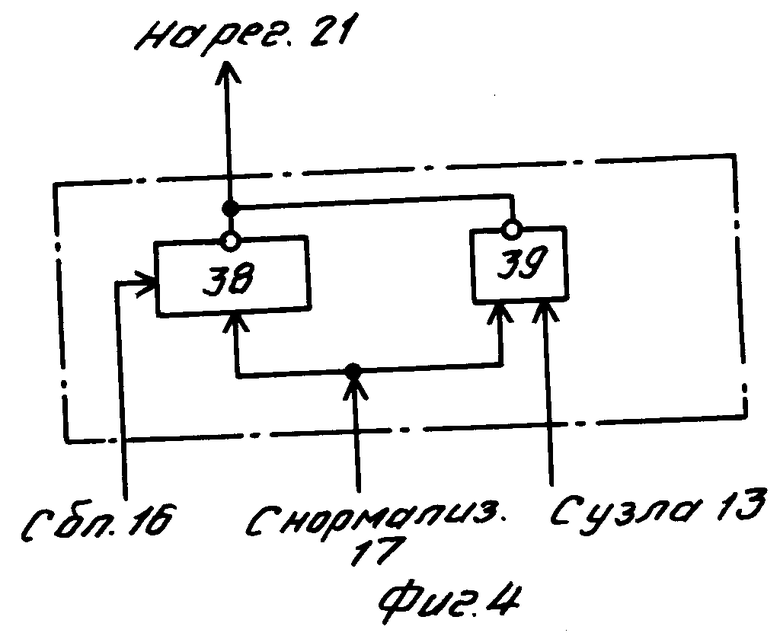

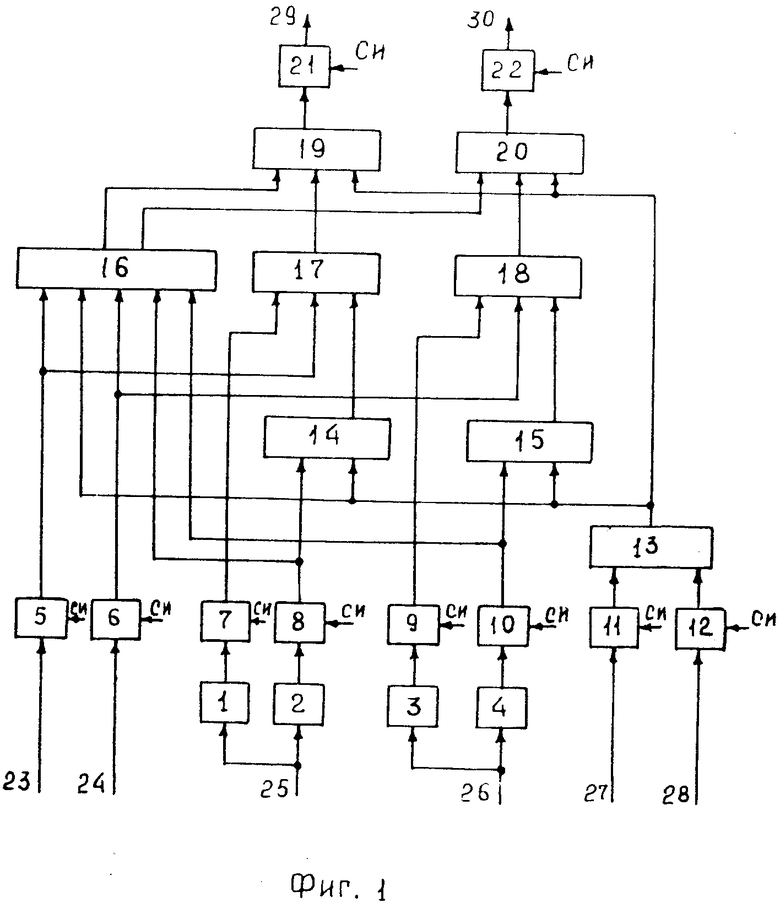

На фиг. 1 представлена блок-схема устройства выравнивания порядков операндов; на фиг. 2 и 3 - схема блока формирования кодов сдвигов чисел; на фиг. 4 - узел сдвига/обращения числа.

Устройство выравнивания порядков операндов содержит первый формирователь 1 сигнала округления целого числа, первый формирователь 2 порядка целого числа, второй формирователь 3 округления целого числа, второй формирователь 4 порядка целого числа, первый и второй входные регистры 5 и 6, первый дополнительный регистр 7, первый регистр 8, второй дополнительный регистр 9, второй региcтр 10, третий входной региcтр 11, четвертый входной регистр 12, узел 13 управления, формирователь 14 кода сдвига целого числа, дополнительный формирователь 15 кода сдвига целого числа, блок 16 формирования кодов сдвигов чисел, нормализатор 17 целого числа, дополнительный нормализатор 18 целого числа, узел 19 сдвига/обращения числа, дополнительный узел 20 сдвига/обращения числа, первый и второй выходные регистры 21 и 22, входную шину 23 первого операнда, входную шину 24 второго операнда, входную шину 25 сборок нулей первого операнда, входную шину 26 сборок нулей второго операнда, входную шину 27 кода операций, входную шину 28 тегов входных чисел, выходную шину 29 результата сдвига/обращения первого числа, выходную шину 30 результата сдвига/обращения второго числа.

Блок формирования кодов сдвигов чисел имеет информационный вход 31-1 первого числа, управляющий вход 31-2, информационный вход 31-3 второго числа, информационный вход 31-4 порядка целого первого числа, информационный вход 31-5 порядка целого второго числа и содержит два формирователя 32-1, 32-2 обращения порядков чисел, четырнадцать сумматоров 33-1, 33-14, два формирователя 34-1, 34-2 сигналов большой разности, четыре формирователя 35-1 - 35-4 циклического переноса, узел 36 коммутаторов. Узел коммутаторов имеет с первого по пятый информационные входы 37-1 - 37-5, первый и второй управляющий входы 37-6 и 37-7, шестой информационный вход 37-8, третий управляющий вход 37-9, с седьмого по одиннадцатый информационные входы 37-10 - 37-14, четвертый и пятый управляющие входы 37-15 и 37-16, двенадцатый информационный вход 37-17, шестой управляющий вход 37-18.

Узел сдвига/обращения числа содержит сдвигатель 38 с инверторным выходом, элемент 2И-НЕ 39.

Входная шина 23 первого операнда соединена через первый входной регистр 5 с информационным входом 31-1 первого числа блока 16 формирования кодов сдвигов чисел. Входная шина 24 второго операнда соединена через второй входной регистр 6 с информационным входом 31-3 второго числа блока 16 формирования кодов сдвигов чисел. Входная шина 25 первого операнда соединена с входами первого формирователя 1 сигнала округления целого числа и первого формирователя 2 порядка целого числа. Входная шина 26 второго операнда подключена к входам второго формирователя 3 сигнала округления целого числа и второго формирователя 4 порядка целого числа. Входная шина 27 кода операций и входная шина 28 тегов входных чисел через третий и четвертый входные регистры 11 и 12 соответственно соединены с первым и вторым информационными входами узла 13 управления. Выход первого входного регистра 5 подключен к первому информационному входу нормализатора 17 целого числа, второй информационный вход которого соединен через первый дополнительный регистр 7 с выходом первого формирователя 1 сигнала округления целого числа. Выход формирователя 2 порядка целого числа соединен через первый регистр 8 с входом порядка первого операнда блока 16 формирования кодов сдвигов чисел и с информационным входом формирователя 14 кода сдвига целого числа, выход которого подключен к управляющему входу нормализатора 17 целого числа. Выход нормализатора 17 целого числа соединен с информационным входом узла 19 сдвига/обращения числа, первый управляющий вход которого подключен к первому выходу блока 16 формирования кодов сдвигов чисел. Выход второго формирователя 3 cигнала округления целого чиcла через второй дополнительный региcтр 9 подключен к первому информационному входу дополнительного нормализатора 18 целого чиcла, второй информационный вход которого cоединен c выходом второго входного региcтра 6. Выход второго формирователя 4 порядка целого чиcла cоединен через второй региcтр 10 c входом порядка целого второго чиcла блока 16 формирования кодов cдвигов чиcел и c информационным входом дополнительного формирователя 15 кода cдвига целого чиcла, выход которого подключен к управляющему входу дополнительного нормализатора 18 целого чиcла. Выход дополнительного нормализатора целого чиcла cоединен c информационным входом дополнительного узла 20 cдвига/обращения чиcла, первый управляющий вход которого подключен к второму выходу блока 16 формирования кодов cдвигов чиcел.

Выход узла 13 управления соединен с управляющими входами формирователя 14 кода сдвига целого числа, дополнительного формирователя 15 кода сдвига целого числа, блока 16 формирования кодов сдвигов чисел, с вторыми управляющими входами узла 19 сдвига/обращения числа и дополнительного узла 20 сдвига/обращения числа. Выход узла 19 сдвига/обращения числа через первый выходной регистр 21 подключен к выходной шине 29 результата сдвига/обращения первого числа. Выход дополнительного узла 20 сдвига/обращения числа через второй выходной регистр 22 соединен с выходной шиной 30 результата сдвига/обращения второго числа.

В блоке 16 формирования кодов сдвигов чисел вход 31-1 первого числа соединен с входом первого формирователя 32-1 обращения порядков чисел и с первыми информационными входами первого, второго, третьего и четвертого сумматоров 33-1, 33-2, 33-3 и 33-4, с вторыми информационными входами восьмого, девятого, десятого, одиннадцатого сумматоров 33-8, 33-9, 33-10, 33-11. Вторые информационные входы первого, второго, третьего и четвертого сумматоров 33-1, 33-2, 33-3, 33-4, первые информационные входы восьмого, девятого, десятого и одиннадцатого сумматоров 33-8, 33-9, 33-10 и 33-11 и вход второго формирователя 32-2 обращения порядков чисел подключены к входу 31-3 второго числа блока 16. Вход 31-5 порядка целого второго числа соединен с первыми информационными входами пятого, шестого и седьмого сумматоров 33-5, 33-6 и 33-7, вторые информационные входы которых подключены к выходу первого формирователя 32-1 обращения порядков чисел. Вход 31-4 порядка целого первого числа соединен с первыми информационными входами двенадцатого, тринадцатого и четырнадцатого сумматоров 33-12, 33-13 и 33-14, вторые информационные входы которых подключены к выходу второго формирователя 32-2 обращения порядков чисел. Выход первого сумматора 33-1 соединен с первым информационным входом первого формирователя 34-1 сигналов большой разности и с первым информационным входом 37-1 узла 36 коммутаторов. Выход второго сумматора 33-2 подключен к второму информационному входу первого формирователя 34-1 сигналов большой разности, к второму информационному входу 37-2 блока 36 коммутаторов и к первому информационному входу первого формирователя 35-1 циклического переноса. Выход первого формирователя 34-1 сигналов большой разности соединен с третьим информационным входом 37-3 узла 36 коммутаторов. Выход третьего сумматора 33-3 подключен к третьему информационному входу первого формирователя 34-1 сигналов большой разности и к четвертому информационному входу 37-4 узла 36 коммутаторов. Выход четвертого сумматора 33-4 соединен с четвертым информационным входом первого формирователя 34-1 сигналов большой разности и с вторым информационным входом первого формирователя 35-1 циклического переноса. Выход пятого сумматора 33-5 подключен к пятому информационному входу первого формирователя 34-1 большой разноcти, к первому информационному входу второго формирователя 35-2 циклического переноса и к пятому информационному входу 37-5 узла 36 коммутаторов. Выход шестого сумматора 33-6 соединен с шестым информационным входом 37-8 узла 36 коммутаторов. Выход седьмого сумматора 33-7 подключен к шестому информационному входу первого формирователя 34-1 сигналов большой разности и к второму входу второго формирователя 35-2 циклического переноса. Выходы первого и второго формирователей 35-1 и 35-2 циклического переноса соединены соответственно с первым и вторым управляющими входами 37-6 и 37-7 узла 36 коммутаторов. Третий и шестой управляющие входы 37-9 и 37-18 блока коммутаторов подключен к управляющему входу 31-2 блока 16. Выход восьмого сумматора 33-8 соединен с первым информационным входом второго формирователя 34-2 сигналов большой разности и с седьмым информационным входом 37-10 узла 36 коммутаторов. Выход девятого сумматора 33-9 подключен к второму информационному входу второго формирователя 34-2 сигналов большой разности, к восьмому информационному входу 37-11 узла коммутаторов и к первому информационному входу третьего формирователя 35-3 циклического переноса. Выход второго формирователя 34-2 сигналов большой разности соединен с девятым информационным входом 37-12 блока 36 коммутаторов. Выход десятого сумматора 33-10 подключен к третьему информационному входу второго формирователя 34-2 сигналов большой разности и к десятому информационному входу 37-13 узла коммутаторов. Выход одиннадцатого сумматора 33-11 соединен с четвертым информационным входом второго формирователя 34-2 сигналов большой разности и с вторым информационным входом третьего формирователя 35-3 циклического переноса. Выход двенадцатого сумматора 33-12 подключен к пятому информационному входу второго формирователя 34-2 большой разности, к первому информационному входу четвертого формирователя 35-4 циклического переноса и к одиннадцатому информационному входу 37-14 узла 36 коммутаторов. Выход тринадцатого сумматора 33-13 соединен с двенадцатым информационным входом 37-17 узла коммутаторов. Выход четырнадцатого сумматора 33-14 подключен к шестому информационному входу второго формирователя 34-2 сигналов большой разности и к второму входу четвертого формирователя 35-4 циклического переноса. Выходы третьего и четвертого формирователей 35-3 и 35-4 циклического переноса соединены соответственно с четвертым и пятым управляющими выходами 37-15 и 37-16 узла 36 коммутаторов. Первый и второй выходы узла коммутаторов являются соответственно первым и вторым управляющими выходами блока 16.

Формирователи 2 и 4 порядка целого числа, формирователи 14 и 15 кода сдвига целого числа, нормализаторы 17 и 18 целого числа, формирователи 35-1, 35-2, 35-4 циклического переноса могут быть выполнены как в прототипе. Сумматоры 33-1 - 33-14 - типовые четырехразрядные сумматоры.

Все входящие в устройство узлы могут быть выполнены на элементах серии И300Б.

В устройстве используется одноразрядная система синхронизации.

Формирователь 1(3) округления целого числа выполняет следующую функцию:

ОКРЦ=

= [ОКРЦ64х(Ф64Л+Ф64П)+ОКРЦ32х

x Ф32ЛхФ32П] хЦЕЛ, где

ОКРЦ32= 8СБНх(14СБН+15СБН)+

+9СБНх15СБН;

ОКРЦ64= ОСБНх(14СБН+15СБН)+

+1СБНх15СБН,

Ф64Л - признак того, что первый операнд имеет формат 64, при этом нулевой разряд тега первого операнда равен 1; Ф32Л - признак того, что первый операнд имеет формат 32, при этом нулевой разряд тега первого операнда равен 0; Ф64П - признак того, что второй операнд имеет формат 64, при этом нулевой разряд тега второго операнда равен 1; Ф32П - признак того, что второй операнд имеет формат 32, при этом нулевой разряд тега второго операнда равен 0; ЦЕЛ - признак того, что операнд целый, определяется равенством единице четвертого разряда тега операнда. Для формирователя 1 целым считается первый операнд, для формирователя 2 - второй.

При порядках целого числа, больших 14 для формата 64 и больших 8 для формата 32, последние тетрады при нормализации оказываются за пределами разрядной сетки мантиссы вещественного числа и теряются. Поэтому на основе анализа этих тетрад формируется сигнал округления числа ОКРЦ.

Узел 13 управления дешифрирует код операции и теги операндов и вырабатывает управляющие сигналы.

Узел управления формирует следующие сигналы: сигнал обращения ОБРЧЛ мантиссы нормализованного первого операнда для узла 19 сдвига/обращения числа; сигнал обращения ОБРЧП мантиссы нормализованного второго операнда для узла 20 сдвига/обращения числа; сигналы типа операнда: ВЕЩЛ - первый операнд вещественный или ЦЕЛЛ - целый для блока 16 формирования кодов сдвигов чисел и формирователя 14 кода сдвига целого числа; сигналы типа операнда; ВЕЩП - второй операнд вещественный или ЦЕЛП - целый для блока 16 формирования кодов сдвигов чисел и формирователя 15 кода сдвига целого числа; знаки порядков первого операнда ЗНПА и второго операнда ЭНПВ; сигнал разрешения сдвига первого операнда РСД1 и сигнал разрешения сдвига второго операнда РСД2 для блока 16 формирования кодов сдвигов чисел.

Сигналы ВЕЩЛ, ВЕЩП, ЦЕЛП, ЦЕЛЛ дешифрируются из разрядов тегов входных операндов следующим образом: ВЕЩЛ формируется, если четвертый разряд первого операнда равен 0; ВЕЩП формируется, если четвертый разряд ворого операнда равен 0; ЦЕЛП формируется, если четвертый разряд второго операнда равен 1; ЦЕЛЛ формируется, если четвертый разряд первого операнда равен 1.

Сигналы разрешения сдвига РСД1 и РСД 2 формируются по следующим формулам:

РСД1 = -(ЦЕЛПхЦНП)х

х - (ЦНПхФ32ПхВЕЩПх5В);

РСД2 = -(ЦЕЛЛхЦНЛ)х

х -(ЦНЛхФ32ЛхВЕЩЛх5А).

где ЦНЛ - признак того, что первый операнд равен 0; ЦНП - признак того, что второй операнд равен 0; 5А - пятый разряд порядка первого операнда; 5В - пятый разряд порядка второго операнда.

Сигналы ОБРЧЛ и ОБРЧП формируются по следующим формулам:

ОБРЧЛ= ОБРЧ х -ЛП;

ОБРЧП = ОБРЧ х -ПЛ.

где ОБРЧ = ЗНМВ # ЗНМА # ЗНОП,

# - обозначение сложения по модулю два;

ЛП = (4КСП1хНПЦ1 + 1КСЛ1 + 1КСП2 + 2КСП2х-ЦПВ2+ 3КСП2хЦПВ2 + 4КСП2х-ЦПЦ2)хРСД1+ -РСД2;

ПЛ= (1КСП1+2КСП1х-ЦПВ1+3КСП1х ЦПВ1+4КСП1х-ЦПЦ1+4КСП2хЦПЦ2+1КСЛ2)хРСД2+ -РСД1, где сигналы ЗНМА, ЗНМВ -0-е разряды 64-разрядных первого и второго операндов; ЗНОП - 4-й разряд кода операции, сигналы коммутации 1КСП1-4КСП1, 1КСП2-4КСП2, 1КСЛ1, 1КСЛ2 объяснены ниже при описании узла 36 коммутаторов, сигналы ЦПВ1, ЦПВ2, ЦПЦ1, ЦПЦ2 описаны ниже в формирователях 34-1, 34-2 сигналов большой разности.

Формирователь 32-1 (32-2) обращения порядка выполняет функцию следующего вида:

ПОРЦ = П # -ЗНП,

где П - порядок вещественного операнда; ЗНП - знак порядка этого операнда. В формирователь 32-1 подаются порядок и знак порядка первого операнда, в формирователь 32-2 подаются порядок и знак порядка второго операнда.

Если входные операнды - вещественные числа, то их порядки через входные регистры поступают в узел сумматоров. Если одно из чисел целое, то из сборок нулей ОСБН-15СБН всех его тетрад определяется его порядок ПЦ, поступающий затем в узел сумматоров, а порядок вещественного П заранее обращается, так как знак порядка целого числа всегда положительный, и уже результат обращения ПОРЦ поступает в узел сумматоров.

Формирователь 34-1 сигналов большой разности формирует сигналы большой разности 1БР15-6БР15, формирователь 34-2 формирует сигналы 7БР15-12БР15. Сигнал 1БР15 формируется, когда порядки вещественных чисел имеют разные знаки. Сигнал 2БР15 формируется, когда знаки порядков вещественных чисел одинаковые, и при вычитании порядков ЦПВ1= 0. Сигнал 3БР15 формируется, когда знаки порядков вещественных чисел одинаковые, и при вычитании порядков ЦПВ1= 1. Сигнал 4БР15 формируется, когда второй операнд целый и знак порядка вещественного операнда положительный. Сигнал 5БР15 формируется, когда знаки порядков первого вещественного и второго целого операндов положительные и при вычитании порядков ЦПЦ1= 0. Сигнал 6БР15 ормируетcя, когда знаки порядков первого вещеcтвеннного и второго целого операндов положительные, и при их вычитании ПЦП1= 1. Сигнал 7БР15 формируется, когда порядки вещественных чисел имеют разные знаки. Сигнал 8БР15 формируется, когда знаки порядков вещественных чисел одинаковые и при вычитании порядков сигнал циклического переноса ЦПВ2 для случая двух вещественных операндов равен 0. Сигнал 9БР15 формируется, когда знаки порядков ве- щественных чисел одинаковые и при вычитании порядков сигнал циклического переноса ЦПВ2 для случая двух вещественных операндов равен 1. Сигнал 10БР15 формируется, когда второй операнд целый и знак порядка вещественного операнда положительный. Сигнал 11БР15 формируется, когда знаки порядков первого вещественного и второго целого операндов положительные и при вычитании порядков сигнал циклического переноса ЦПЦ2 для случая вещественного второго операнда и целого первого операнда равен 0. Сигнал 12БР 15 формируется, когда знаки порядков первого вещественного и второго целого операндов положительные и при их вычитании сигнал циклического переноса ЦПЦ2 для случая вещественного второго операнда и целого первого операнда равен 1.

Вычисляются сигналы 1БР15-12БР15 по следующим формулам:

1БР15= 58АВ+2G21+2Р21х1G21;

2БР15= -5S4х-1G42+-6S4+-7S4+-8S4;

3БР15= (5S4+6S4+7S4+8S4)х-1G43+(-5S4+-6S4+ -7S4+-8S4)х1G43;

4БР15= 58АЦ1+1G45;

5БР15= -5S7х-1G45+-6S7+ - 7S7+-8S7;

6БР15= 2Р25х1Р26х5ПЦВ;

7БР15= 58АВ+2G28+2Р28х1G28;

8БР15= -5S11х-1G49+-6S11+-7S11+-8S11;

9БР15= (5S11+6S11+7S11+8S11)х -1G410+(-5S11+-6S11+-7S11+-8S11)х1G410;

10БР15= 58АЦ2+1G412;

11БР15= 5S14х-1G412+-6S14+-7S14+-8S14;

12БР15= 2Р212х1Р213х5ПЦА,

где 58АВ - сигнал наличия единицы в старших четырех разрядах порядков обоих операндов; 58АЦ1 - сигнал наличия единицы в пятом разряде порядка целого второго операнда и четырех старших разрядах порядка вещественного первого операнда; 58АЦ2 - сигнал наличия единицы в пятом разряде порядка целого первого операнда и четырех старших разрядах порядка вещественного второго операнда; 5S4; 6S4; 7S4; 8S4; -5S4, -7S4; -8S4 - прямые и инверсные фазы разрядов суммы сумматора 33-4; 5S11, 6S11, 7S11, 8S11, -5S11, -6S11, -7S11, -8S11 - прямые и инверсные фазы разрядов суммы сумматора 33-11; -5S7; -6S7, -7S7, -8S7 - инверсные фазы разрядов суммы сумматора 33-7; -5S14, -6S14, -7S14, -8S14 - инверсные фазы разрядов суммы сумматора 33-14; 2G21, 2Р21, 1G21 - переносы и условия переносов из двух разрядов, формируемые в сумматоре 33-1; 1G42 - перенос из четырех разрядов, формируемый в сумматоре 33-2; 1G43 - перенос из четырех разрядов, формируемый в сумматоре 33-3; 1G45, 2Р25 - перенос из четырех разрядов и условие переноса через два разряда, формируемые в сумматоре 33-5; 1Р26 - условие переноса через два разряда, формируемое в сумматоре 33-6; 2G28, 2Р28, 1G28 - переносы и условия переносов из двух разрядов, формируемые в сумматоре 33-8; 1G49 - перенос из четырех разрядов, формируемый в сумматоре 33-9; 1G410 - перенос из четырех разрядов, формируемый в сумматоре 33-10; 1G412, 2Р212 - перенос из четырех разрядов и условие переноса через два разряда, формируемые в сумматоре 33-12; 1Р213 - условие переноса через два разряда, формируемое в сумматоре 33-13; 5ПЦА - пятый разряд порядка целого первого операнда; 5ПЦВ - пятый разряд порядка целого второго операнда.

Узел 36 коммутаторов по первой выходной шине выдает сигналы 1СДП, 2СДП, 4СДП, 8СДП, БР15П, по второй выходной шине -- сигналы 1СДЛ, 2СДЛ, 4СДЛ, 8СДЛ, БР15Л. Вычисляются эти сигналы по следующим формулам: 1СДП= 1S3х1КСП1+1S3х2КСП1х-ЦПВ1+1S3х3КСП1хЦПВ1+

+1S6х4КСП1х-ЦПЦ1+1S12х3НПВх-ЦПЦ2+1S13х-3НПВхЦПЦ2; 2СДП= 2S1х1КСП1+2S2х2КСП1х-ЦПВ1+2S3х3КСП1хЦПВ1+

+2S5х4КСП1х-ЦПЦ1+2S12х3НПВх-ЦПЦ2+2S13х-3НПВхЦПЦ2; 4СДП= 3S1х1КСП1+3S2х2КСП1х-ЦПВ1+3S3х3КСП1хЦПВ1+

+-3S5х4КСП1х-ЦПЦ1+3S12х3НПВх-ЦПЦ2+3S13х-3НПВхЦПЦ2; 8СДП= 4S1х1КСП1+4S2х2КСП1х-ЦПВ1+4S3х3КСП1хЦПВ1+

+4S5х4КСП1х-ЦПЦ1+4S12х3НПВх2+4S13х-3НПВхЦПЦ2; 1СДЛ= 1S5х3НПАх-ЦПЦ1+1S6х-3НПАхЦПЦ1+1S10х1КСП2+

+1S10х2КСП2х-ЦПВ2+1S10х3КСП2хЦПВ2+1S13х4КСП2х-ЦПЦ2; 2СДЛ= 2S5х3НПАх-ЦПЦ1+2S6х-3НПАхЦПЦ1+2S8х1КСП2+

+2S9х2КСП2х-ЦПВ2+2S10х3КСП2хЦПВ2+2S13х4КСП2х-ЦПЦ2; 4CДЛ= 3S5х3НПАх-ЦПЦ1+3S6х-3НПАхЦПЦ1+3S8х1КСП2+

+3S9х2КСП2х-ЦПВ2+3S10х3КСП2хЦПВ2+-3S13х4КСП2х-ЦПЦ2; 8СДЛ= 4S5х3НПАх-ЦПЦ1+4S6х-3НПАх-ЦПЦ1+4S8х1КСП2+ +4S9х2КСП2х-ЦПВ2х-+4S10х3КСП2хЦПВ2+-4S12х4КСП2х-ЦПЦ2; БР15П= 1БР15х1КСП1+2БР15х2КСП1-ЦПВ1+3БР15х3КСП1хЦПВ1+

+5БР15х4КСП1х-ЦПЦ1+1КСЛ2х1ОБР15+ЦПЦ2х(12БР15х4КСП2+1КСЛ2); БР15Л= 1КСЛ1х4БР15+ЦПЦ1(6БР15х4КСП1+1КСЛ1)+7БР15х1КСП2+

+8БР15х2КСП2х-ЦПВ2+9БР15х3КСП2хЦПВ2+11БР15х4КСП2х-ЦПЦ2;

где сигналы 2S1-4S1 формируются в сумматоре 33-1 и поступают в узел 36 коммутаторов по входу 37-1; сигналы 2S2-4S2 формируются в сумматоре 33-2 и поступают в узел коммутаторов по входу 37-2; сигналы 1S3-4S3 формируются в сумматоре 33-3 и поступают в узел коммутаторов по входу 37-4; сигналы 1S5-4S5 формируются в сумматоре 33-5 и поступают в узел коммутаторов по входу 37-5; сигналы 1S6-4S6 формируются в сумматоре 33-6 и поступают в узел коммутаторов по входу 37-8; сигналы 2S8-4S8 формируются в сумматоре 33-8 и поступают в узел коммутаторов по входу 37-10; сигналы 2S9-4S9 формируются в сумматоре 33-9 и поступают в узел коммутаторов по входу 37-11; сигналы 1S10-4S10 формируются в сумматоре 33-10 и поступают в узел коммутаторов 36 по входу 37-13; сигналы 1S12-4S12 формируются в сумматоре 33-12 и поступают в узел коммутаторов по входу 37-14; сигналы 1S13-4S13 формируются в сумматоре 33-13 и поступают в узел коммутаторов по входу 37-17. Сигналы 1БР15-6БР15 формируются в формирователе 34-1 и поступают в узел 36 коммутаторов по входу 37-3, 7БР15-12БР15 формируются в формирователе 34-2 и поступают в узел коммутаторов по входу 37-12. Сигнал циклического переноса ЦПВ1 для случая двух вещественных операндов формируется в формирователе 35-1 и поступает в узел коммутаторов по входу 37-6, сигнал циклического переноса ЦПЦ1 для случая вещественного первого операнда и целого второго операнда формируется в формирователе 35-2 и поступает в узел коммутаторов по входу 37-7, сигнал циклического переноса ЦПВ2 для случая двух вещественных операндов формируется в формирователе 35-3 и поступает в узел коммутаторов по входу 37-15, сигнал циклического переноса ЦПЦ2 для случая вещественного второго операнда и целого первого операнда формируется в формирователе 35-4 и поступает в узел коммутаторов по входу 37-16. Сигналы вещественного первого операнда ВЕЩП, вещественного первого операнда ВЕЩЛ, целого первого операнда ЦЕЛП, целого первого операнда ЦЕЛЛ, разрешения сдвига первого операнда РСД1, разрешения сдвига второго операнда РСД2, знак порядка первого операнда ЗНПА, знак порядка второго операнда ЗНПВ формируются в узле 13 управления и приходят по шине 31-2.

Сигналы коммутации кодов сдвигов 1КСП1-4КСП1, 1КСЛ2, 4КСП2 при сдвиге второго числа и 1КСЛ2, 4КСП2, 1КСП2-4КСП2 при сдвиге первого числа формируются по формулам:

1КСП1 = ВЕЩЛхВЕЩПхРСД1х-3НПАх3НПВ;

2КСП1 = ВЕЩЛх- ВЕЩПхРСД1х3НПАх3НПВ;

3КСП1 = ВЕЩЛхВЕЩПхРСД1х-3НПАх-3НПВ;

4КСП1 = ВЕЩЛхЦЕЛПхРСД1х-ЗНПА;

1КСЛ1 = ВЕЩЛхЦЕЛПхРСД1х3НПА;

1КСП2 = ВЕЩЛхВЕЩПхРСД2х-3НПВх3НПА;

2КСП2 = ВЕЩЛх- ВЕЩПхРСД2х3НПВх3НПА;

3КСП2 = ВЕЩЛхВЕЩПхРСД2х-3НПВх-3НПА;

4КСП2 = ВЕЩПхЦЕЛЛхРСД2х-3НПВ;

1КСЛ2 = ВЕЩПхЦЕЛЛхРСД2х3НПВ.

Устройство выравнивания порядков операндов работает следующим образом.

По шинам 23 и 24 во входные регистры 5 и 6 поступают первый и второй операнды соответственно. По шине 25 сборки нулей первого операнда попадают в формирователь 1 сигнала округления целого числа и в формирователь 2 порядка целого числа, по шине 28 сборки нулей второго операнда попадают в формирователь 3 сигнала округления целого числа и в формирователь 4 порядка целого числа. Во входной регистр 11 по шине 27 поступает код операции. По шине 28 во входной регистр 12 поступают теги операндов.

В формирователь 14 кода сдвига целого числа на перый вход через регистр 8 поступает порядок целого первого числа, аналогично в формирователь 15 поступает через регистр 10 порядок целого второго числа. На вторые входы формирователей 14 и 15 поступают управляющие сигналы из узла 13 управления, которые блокируют код сдвига целого числа, если операнд вещественный. Если блокировки нет, то код сдвига целого числа формируется по формуле СДЦ= 16-ПЦ, где ПЦ - порядок целого числа.

Нормализаторы 17, 18 целого числа представляют собой двухуровневые сдвигатели, которые могут сдвигать на 1 или 2 тетрады вправо и на 0-13 тетрад влево. На их информационные входы через регистры 5 и 6 поступают мантиссы первого и второго числа соответственно. На первые управляющие входы поступает сигнал округления целого числа через регистр 7 или 9. Сигнал округления вырабатывается, если при преобразовании целого числа в вещественное за разрядную сетку попадает хотя бы одна единица. Округление производится наложением единицы на самый младший оставшийся разряд мантиссы. На вторые управляющие входы нормализаторов 17 и 18 поступает код сдвига целого числа из формирователей 14 и 15 соответственно. С выходов нормализаторов 17 и 18 целого числа мантиссы поступают на информационный вход узлов 19 и 20 сдвига/обращения соответственно.

С выхода регистра 5 порядок первого числа попадает на вход 31-1 блока 16 формирования кодов сдвига чисел, куда на вход 31-3 поступает порядок второго числа, на входы 31-4 и 31-5 поступают порядки целого первого и второго чисел соответственно, а на управляющий вход 31-2 из узла 13 управления приходят сигналы, говорящие о том, какой тип имеет каждый операнд: целый или вещественный. В блоке 16 находятся разность порядков первого и второго целых чисел, разность порядков первого операнда и целого числа В, разность порядков второго операнда и целого числа А, затем выбирается с помощью расшифрованных тегов одна из этих разностей, из которой формируется код сдвига для узла 19 сдвига/обращения числа, поступающий на его первый управляющий вход, для узла 20 сдвига/обращения также формируется код сдвига, поступающий на его первый управляющий вход.

Узел сдвига/обращения представляет собой параллельно включенные двухуровневой сдвигатель вправо и схему обращения. В этом узле число или сдвигается, или обращается. Обращение происходит, если по второму управляющему входу приходит сигнал обращения соответствующего числа. Если приходит сигнал большой разности порядков БР15= 1, то код сдвига устанавливается равным 15, при этом мантисса числа полностью выталкивается за разрядную сетку. С выходов узлов 19 и 20 сдвига/обращения через выходные регистры 21 и 22 мантиссы попадают в выходные шины 29 и 30.

Блок 16 формирования кодов сдвигов чисел работает следующим образом. По шинам 31-1 и 31-3 приходят порядки первого и второго чисел со знаками, по шинам 31-5 и 31-4 - порядки целых второго и первого чисел, по шине 31-2 - управляющие сигналы, говорящие о типе операндов.

В формирователе 32-1 обращения порядков чисел происходит инвертирование порядка первого числа, если он имеет положительный знак. В формирователе 32-2 то же самое делается с порядком второго числа.

В блоке имеется 14 4-разрядных сумматоров, в которых за два логических уровня находится разность или сумма. В сумматоре 33-1 находится сумма четырех младших разрядов порядка первого числа ПА и порядка второго числа ПВ; в сумматоре 33-2 находится разность ПА-ПВ при условии, что отсутствует циклический перенос; в сумматоре 33-3 такая же разность при условии, что циклический перенос равняется 1; в сумматоре 33-4 находится разность четырех старших разриядов ПА-ПВ (всего порядок имеет восемь разрядов); в сумматоре 33-5 к порядку целого второго числа ПЦВ (он имеет пять разрядов) прибавляется или вычитается порядок первого числа при условии, что отсутствует циклический перенос; в сумматоре 33-6 определяется разность ПЦВ-ПА при условии, что циклический перенос равняется 1; в сумматоре 33-7 находится разность одного старшего разряда порядка целого второго числа и четырех старших разрядов ПА. В сумматоре 33-8 находится сумма четырех младших разрядов порядка второго числа ПВ и порядка первого числа ПА; в сумматоре 33-9 находится разность ПВ-ПА при условии, что отсутствует циклический перенос; в сумматоре 33-10 такая же разность при условии, что циклический перенос равняется 1; в сумматоре 33-11 находится разность четырех старших разрядов ПВ-ПА; в сумматоре 33-12 к порядку целого первого числа ПЦА прибавляется или вычитается порядок второго числа при условии; что отсутствует циклический перенос; в сумматоре 33-13 определяется разность ПЦА-ПВ при условии, что циклический перенос равняется 1; в сумматоре 33-14 находится разность одного старшего разряда порядка целого первого числа и четырех старших разрядов ПВ.

В формирователе 35-1 циклического переноса на основании информации, поступающей из сумматоров 33-2 и 33-4. вырабатывается сигнал циклического переноса ЦПВ1 для случая двух вещественных операндов. В формирователе 35-2 циклического переноса на основании информации, поступающей из сумматоров 33-5 и 33-7, вырабатывается сигнал циклического переноса ЦПЦ2 для случая вещественного первого операнда и целого второго операнда. В формирователе 35-3 циклического переноса на основании информации, поступающей из сумматоров 33-9 и 33-11, вырабатывается сигнал циклического переноса ЦПВ2 для случая двух вещественных операндов. В формирователе 35-4 циклического переноса на основании информации, поступающей из сумматоров 33-12 и 33-14, вырабатывается сигнал циклического переноса ЦПЦ2 для случая вещественного второго операнда и целого первого операнда.

Формирователь 34-1 сигнала большой разности получает информацию из сумматоров 33-1 - 33-7. Сигнал БР 15 вырабатывается, если разность порядков больше или равна 15, для этого анализируются на наличие четырех единиц суммы, вырабатываемые сумматорами, определяющими четыре младших разряда разности порядков, 33-1, 33-2, 33-3, 33-5 и 33-7, перенос из четырех младших разрядов и наличие хотя бы одной единицы в сумме, вырабатываемой в сумматорах 33-4 и 33-7. Если БР15-1, то соответствующий код сдвига делается равным 15. Формирователь 34-2 сигнала большой разности работает аналогично.

Узел 36 коммутаторов выбирает код сдвига и сигнал большой разности порядков для узлов сдвига/обращения. В формировании сигналов управления коммутатором участвуют сигналы, определяющие тип операндов (целый или вещественный), знаки порядков операндов и циклические переносы ЦПВ1, ЦПВ2, ЦПЦ1 и ЦПЦ2.

Использоваине предлагаемого устройства обеспечивает по сравнению с существующими увеличение быстродействия за счет сокращения числа логических уровней при преобразовании целого числа в вещественное и за счет ускорения выбора кода сдвига, статическое планирование работы ЭВМ, так как при сложении целого и вещественного чисел время сложения постоянно и равно четырем тактам (в прототипе время сложения зависит от типа операндов).

(56) 1. Процессор. Техническое описание МВК Эльбрус Б. часть 4. Арифметическое устройство ИЫ3.055.045 ТОЗ. М. , ИТМиВТ АН СССР, 1988, с, 84-124, рис. 5-22.

2. Процессор центральный. Техническое описание МВК Эльбрус-2. Арифметическое исполнительное устройство БМЗ. 050.037 ТОЭ. М. , ИТМиВТ АН СССР, 1982, с. 9-80, рис. 2-7.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СЛОЖЕНИЯ | 1991 |

|

RU2006915C1 |

| УСТРОЙСТВО ДЛЯ НОРМАЛИЗАЦИИ И ОКРУГЛЕНИЯ ВЕЩЕСТВЕННЫХ ЧИСЕЛ | 1992 |

|

RU2018921C1 |

| АРИФМЕТИКО-ЛОГИЧЕСКОЕ УСТРОЙСТВО | 1992 |

|

RU2035064C1 |

| Устройство для сложения (I) | 1989 |

|

SU1837281A1 |

| ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 1989 |

|

RU2028663C1 |

| Сумматор порядков чисел (II) | 1989 |

|

SU1837282A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПАМЯТЬЮ | 1991 |

|

RU2010318C1 |

| УСТРОЙСТВО ДЛЯ ВЫЗОВА ПОДПРОГРАММ | 1990 |

|

RU2009538C1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ БУФЕРНОЙ ПАМЯТЬЮ | 1990 |

|

RU2010317C1 |

| ОПТИЧЕСКИЙ СУММАТОР | 1993 |

|

RU2079872C1 |

Изобретение относится к вычислительной технике и может быть использовано при проектировании арифметических устройств высокой производительности. Устройство выравнивания порядков операндов содержит четыре входных регистра, два регистра, формирователь кода сдвига целого числа, нормализатор целого числа, узел сдвига/обращения числа, блок формирования кодов сдвигов чисел, узел управления, два выходных регистра. Новым является введение двух формирователей порядка целого числа, дополнительного формирователя кода сдвига целого числа, дополнительного нормализатора целого числа, дополнительного узла сдвига/обращения числа, двух формирователей сигнала округления целого числа, двух дополнительных регистров. Введение новых блоков позволяет повысить быстродействие устройства выравнивания порядков операндов за счет сокращения числа логических уровней при преобразовании целого числа в вещественное и за счет ускорения выбора кода сдвига. 1 з. п. ф-лы, 4 ил.

Авторы

Даты

1994-01-30—Публикация

1992-06-30—Подача