( УСТРОЙСТВО для ХРАНЕНИЯ И ВЫБОРКИ ИНФОРМАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для хранения и выборкииНфОРМАции | 1979 |

|

SU841058A1 |

| Преобразователь напряжения в код Грея | 1984 |

|

SU1182687A1 |

| Аналоговое запоминающее устройство | 1981 |

|

SU978200A1 |

| Программируемый приемник сигналов для коммутационных сред | 1988 |

|

SU1718236A1 |

| Аналоговое запоминающее устройство | 1982 |

|

SU1062794A1 |

| Дифференциальный усилитель | 1983 |

|

SU1124427A1 |

| Операционный усилитель | 1989 |

|

SU1721614A1 |

| Устройство для интегрирования произведения двух сигналов | 1984 |

|

SU1211764A1 |

| Компаратор напряжений | 1988 |

|

SU1525891A1 |

| Устройство для выборки и хранения информации | 1986 |

|

SU1388955A1 |

1

Изобретение относится к информационно-измерительной технике и может быть использовано при проектировании аналого-цифровых преобразователей.

Известно устройство для хранения и выборки информации, содержащее два дифференциальных усилителя, охваченмых общей отрицательной обратной свя зьго, накопительный элемент и ключи в канале усиления, которые упоавляют режимом работы устройства 1

Однако это устройство имеет сравнительно большое время выборки вследствие использования ключа в канале усиления.

Наиболее близким техническим решением к изобретению является устройство для хранения и выборки информации, содержащее дифференциальный каскад, выполненный на первом, втором, третьем и четвертом транзисторах, причем база первого транзистора является входом устройства, эмиттеры первого и

и второго транзисторов объединены, эмиттеры третьего и четвертого транзисторов подключены к положительной шине питания, базы третьего и четвертого транзисторов объединены и подключены к коллекторам третьего и первого транзисторов, ключ, выполненный на пятом транзисторе, коллектор которого соединен с эмиттерами первого и второго транзисторов, база пятого транзистора подключена к шине управления, а эмиттер подключен к отрицательной шине питания, накопительный элемент, например конденсатор, первая

j обкладка которого соединена с шиной нулевого потенциала, а вторая обкладка подключена к входу буферного усилителя , выход которого соединен с базой второго транзистора, которая явЮ ляется выходом устройства f2j .

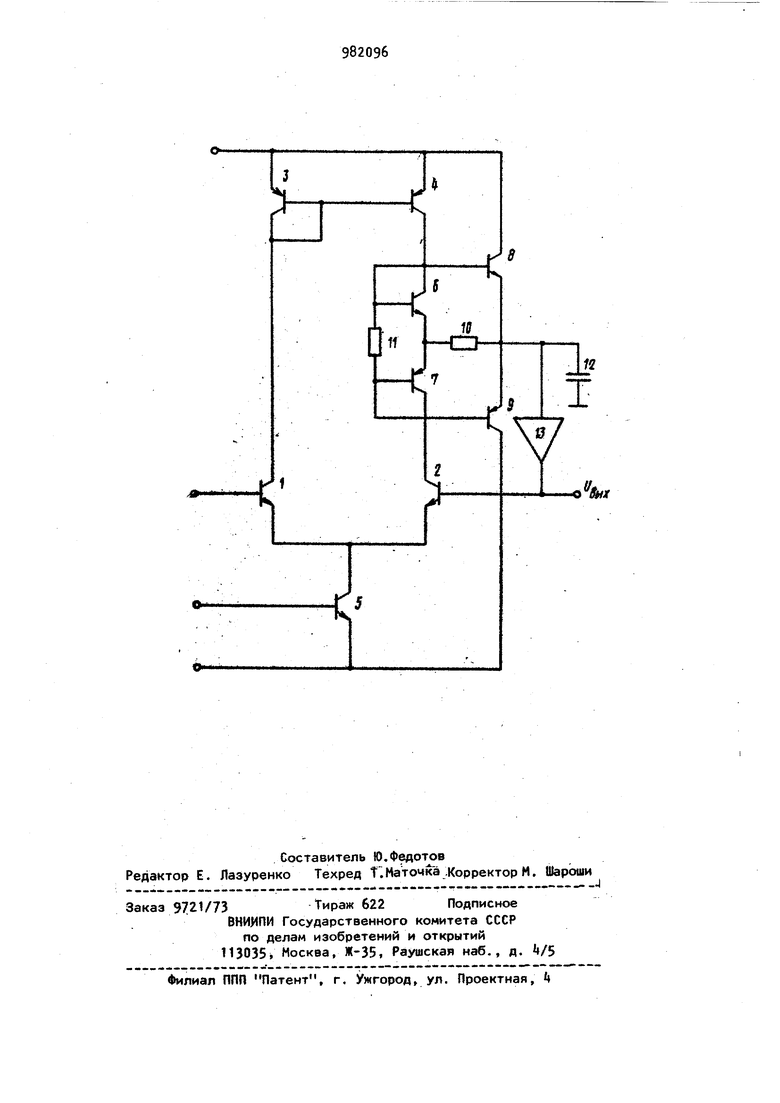

Однако данное устройство щ хранения и выборки информации из-за различных постоянных времени транзисто398ров дифференциального каскада при пёреходе к хранению имеет большое апертурное время, что сказывается на точности воспроизведения входного сигна ла. Кроме того, скорость заряда накопительного элемента ограничена дифференциального каскада, что приводит к большому времени выборки. Цель изобретения - увеличение точности быстродействия устройства. Поставленная цель достигается тем, что в устройство для хранения и вы- i борки информации введены пороговый ограничитель, выполненный на шестом и седьмом TpaH3iVicTopax и нагрузочном элементе, и генератор тока заряда, выполненный на восьмом и девятом транзисторах и токозадающем элементе, причем коллектор и база шестого транзистора соединены с коллектором четвертбго транзистора и с первым выводом нагрузочного элемента, коллектор и база седьмого транзистора соединены с коллектором второго транзистора и , вторым выводом нагрузочного элемента коллекторы восьмого и девятого транзисторов подключены соответственно к положительной и отрицательной шинам питания, база восьмого,и девятого транзисторов соединеньГ соответственно с коллекторами шестого и седьмого транзисторов, эмиттеры которых соединены с первым выводом токозадающего элемента, второй вывод которого соеди нен с эмиттерами восьмого и девятого транзисторов и второй обкладкой конденсатора. На чертеже изображена функциональ. ная схема устройства. Устройство содержит дифференциальный каскад, выполненный на транзисторах 1-А, ключ, выполненный на транзисторе 5. пороговый ограничитель на транзисторах 6 и 7, генератор тока за ряда на транзисторах 8 и 9 и токозадакщем элементе 10, нагрузочный элемент 11, накопительный элемент, например конденсатор 12, бyJфepный уси литель 13. Устройство для хранения и выборки информации работает следующим образом. В установившемся режиме выборки, когда с помощью управляющего напряжения на базе через транзистор 5 про текает постоянный ток, устройство ра ботает как усилитель с глубокой отри цательной обратной связью, повторяя 64 на выходе входное напряжение. Токи в плечах дифференциального каскада равны 0,51. ток в выходном племе дифференциального каскада делится между нагрузочным элементов П (.) и транзисторами 6 и 7 порогового ограничителя (0,51 - ). Токи транзисторов 6 и7, 8 и 9 равны, что достигается использованием в качестве 6 и 8, 7 и 9 согласованных пар транзисторов. Дли перевода устройства в режим хранения управляющее,напряжение изменяется так, чтобы ток через транзистор 5 стал равен нулю. В известном устройстве этот переход сопровождается значительными погрешностями из-за различных постоянных вре- ч мени уменьшения токов через транзисторы 2 и 4, что приводит к существенному (до 100 мВ) сдвигу напряжения, хранимого на конденсаторе 12, относительно истинного значения, а также вследствие сравнительно медленного уменьт шения тока в дифференциальном каскаде, В предлагаемом устройстве, выбрав 2U при переходе к хранению тсж через транзисторы 6 и 7 (следовательно 8 и 9) уменьшается практически до нуля в первый же момент, так как для этого достаточно, чтобы напряжение на нагрузочном элементе 11 уменьшилось всего на 100 мВ, т. е. в первый же момент перехода к хранению цепь из закрытых р-п переходов отключает запоминающий конденсатор 12 от выхода дифференциального каскада. Погрешность запоминаемого на конденсаторе 12 напряжения относительно его истинного значения равна разбросу напряжений эмиттер-база парных транзисторов 7 и 9 или 6 и 8 и может составлять 2-3 мВ. При переходе к выборке нового значения входного напряжения ток делится между цепью транзистора 6 (или 7), токозадающего элемента 10 и цепью базы транзистора 8 (или Э) Сопротивление токозадающего элемента 10 выбирается так, чтобы ток через транзисторы 8 и 9 не превышал максимально допустимого импульсного значения, которое для современных маломощных транзисторов достигает 100 мА. Этот относительно большой импульсный ток и обеспечивает заряд конденсатора 12, позволяя существенно увеличить быстродействие предлагаемого устройства по сравнению с известным. Кроме того. увеличение емкости конденсатора 12 , в предлагаемом устройстве позволяет дополнительно улучшать его точностны характеристики в режиме хранения, а именно уменьшить разряд конденсатора под действием токов утечки р-п лереходов. Таким образом, пдедлагаемое устройство позволяет повысить точность воспроизведения входного сигнала с 1 до 0,1% и уменьшить время выборки. Формула изобретения Устройство для хранения и выборки информации, содержащее дифференциаль ный каскад, выполненный на первом, втором, третьем и четвертом транзисторах, причем база первого транаисто ра является входом устройства, эмиттеры первого и второго транзисторов объединены, эмиттеры третьего и четвертого транзисторов подключены к. положительной шине питания, базы третье го и четвертого транзисторов объединены и подключены к коллекторам третьего и первого транзисторов, ключ, выполенный на пятом транзисторе, коллектор которого соединен с эмиттерами первого и второго транзисторов, база пятого транзистора подключена к шине управления, а .эмиттер подключен к отрицательной шине питания, накопительный элемент, например конденсатор, первая обкладка которого соединена с шиной нулевого потенциала, а вторая, обкладка подключена к входу буферного усилителя, выход которого соединен с базой второго транзистора, которая является выходом устройства, о т л и- . чающееся тем, что, с целью повышения точности и быстродействия устройства, в него введены пороговый ограничитель, выполненный на шестом и седьмом транзисторах и нагрузочном элементе, и генератор тока заряда, выполненный на восьмом и девятом транзисторах и токозадающем элементе, причем коллектор и база шестого транзистора соединены с коллектором четвертого транзистора и с первым выводом нагрузочного элемента, коллектор и база седьмого транзистора соединены с коллектором второго транзистора и вторым выводом нагрузочного элемента, коллекторы восьмого и девятого тоан- , зисторов подключены соответственно к положительной и otpицaтeльнoй -шинам питания, базы восьмого и девятого транзисторов соединены соответственно с коллекторами шестого и седьмого транзисторов, эмиттеры которых соединены с первым выводом токозадающего элемента, второй вывод которого соединен с эмиттерами; восьмого и девятого транзисторов и второй .обкладкой конденсатора. Источники информации, принятые во внимание при экспертизе . 1.Бахтиаров Г. Д., Малинин В.В. и Школин В. П. Аналого-цифровые npej образователи. М., Советское радио,:. 1980, с. П6. 2.Авторское свидетельство СССР fP , кл.С t1 С 27/02, 1979IB

12

Л

Г

Авторы

Даты

1982-12-15—Публикация

1981-05-08—Подача