(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ БЛОКОВ ПАМЯТИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения | 1980 |

|

SU875374A1 |

| Ультразвуковой дефектоскоп | 1988 |

|

SU1627974A1 |

| Программируемый аналого-цифровой преобразователь | 1987 |

|

SU1732469A1 |

| Преобразователь кода спектра звукового сигнала | 1990 |

|

SU1800618A1 |

| Программируемый генератор сигналов | 1980 |

|

SU959269A1 |

| Устройство для моделирования дискретных систем | 1985 |

|

SU1295411A1 |

| Ультразвуковой дефектоскоп | 1990 |

|

SU1746298A1 |

| ЛАЗЕРНЫЙ ИМПУЛЬСНЫЙ ДАЛЬНОМЕР | 2014 |

|

RU2551700C1 |

| МОДЕЛИРУЮЩИЙ КОАП | 2013 |

|

RU2516703C1 |

| Устройство контроля качества датчиков времени | 1986 |

|

SU1422218A1 |

1

Изобретение относится к устройствам контроля запоминающих блоков и может быть использовано в вычислительной технике и автоматике.

Известно устройство для контроля накопителей, содержащее регистр адреса, соединенный с дещифратором, блок контроля, подключенный к усилителям считывания и блоку управления, и счетчик циклов проверки, вход которого подключен к выходу регистра адреса, а выход - к блоку управления I

Известно также устройство для контроля запоминающего блока, которое является наиболее близким к предлагаемому по технической сущности. Устройство содержит выходной регистр, вход которого подключен к выходу запоминающего блока, а выход - к одному входу схемы сравнения, счетчик адресов, разрядные выходы которого подсоединены к блоку останова по адресу и запоминающему блоку, а вход - к блоку управления, преобразователь, вход которого подключен к выходу запоминающего блока, счетчик контрольного кода, один из входов которого подсоединен к выходу преобразователя, другой - к блоку управления, а выход - к другому входу схемы сравнения, к запоминающему блоку и ко входу блока останова по контрольному коду, выход которого подключен к блоку управления. В этом устройстве проверка постоянного запоминающего устройства (ПЗУ) производится счетом числа единиц в массиве и поразрядным суммированием по модулю 2. Проверка оперативного запоминающего устройства (ОЗУ) осуществляется последовательной записью - чтением-сравнением чисел от п до ш каждого в ячейки с номерами

от k до 1 2.

Недостатком известного устройства является низкая точность контроля оперативного запоминающего устройства с синхронным последовательным опросом ячеек, например, в системе обегающего контроля, в

5 составе группы синхронно работающих накопителей с последовательной выборкой, в частности, в виде группы синхронно работающих последовательных регистров.

Цель изобретения - повыщение точности контроля.

Поставленная цель достигается тем, что в устройство для контроля блоков памяти, содержащее счетчик и первую схему сравнения, первый вход которой является входом устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены формирователь контрольного кода, выход которого подключен ко второму входу схемы сравнения и является первым выходом устройства, первый, второй и третий триггеры, первые входы которых подключены к выходу первой схемы сравнения, первый формирователь импульсов, выход которого подключен ко второму входу второго триггера, элемент И-ИЛИ, первый вход которого подключен к выходу первого триггера, а выход - к первому входу счетчика, второй формирователь импульсов, выход которого подключен ко вторым входам элемента И-ИЛИ и третьего триггера, элемент И, первый вход которого подключен к выходу второго триггера, а выход - к третьему входу третьего триггера и ко второму входу счетчика, дешифратор, вход которого подключен к выходу счетчика, а выход - к третьему входу второго триггера, мультиплексор, первый вход которого подключен к выходу счетчика, формирователь адреса, выход которого подключен ко второму входу мультиплексора, вторую схему сравнения, первый вход котород подключен к выходу муфльтиплексора, второй вход - к выходу третьего триггера, а ее третий вход является вторым входом устройства, выход второй схемы сравнения подключен ко второму входу первого триггера и является вторым выходом устройства, синхронизатор, первый выход которого подключен к третьему входу элемента И-ИЛИ, второй выход - ко второму входу элемента И, а его третий выход является третьим выходом устройства.

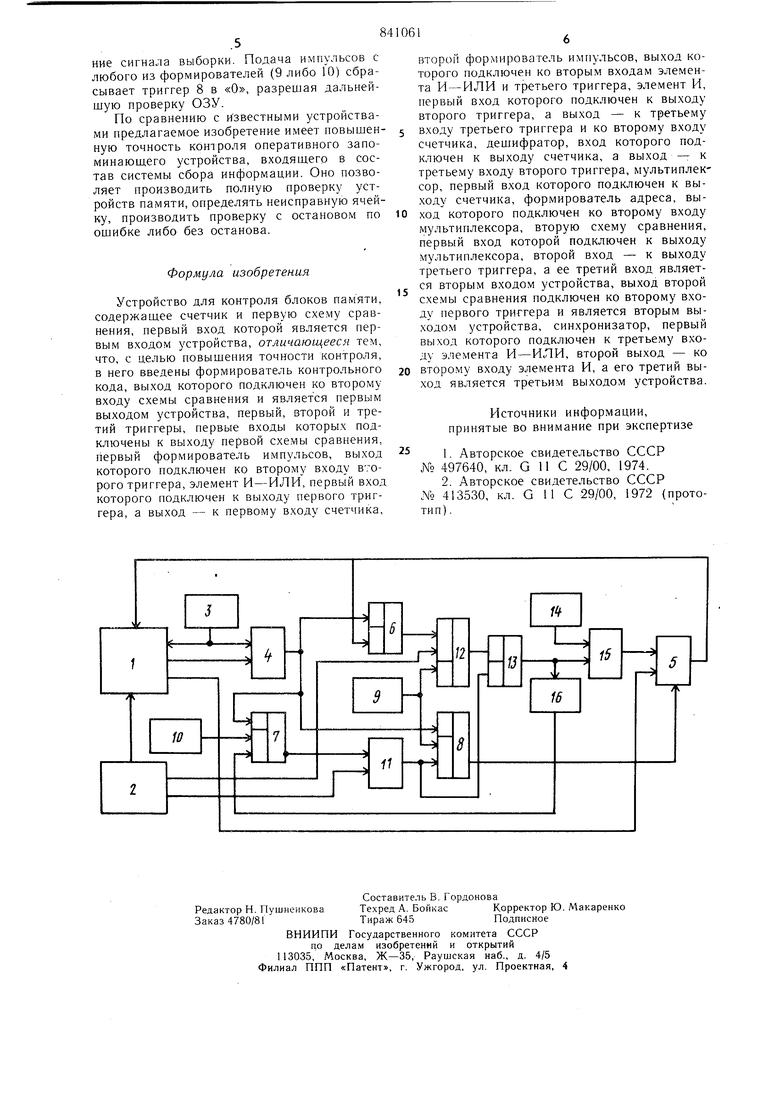

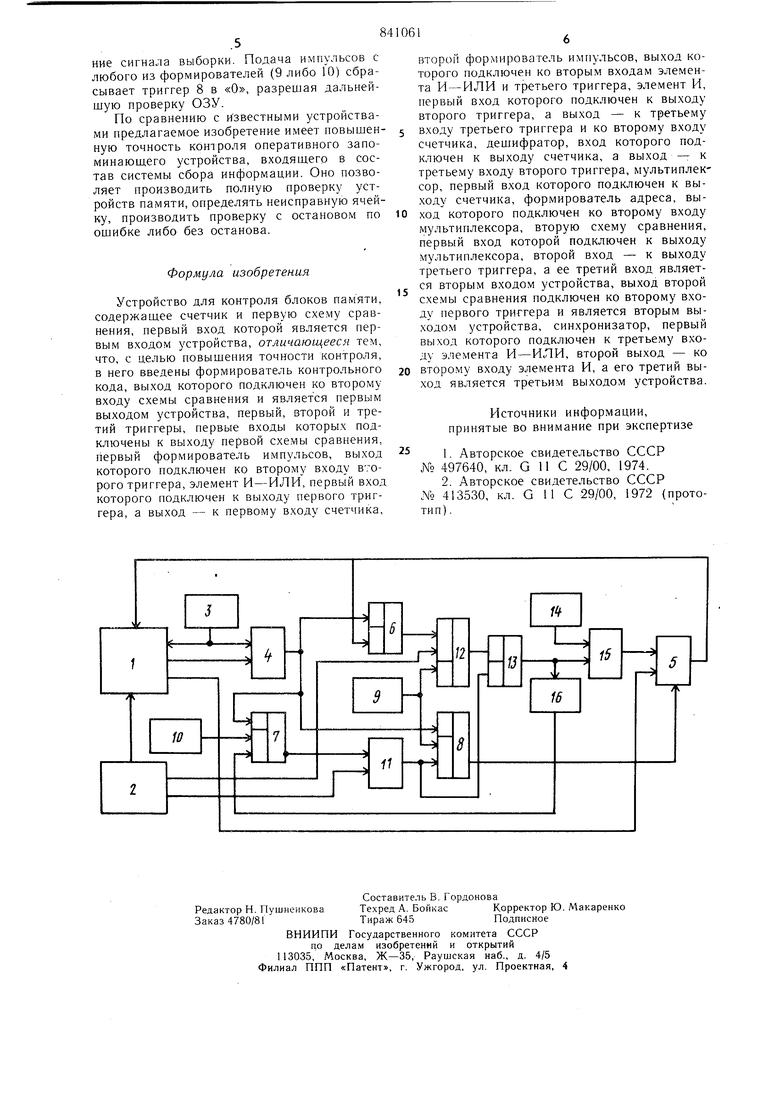

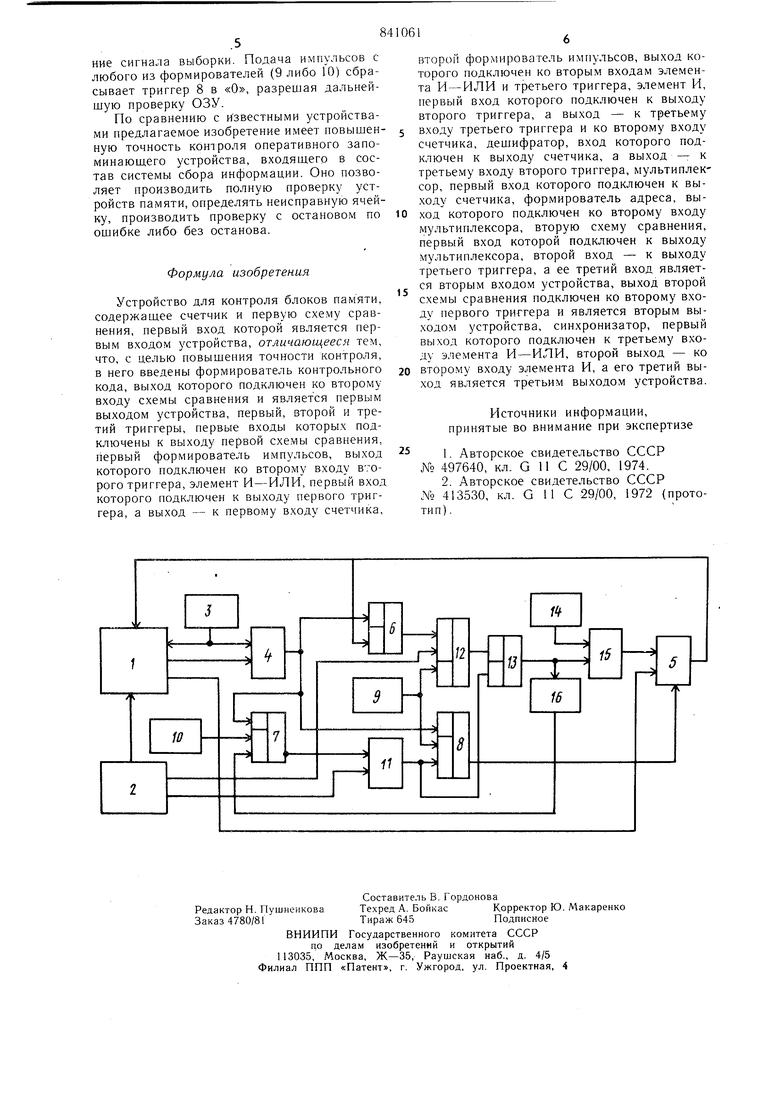

На чертеже представлена схема устройства для контроля блоков памяти.

Устройство для контроля блоков памяти содержит запоминающий блок 1 с синхронизатором 2, формирователь 3 контрольного кода, первую схему 4 сравнения, вторую схему 5 сравнения, первый 6 второй 7 и третий 8 триггеры, первый 9 и второй 10 формирователи импульсов, элемент И 11, элемент И-ИЛИ 12, счетчик 13, формирователь 14 адреса, мультиплексор 15 н дешифратор 16.

Устройство работает следующим образом.

На запоминающий блок 1, синхронизируемый синхронизатором 2, подается информация с выхода формирователя контрольного кода 3. Этот же код поступает на один вход первой схемы сравнения 4, на второй вход которой приходит считываемая из ОЗУ информация. Все триггеры сброшены в 0.

Первый триггер 6 разрешает прохождение импульсов счета от синхронизатора 2 через элемент И-ИЛИ 12 на счетный вход счетчика 13, второй триггер 7 разрешает прохождение импульсов начальной установки на вход установки счетчика 13 через элемент И 11, третий триггер 8 разрешает формированиее второй схемой сравнения 5 сигнала выборки при равенстве кодов счетчика 13, поступающего через мультиплексор 15 и адреса на кодовой шине адреса. В режиме контроля одной ячейки ОЗУ мультиплексор 15 подключает ко второй схеме сравнения 5 формирователь адреса 14.

При несовпадении записываемого и считанного кодов (сбой) в режиме контроля информации по всему массиву первая схема сравнения 4 устанавливает триггеры 6, 7, 8 и «1. Триггеры 6 и 7 разрешают подачу синхроимпульсов счета и установки соответственно на счетчик 13, триггер 8 запрешает формирование сигнала выборки при равенстве кода адреса на кодовой шине адреса и кода счетчика 13.

.Дальнейшая проверка может проводиться в последующей ячейке ОЗУ либо с первой, ячейки (с начала массива).

0 Для проверки ОЗУ с последующей ячейки второй формирователь 10 выдает импульс, поступающий через элемент И-ИЛИ 12 на счетный вход счетчика 13, увеличивая его код на «1 и сбрасывает в «О третий триггер 8, разрещая формирование сигнала вы борки при равенстве кодов на входах второй схемы совпадения 5. Сигнал выборки сбрасывает первый триггер 6, разрещая при этом синхронную с синхронизатором 2 работу счетчика 13. Следующий посл,е опроса поQ следней ячейки импульс устанавливает на счетчике код N + 1, дешифратор 16 при этом сбрась вает второй триггер 7 в «О, разрешая прохождение сигналов установки через элемент И 11 на вход сброса счетчика 13.

5 Если код счетчика 13 указывает адрес последней ячейки ОЗУ, то одиночный импульс второго формирователя 10 сбрасывает третий триггер 8, счетчик 13 переходит в состояние N -f 1 и сбрасывает второй триггер 7 через дешифратор 16. При равенстве кодов

° на входе второй схемы совпадения 5 формируется сигнал выборки, сбрасывающий первый триггер 6, разрешая дальнейший контроль ОЗУ.

5 Для проверки ОЗУ с первой ячейки выходной импульс первого формирователя 9 сбрасывает второй триггер 7, разрешая выдачу импульса начальной установки через элемент И 11 на сброс счетчика 13 и триггера 8. При опросе первой ячейки вторая схема совпадения 5 формирует сигнал выборки, который сбрасывает триггер 6, разрешая дальнейшую работу счетчика 13.

При контроле по одному адресу ко второй схеме сравнения 5 подключается формирователь 14 через мультиплексор 15. Сигнал выборки вырабатывается при обращении к ячейке, адрес которой задан формирователем 14. При сбое третий триггер 8 устанавливается в «1, запрещая формирование сигнала выборки. Подача импульсов с любого из формирователей (9 либо 10) сбрасывает триггер 8 в «О, разрешая дальнейшую проверку ОЗУ.

По сравнению с известными устройствами предлагаемое изобретение имеет повышенную точность конпроля оперативного запоминаюш,его устройства, входяшего в состав системы сбора информации. Оно позволяет производить полную проверку устройств памяти, определять неисправную ячейку, производить проверку с остановом по ошибке либо без останова.

Формула изобретения

Устройство для контроля блоков памяти, содержащее счетчик и первую схему сравнения, первый вход которой является первым входом устройства, отличающееся тем, что, с целью повышения точности контроля, в него введены формирователь контрольного кода, выход которого подключен ко второму входу схемы сравнения и является первым выходом устройства, первый, второй и третий триггеры, первые входы которых подключены к выходу первой схемы сравнения, первый формирователь импульсов, выход которого подключен ко второму входу второго триггера, элемент И-ИЛИ, первый вход которого подключен к выходу первого триггера, а выход - к первому входу счетчика.

второй формирователь импульсов, выход которого подключен ко вторым входам элемента И -ИЛИ и третьего триггера, элемент И, первый вход которого подключен к выходу второго триггера, а выход - к третьему

входу третьего триггера и ко второму входу счетчика, дешифратор, вход которого подключен к выходу счетчика, а выход- к третьему входу второго триггера, мультиплексор, первый вход которого подключен к вы.ходу счетчика, формирователь адреса, выход которого подключен ко второму входу мультиплексора, вторую схему сравнения, первый вход которой подключен к выходу мультиплексора, второй вход - к выходу третьего триггера, а ее третий вход является вторым входом устройства, выход второй

схемы сравнения подключен ко второму входу первого триггера и является вторым выходом устройства, синхронизатор, первый выход которого подключен к третьему входу элемента И-ИЛИ, второй выход - ко

второму входу элемента И, а его третий выход является третьим выходом устройства.

Источники информации, принятые во внимание при экспертизе

№ 413530, кл. G 11 С 29/00, 1972 (прототип).

Авторы

Даты

1981-06-23—Публикация

1979-09-27—Подача