1

Изобретение относится к вычислительной технике и может быть использовано для сопряжения синхронного источника с асинхронным приемником, в частности для связи устройства циклического опроса датчиков с устройством вывода информации.

Известно устройство для обмена информацией, содержащее буферный накопительный блок, дешифратор адреса, регистр чцсла, регистры текущ 1Х адресов и регистр начального адреса ш.

Недостатком этого устройства являются большие аппаратурные затраты из-за необходимости большого числа регистров текущих адресов, требующихся для осуществления произвольного порядка записи и выборки информации.

Наиболее близким по технической сущности к предлагаемому является устройство для сопряжения, содержащее буферный запоминающий регистр, даиифратор, маркерный регистр, триггер, первый и второй элементы задержки, первый и второй вентили, элемент ИЛИ-НЕ, формирователь импульса 2..

Недостаток известного устройства состоит в ограничен-ных функциональных возможностях, что не позволяет осуществлять выборку информации по годресу из основного запоминающего устройства (ЗУ).

Цель изобретения - расширение функциональных возможностей за счет обеспечения возможности вывода информации по заданному адресу.

Поставленная цель достигается

10 тем, что в устройство, содержащее буферный запоминающий блок, регистр, первый триггер, элемент задержки, элемент И, формирователь импульса и дешифратор, причем информационные

15 вход и. выход буферного запоминающего блока являются соответственно инфо мационньми входом и выходом устройства, введены синхронизатор, счетчик, второй триггер, схема срарнения,

20 сумматор по модулю два, элемент И-ИЛИ и два элемента ИЛИ, причем первый вход дешифратора соединен с первыми входами первого и второго триггеров, фО1 | ирователя импульса,

25 элемента И и первьм входом устройства, первый вход схемы сравнения соединен со вторам входом устройства, дервый выход первого триггера подключен ко второму входу формировате30ля импульса, выход которого подключен

к первому входу элемента И-ИЛИ и ерез элемент задержки к первому входу первого элемента ИЛИ, выход которого соединен со вторым входом второго триггера, а второй вход - со вторым входом схемы сравнения и выходом элемента И, второй вход которого подключён ко второму выходу первого триггера, второй вход которого соединен с выходом дешифратора и со вторым входом элемента И-ИЛИ, подключенного третьим входом к выходу схемы сравнения, третий вход схемы сравнения соединен с первым выходом синхронизатора, выход - с первым :. входом регистра и первым управляющим Егходом буферного запоминающего блока, второй выход синхронизатора подключен к четвертому входу элемента И-ИЛИ, третий выход синхронизатора соединен со вторым управляющим входом буферного запомингиощего блока, выход элемента И-ИЛИ подключен к первому входу счетчика, второй вход которого подключен к выходу второго элемента ИЛИ, а выход - ко вторым входам детпифратора и регистра и к первому входу сумматора по модулю два, выход которого подключен к адресному входу буферного запоминающего блока, второй вход сумматора по модулю два соединен с третьими входами второго триггера и дешифратора, первым входом второго элемента ИЛИ и первым выходом регистра, второй выход которого подключен ко второму входу второго элемента ИЛИ, выход второго триггера является выходом ус тройс ТВ а.

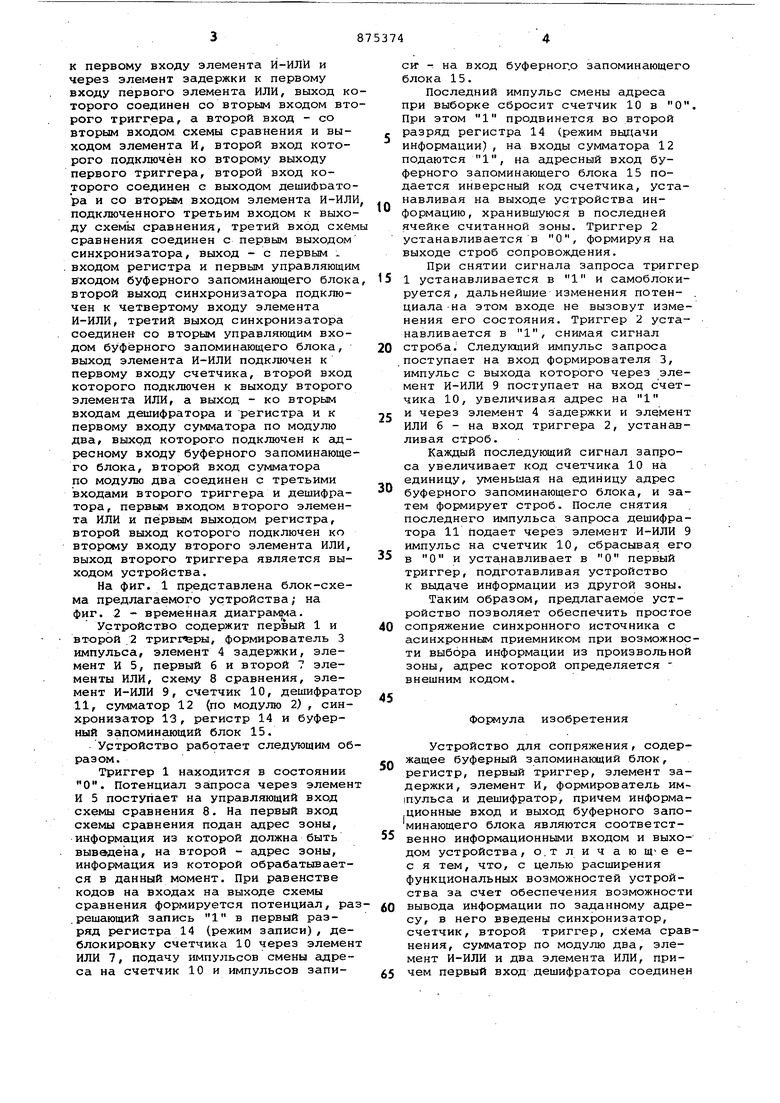

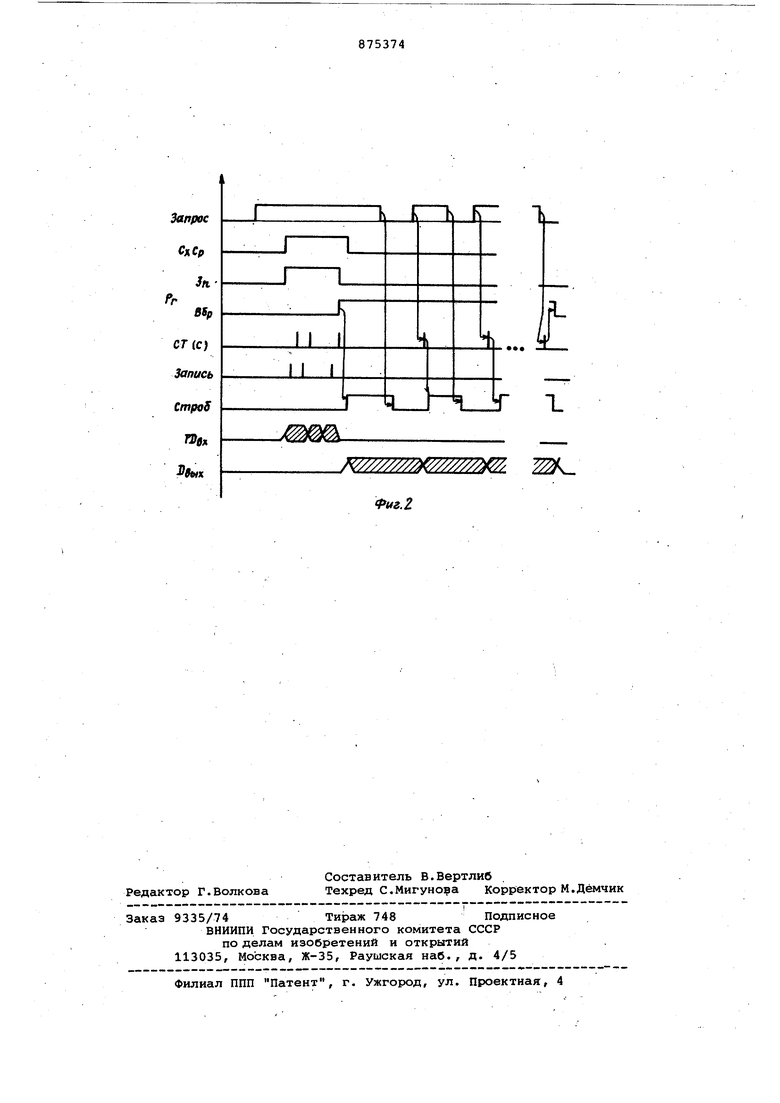

На фиг. 1 представлена блок-схема предлагаемого устройства; на фиг. 2 - временная диаграмма.

Устройство содержит первый 1 и второй 2 триггеры, формирователь 3 импульса, элемент 4 задержки, элемент И 5, первый б и второй 7 элементы ИЛИ, схему 8 сравнения, элемент И-ИЛИ 9, счетчик 10, дешифратор 11, сумматор 12 (по модулю 2) , синхронизатор 13, регистр 14 и буферный запоминающий блок 15.

Устройство работает следующим образом.

Триггер 1 находится в состоянии О. Потенциал запроса через элемент И 5 поступает на управляющий вход схемы сравнения 8. На первый вход схемы сравнения подан гщрес зоны, информация из которой должна быть выведена, на второй - адрес зоны, информация из которой обрабатывается в данный момент. При равенстве кодов на входах на выходе схемы сравнения формируется потенциал, разрешающий запись 1 в первый разряд регистра 14 (режим записи), деблокироаку счетчика 10 через элемент ИЛИ 7, подачу импульсов смены адреса на счетчик 10 и импульсов записи- - на вход буферного запоминающего блока 15.

Последний импульс смены адреса при выборке сбросит счетчик 10 в О. При этом 1 продвинется во второй разряд регистра 14 (режим вьщачи информации), на входы сумматора 12

на адресный вход буподаются

ферного запоминающего блока 15 подается инверсный код счетчика, устанавливая на выходе устройства информацию, хранившуюся в последней ячейке считанной зоны. Триггер 2 устанавливается в О, формируя на выходе строб сопровождения.

При снятии сигнала запроса тригге 1 устанавливается в 1 и самоблокируется, дальнейшие изменения потенциала-на этом входе не вызовут изменения его состояния. Триггер 2 устанавливается в 1, снимая сигнал строба. Следующий импульс запроса поступает на вход формирователя 3, импульс с выхода которого через элемент И-ИЛИ 9 поступает на вход счетчика 10, увеличивая адрес на 1 и через элемент 4 задержки и элемент ИЛИ 6 - на вход триггера 2, устанавливая строб.

Каждый последующий сигнал запроса увеличивает код счетчика 10 на единицу, уменьшая на единицу адрес буферного запоминающего блока, и затем формирует строб. После снятия последнего импульса запроса дешифратора 11 Подает через элемент И-ИЛИ 9 импульс на счетчик 10, сбрасывая его в О и устанавливает в О первый триггер, подготавливая устройство к выдаче информации из другой зоны.

Таким образом, предлагаемое устройство позволяет обеспечить простое сопряжение синхронного источника с асинхроннЕлм приемником при возможности выбора информации из произвольной зоны, адрес которой определяется внешним кодом.

Формула изобретения

Устройство для сопряжения, содержащее буферный запоминающий блок, регистр, первый триггер, элемент задержки, элемент И, формирователь им пульса и дешифратор, причем информа.ционные вход и выход буферного запоминающего блока являются соответственно информационными входом и выходом устройства, о.т л ич ес я тем, что, с целью расширения функциональных возможностей устройства за счет обеспечения возможности вывода информации по заданному адресу, в него введены синхронизатор, счетчик, второй триггер, схема сравнения, сумматор по модулю два, элемент И-ИЛИ и два элемента ИЛИ, причем первый вход дешифратора соединен

с первыми входами первого и второго триггеров, формирователя импульса, элемента И и первым входом устройства, первый вход схемы сравнения соединен со BTOptJM входом устройства, первый выход первого триггера подключен ко второму входу формирователя импульса, выход которого подключен к первому входу элемента И-ИЛИ и через элемент задержки к первому входу первого элемента ИЛИ, выход которого соединен со вторым входом второго триггера, а второй вход со вторым входом схемы сравнения и выходом элемента И, второй вход которого подключен ко второму выходу первого триггера, второй вход которого соединен с выходом дешифратора и со вторым входом элемента И-ИЛИ, подключенного третьим входом к выходу схемы сравнения, третий вход схемы сравнения соединен с первым выходом синхронизатора, выход - с первым входом регистра и первым управляющим входом буферного запоминающего блока, второй выход синхронизатора подключен к четвертому входу элемента

И-ИЛИ, третий выход синхронизатора соединен со вторым управляющим входом буферного запоминающего блока, выход элемента И-ИЛИ подключен к первому входу счетчика, второй вход которого подключен к выходу второго элемента ИЛИ, а выход - ко вторым входам дешифратора и регистра и к первому входу сумматора по модулю два, выход которого подключен к адресному входу буферного запоминаю0щего блока, второй вход сумматора по модулю два соединен с третьими входами второго триггера и дешифратора, первым Ьходом второго элемента ИЛИ и первым выходом регистра,

5 второй выход которого подключен ко второму входу второго элемента ИЛИ, выход второго триггера является выходом устройства.

Источники информации,

0 принятые во внимание при экспертизе

1.Авторское свидетельство СССР №410392, кл, G 06 F 3/04, 1971.

2.Авторское свидетельство СССР №488202, кл, G Об F 3/04, 1973 (прототип) .

5

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля блоковпАМяТи | 1979 |

|

SU841061A1 |

| УСТРОЙСТВО УПРАВЛЕНИЯ ПЕРЕДАЧЕЙ ДАННЫХ В КАНАЛЕ МНОЖЕСТВЕННОГО ДОСТУПА | 2002 |

|

RU2233038C1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ВЫЧИСЛИТЕЛЬНОЙ МАШИНЫ С КАНАЛАМИ СВЯЗИ | 1990 |

|

RU2020565C1 |

| Буферное запоминающее устройство | 1986 |

|

SU1361632A1 |

| НАКОПИТЕЛЬ ИМПУЛЬСНЫХ СИГНАЛОВ | 1991 |

|

RU2089043C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| ПОДВИЖНЫЙ ПЕЛЕНГАТОР | 2005 |

|

RU2298804C2 |

| МАГИСТРАЛЬНО-МОДУЛЬНАЯ ВЫЧИСЛИТЕЛЬНАЯ СИСТЕМА | 2013 |

|

RU2564626C2 |

| УСТРОЙСТВО ОБНАРУЖЕНИЯ ПЕРИОДИЧЕСКИХ ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ И ОЦЕНКИ ИХ ПЕРИОДА | 1990 |

|

RU2033617C1 |

| ПОДВИЖНЫЙ ПЕЛЕНГАТОР | 1997 |

|

RU2124222C1 |

Авторы

Даты

1981-10-23—Публикация

1980-02-22—Подача