(54) МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения процессора с каналами связи | 1978 |

|

SU763882A1 |

| Многоканальное устройство приоритета для распределения заявок по процессорам | 1985 |

|

SU1327105A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1990 |

|

SU1702380A1 |

| Устройство для распределения приоритетных заявок по процессорам | 1987 |

|

SU1495795A1 |

| Устройство для обмена информацией управляющей вычислительной машины с объектами управления | 1982 |

|

SU1030792A1 |

| Устройство для сопряжения абонентов с каналом передачи данных | 1986 |

|

SU1357969A2 |

| Устройство для контроля памяти | 1981 |

|

SU985831A1 |

| Устройство для обмена информацией | 1982 |

|

SU1048468A1 |

| Устройство для приоритетного распределения абонентов | 1985 |

|

SU1285617A1 |

| МНОГОКАНАЛЬНОЕ УСТРОЙСТВО ПРИОРИТЕТА | 2002 |

|

RU2231111C2 |

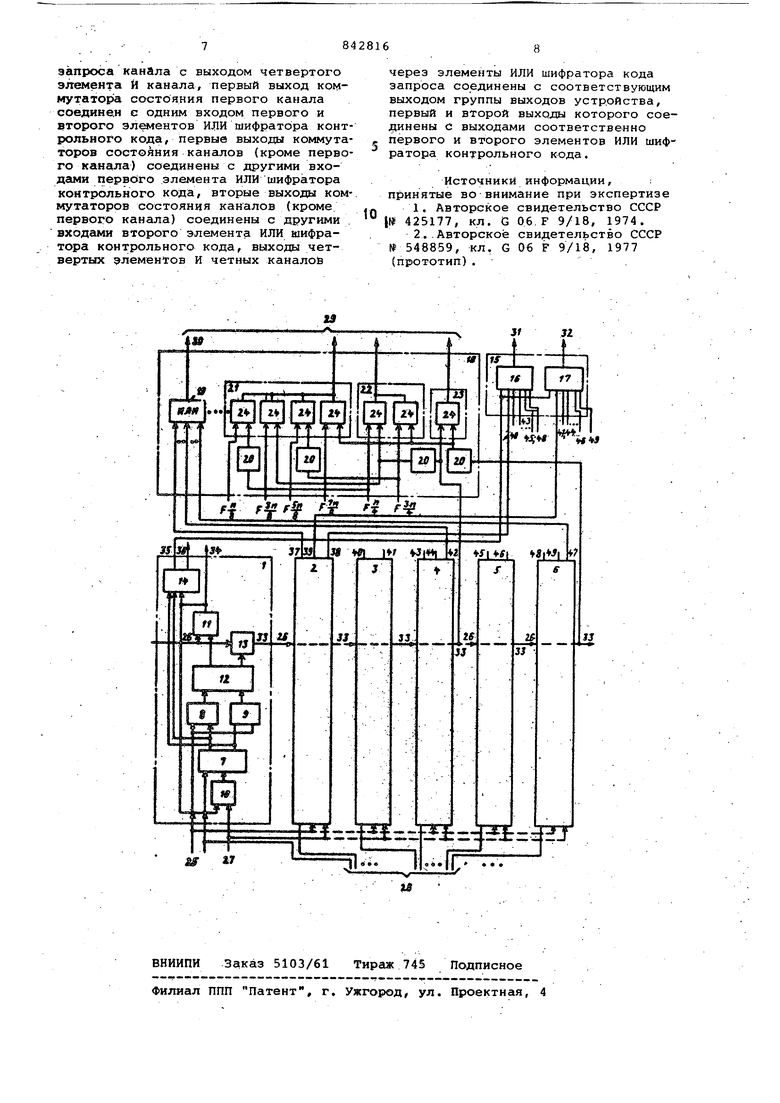

Изобретение относится к вычислительной технике, в частности к устройствам приоритета и может быть использовано для управления обращением к некоторому совместно используемому ресурсу. Известно многоканальное устройство приоритета, содержащее регистрзапросов, вспомогательные регистры, элементы И, ИЛИ, НЕ, элементы ЗАПРЕТ tl . Недостаток устройства состоит в том, что оно имеет малую надежность из-за отсутствия схемы контроля и довольно сложны по структуре. Наиболее близким к изобретению по технической сущности и достигаемому результату является многоканаль ное устройство приоритета, содержаще регистр, шифратор, блок очередности обслуживания, блок управления элементы И, ИЛИ, причем группа выходов каналов соединена с соответствующими группами входов блока упра вления, выход блока управления соеди нен со входами регистра, выход которого является выходом устройства 2 Недостаток устройства состоит в том, что оно требует значительных затрат оборудования для своей реализации. Цель изобретения - сокращение Оборудования. Поставленна-я цель достигается тем, что в многоканальное устройство приоритета, содержащее шифратор кода запроса, выполненный в виде элементов И, ЕЕ и элемента ИЛИ, шифратрр контрольнрго кода, построенный из элементов ИЛИ, а в каждом канале триггер запроса, предварительный триггер запроса, четыре элемента И, элементы ЗАПРЁТ, причем первый вход устройства соединен с первыми входами первых элементов И каналов, второй Ёход устройства соединен с Ьервымй входами второго и третьего элементов И канала, третий вход устройства соединен с-первыми входами четвертого эличента И и элемента ЗАПРЕТ первого канала, каждый «ход групп входов устройства соединен с первым входом предварительного триггера заnjioca, соответствующего канала, выход элемента ЗАПРЕТ канала соединен с первыми входами четвертого элемента И и элемента ЗАПРЕТ последующего канала, выходы шифратора кода запроса являются группой выходов устройстt.аи первый, второй выходы предварительного триггера, запроса канала соединен со вторыми входами соответственно второго и третьего элементов И канала, выходы второго и треть его элементов И канала соединены соответственно с первым и вторым входами триггера запроса канала, первый I второй выходы триггера запроса канал : соединены со вторы14и входайи соответ ственно четвертого элемента И и элемента ЗАПРЕТ канала, выход четвертого элемента И канала соединей со вто Е«лм входом первого элемента И канала, выход первого элемента И канала соединен со вторым входом пердварительного триггера запроса канала, элементы И шифратора кода запроса объединены в К групп (по числу разрядов кода без единицы) по m( ,2,..К номер группы) элементов в группе, выходы элементов И каждой группы шифратора кода запроса соединены с соответствующим выходом группы выходов устройства, выход элемента ЗАПРЕТ п-го канала соединен через соответствующий элемент НЕ шифратора,кода запроса с первыми входами 2 -ых элементов И каждой группы элементов И шифратора кода Запроса, выход элемента ЗАПРЕТ -§канала соединен со вторым входом элемента И первой группы элементов -И шифратора кода запроса и через соответствующий элемент НЕ шифратор кода запроса с первыми входами ( ых элементов И (кроме i-1) в каждой группе элементов И шифратора кода запроса, первый вход j-ro (,...,m элемента И i-ой (кроме ) группы элементов И шифратора кода запроса соединен с выходом элемента ЗАПРЕТ ( ) канала; второй вход каждого нечетног.о элемента И i-ой (,.,,,т) группы элементов И шифратора кода запроса соединен через соответствующий элемент НЕ шифратор кода запроса с выходом элемента ЗАПРЕТ .( )-ого канала, каждый ка нал содержит коммутатор состояния, входы которого соединены с первым, выходами предварительного триггера запроса канала и с выходом четвертого элемента И канала, первый выход коммутатора состояния пер вого канала соединен с одним входом первого и второго элементов ИЛИ шиф ратора контрольного кода, первые выходы коммутаторов состЬяния каналов (кроме первого канала) соединен с другими входами первого элемента ИЛИ шифратора «онтрольного кода, вторые выходы коммутаторов состояни каналов (кроме первого канала) соединены о другими входами второго элемента ИЛИ шифратора контрольного кода, выходы четвертых элементов И четных каналов через элементы ИЛИ шифратора кода запроса соединены с соответствующим выходом группы выходов устройства, первый и второй выходы. которого соединены с выходами соответственно первого и второго элементов ИЛИ шифратора контрольного кода. Структурная схема устройства приведена на чертеже. Многоканальное устройство приоритета содержит каналы 1-6, каждый из которых содержит предварительный триггер 7 запроса, элементы И 8-11, триггер 12 запроса, элемент ЗАПРЕТ 13, коммутатор 14 состояния. Устройство содержит также шифратор 15 контрольного кода с элементами ИЛИ 16 и 17 шифратор 18 кода запроса с элементом ИЛИ 19, элементами НЕ 20, с группами21-.23 элементов И 24, входы 25-27, группу 28 входов, группу 29 выходов, выходы 30-32, Каналы устройства имеют 33-49, При этом каналы 1-6 соответствуют каналам 1 и 2, Устройство работает следующим образом (описана работа одного ) , На входы 28 поступают сигналы от абонентов Запрос, являющиеся заявкой абонента на обслуживание, которые запоминаются на предварительном триггере 7 запроса. По сигналу Опрос через вход 25 заявка, записанная на предварительном триггер1е 7 запроса переписывается через элементы 8 и 9 на триггер 12 запроса. Разрешение Сигнал через вход 26 управляет выборкой заявки элементом И 11, Положительный уровень на первом слева выходе триггера 12 запроса указывает на наличие заявки на. триггер 12, При этом сигналом низкого уровня Со второго выхода этого триггера запрещается распространение сигнал.а Разрешение элементом ЗАПРЕТ 13. через выход 33, Если на триггере 12 запроса нет заявки, то на первом выходе триггера 12 и на выходе элемента И 11 будет низкий уровень, а сигнал высокого уровня на втором выходе триггера 12 разрешает распространение сигнала Разрешение через элемент ЗАПРЕТ 13 на выход 33, При отсутствии сигнала Разрешение на входе 26 заявка не выбирается вне зависимости от состояния.триггера 12 запроса. После выборки заявки сигналом с выхода элемента И 11 управляется выдача состояния предварительного триггера 7 запроса через коммутатор 14 состояния в шифратор 15 контрольного кода. Сигналы с выхода элемента И 11 четных каналов 2,4,6 а также сигналы запрета с выхода 33 каналов 1-6 после выборки заявки поступают в шифратор 18 кода запроса, который формирует двоичный код выбранного запроса. После выбЪра заявки абонента с выхода шифратора

18 кода запроса в процессор (не по казан) поступает двоичный код выбраного абонента, а с выхода шифратора 15 контрольного кода в схему контроля процессора выдается контрольный код выбранного абонента, с выхода 33 последнего п-го канала 6 в процессор поступает сигнал прерывании для обслуживания запроса. После окончания обработки запроса происходит сброс запроса, хранящегося на триггере 7 сигналом Сброс через вход 27. Выборка триггера 7, который необходимо сбросить, производится сигналом, поступающим через вход элемента И 10 от элемента И 11. После сброса триггера 7 в , О через коммутаторы 14 состояний в шифратор 15 контрольного кода выдается другое значение сигналов с выходов 35, 36, 38, 39, 43, 44, 48, 4 и с его выходов 31 и 32 поступает иверсное значение сформированного до этого кода для контроля сброса Заявка абонента. Триггер 12 запроса устанавливается по состоянию триггера 7 при поступлении сигнала Опрос .

Таким образом, благодаря использованию для формирования кода выбранного абонента только сигналов выборки и сигналов запрета четных каналов возможно сократить, число элементов в шифраторе 18 кода запроса с элементов НЕ и 2п элементов И (при двухкодОвом выражени элементо И) до элементов НЕ и S элментов И и J элементов ИЙЙГ, где (например, при наличии в известном устройстве 16-ти каналов потребовалось бы 16 элементов НЕ и 32 элемента И в двухкодовом выражении, а в предлагаемом изобретении только 4 элемента НЕ, 7 элементов И и 4 элемента ИЛИ, т.е. в три раза меньше)..

Введение в каждый канал 1-6 коммутатора 14 состояния с соответствующими соединениями позволило более эффективно контролировать не только правильную выборку и шифрацию кода выбранного абонента, но и сброс предварительного триггера 7 запроса после обслуживания запроса абонента.

Формула изобретения

Многоканальное устройство приоритета, содержащее шифратор кода запроса, выполненный на элементах И, НЕ и элементе ИЛИ, шифратор контрольного кода, выполненный на элементах ИЛИ, а в каждом канале триггер запроса, предварительный триг-гер запроса, четыре элемента И, элементы ЗАПРЕТ, причем первый вход устройства соединен с первыми входами первых элементов И каналов, второй вход устройства соединен с первыми входами второго и третьего элементов и канала, третий вход устройства соединен с первыми входами четвертого элемента И и элемента ЗАПРЕТ первого канала, каждый вход группы устройства соединен с первым входом предварительного триггера запроса соответствующего канала,

Q выход элемента ЗАПРЕТ канала соединен с первыми входами четвертого элемента И элемента ЗАПРЕТ последующего канала, входы шифратора кода запроса являются группой выходов устройства, первый, второй выходы

5 предварительного триггера запроса канала соединены со вторыми входами соответственно второго и тр етьего элементов И канала, выходы второго и третьего элементов И канала соединены соответственно с первьоми вторым входами триггера запроса канала, первый, второй выходы триггера запроса канала соединены со вторьамй входами соответственно четвертого элемента И и элемента ЗАПРЕТ канала, выход четвертого элемента И канала соединен со вторым входом первого элемента И канала, выход первого элемента И канала соединен со

Q вторым входом предварительного триггера запроса канала, отличающееся тем, что, с целью сокращения оборудования, элементы И шифратора кода запроса объединены в К групп (по числу разрядов кода без

5 единицы по m( ,2,...,К номер группы) элементов в группе, выходы элементов И каждой группы шифратора кода запроса соединены с соответствую щими выходом группы выходов устройства, выход элемента ЗАПРЕТ канала соединен через соответствующий элемент НЕ шифратора кода запроса с первыми входами (21-1)-ых элементов И каждой группы элементов И шифратора

5 кода запроса, выход элемента ЗАПРЕТ канала соединен со вторым входом элемента И первой группы элементов И шифратора кода запроса и через соответствуюнщй элемент НЕ шифратора

Q кода запроса - с первыми входами ( (2)-ых элементов И (кроме ) в каждой группе И шифратора кода запроса, первый вход j-ro (,...,т) элемента И i-ой (кроме ) группы- элементов И шифратора кода запроса

соединен с выходом элемента ЗАПРЕТ С 1 )-гоканала; второй вход каждого нечетного элемента И 1-ой (кроме ) группы элементов И шифратора кода запроса соединен череэ

0 соответствующий элемент НЕ шифратора кода запроса с выходом элемента ЗАПРЕТ jgTJbj канала, каждый канал содержит коммутатор состояния, входы которого соединены с первым, втогялм

5 выходами предварительного триггера

запроса канала с выходом четвертого элемента И канала, первый выход коммутатора состояния первого канала соединен с одним входом первого и второго элементов ИЛИ шифратора контрольного кода, первые выходы коммутаторов состояния каналов (кроме первого канала) соединены с другими входами первого элемента ИЛИ шифратора контрольного кода, вторые выходы коммутаторов состояния каналов (кроме первого канала) соединены с другими входами второго элемента ИЛИ шифратора контрольного кода, выходы четвертых элементов И четных каналов

Sff У

через элементы ИЛИ шифратора кода запроса соединены с соответствующим выходом группы выходов устройства, первый и второй выходы которого соединены с выходами соответственно первого и второго элементов ИЛИ шифратора контрольного кода.

Источники информации, : принятые во внимание при экспертизе

31 П

WM

Авторы

Даты

1981-06-30—Публикация

1978-05-22—Подача