(54) ПОСТОЯННОЕ ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО . .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для реализации быстрых преобразований в базисах дискретных ортогональных функций | 1985 |

|

SU1292005A1 |

| Ассоциативное запоминающее устройство | 1979 |

|

SU826421A1 |

| Резервированное запоминающее устройство | 1982 |

|

SU1070608A1 |

| Постоянное запоминающее устройство | 1979 |

|

SU824312A1 |

| Ассоциативное запоминающее устройство | 1982 |

|

SU1056269A1 |

| Устройство для аппаратурной трансляции | 1983 |

|

SU1144108A1 |

| Запоминающее устройство | 1980 |

|

SU898506A1 |

| Центральный процессор | 1979 |

|

SU960830A1 |

| Запоминающее устройство | 1980 |

|

SU868835A1 |

| Ассоциативное запоминающее устройство | 1980 |

|

SU926717A1 |

1

Изобретение относится к запоминающим устройствам и может быть использовано в цифровых электронных вычислительных машинах специального и общего назначения, а также в технических средствах автоматизированных систем управления технологическими процессами в качестве постоянного запоминающего устройства для хранения, спецпрограмм, микропрограмм, констант и т.п.

Устройство может быть использовано как датчик опорной цифровой последовательности большой длины для шифровки и, соответственно, дешифровки информации по открытым каналам связи.

Известное постоянное запоминающее устройство представляет собой накопительную матрицу, в которой на каждый бит информации используется не менее одного физического компонента, например, ферритового сердечника 1.

Недостатком этого устройства являются большие аппаратурные затраты.

Наиболее близким техническим решением к предлагаемому является постоянное запоминающее устройство, содержащее регистр адреса, который через дешифратор соединен с адресными шинами, группы многовходовых элементов ИЛИ, кольцевые пересчетные с.хемы, кодовый счетчик, элемент задержки и шину установки в исходное состояние 2.

Одйако это устройство обладает рядом существенных недостатков. Одним из них является необходимость хранить всю информацию на кольцевых пересчетных схемах, что определяет соответствующие аппаратурные затраты. Кроме того, устройство требует несколько групп многЬвходовых элементов ИЛИ, связанных с адресными шинами и управляющих работой кольцевых пересчетных схем. Указанные обстоятельства сужают область применения устройства.

Цель изобретения - упрощение устройства и расширение области его применения за счет обеспечения возможности хранения и К-ичной информации ().

Поставленная цель достигается тем, что в постоянное запоминающее устройство, содержащее накопитель, один из входов которого соединен с выходом регистра сдвига, введены дополнительный накопитель, генератор тактовых импульсов, группы элементов И, логический блок и блок местного управления, причем выход накопителя подключен к одним из входов элементов И первой группы и блока местного управления, которого соединен с первым входом регистра сдвига, выход генератора тактовых импульсов соединен с одним из входов ,фполнительного накопителя, другие входы блока местного управления и дополнительного накопи1теля соединены и -являются входом устройства, выход логического блока и первый выход дополнительного накопителя подключены к другим входам накопителя, второй выход дополнительного накопителя соединен со вторым входом регистра сдвига, . одни из входов элементов И второй группы соединены с Выходом регистра сдвига, другие рходы элементов И и вход логического блока соединены с первым выходом дополнительного накопителя, выходы элементов И являются выходами устройства.

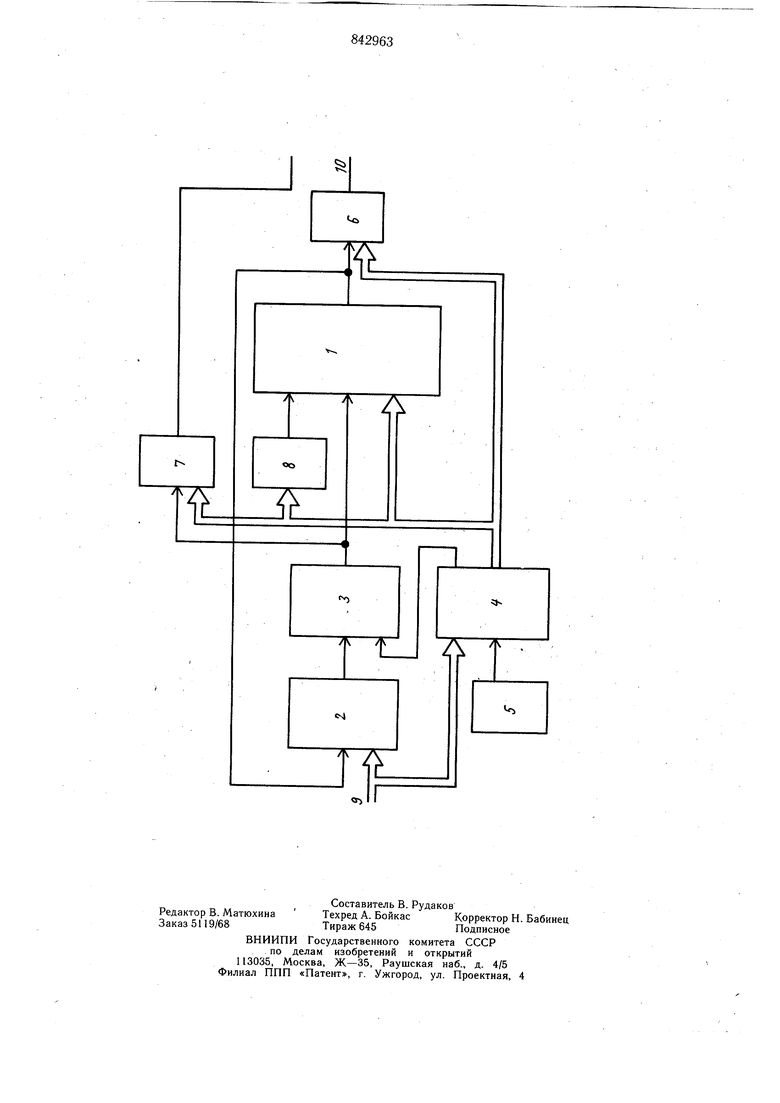

На чертеже изображена структурная схема постоянного запоминающего устройства для хранения К-ичной информации.

Устройство содержит накопитель, реализованный, например, на многофункциональном элементе 1, блок 2 местного управления, регистр 3 сдвига, дополнительный накопитель 4, выполненный, например, на К-ичном регистре и служащий для хранения констант, генератор 5 тактовых импульсов, первую б и вторую 7 группы элементов И, служащие соответственно для считывания последовательного и параллельного кодов хранимой информации, логический блок 8, реализованный также на элементах И.

Один из входов накопителя 1 соединен с выходом регистра 3, а выход - с одними из входов элементов И 6 и блока 2, выход которого соединен с первым входом регистра 3. Выход генератора 5 соединен с одним из входов накопителя 4, другие входы блока 2 и накопителя 4 соединены и являются входом 9 устройства. Выход блока 2 и первый выход накопителя 4 подключены к другим входам накопителя 1. Второй выход накопителя 4 соединен со вторым входом регистра 3. Одни из входов элементов И 7 соединены с выходом, регистра 3, другие входы элементов И 6 и 7 и вход блока 8 соединены с первым выходом накопителя 4. Выходы элементов И 6 и 7 являются выходами 10 устройства.

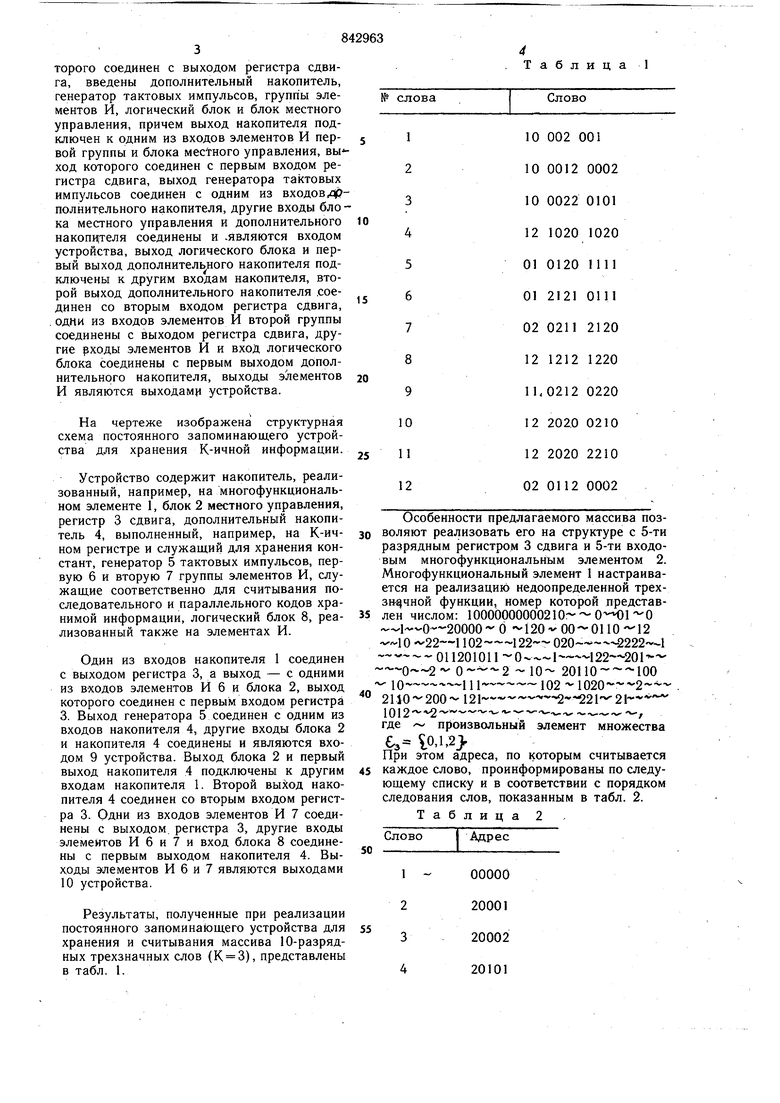

Результаты, полученные при реализации постоянного запоминающего устройства для хранения и считывания массива 10-разрядных трехзначных слов (К 3), представлены в табл. 1.

Особенности предлагаемого массива позволяют реализовать его на структуре с 5-ти разрядным регистром 3 сдвига и 5-ти входовым многофункциональным элементом 2. Многофункциональный элемент 1 настраивается на реализацию недоопределенной трехзн чной функции, номер которой представлен числом: 10000000000210:0 1 0

-1-О--20000--О 120-00-0110- 12

-10- 22-1102122- 020 --2222-1

011201011-0 - 1-122-201 -

10 20110100

10111-102 1020 2 2110 200

1012-- - -- -v-o..

где произвольный элемент множества е,, 0,1,2

При этом адреса, по которым считывается 5 каждое слово, проинформированы по следующему списку и в соответствии с порядком следования слов, показанным в табл. 2.

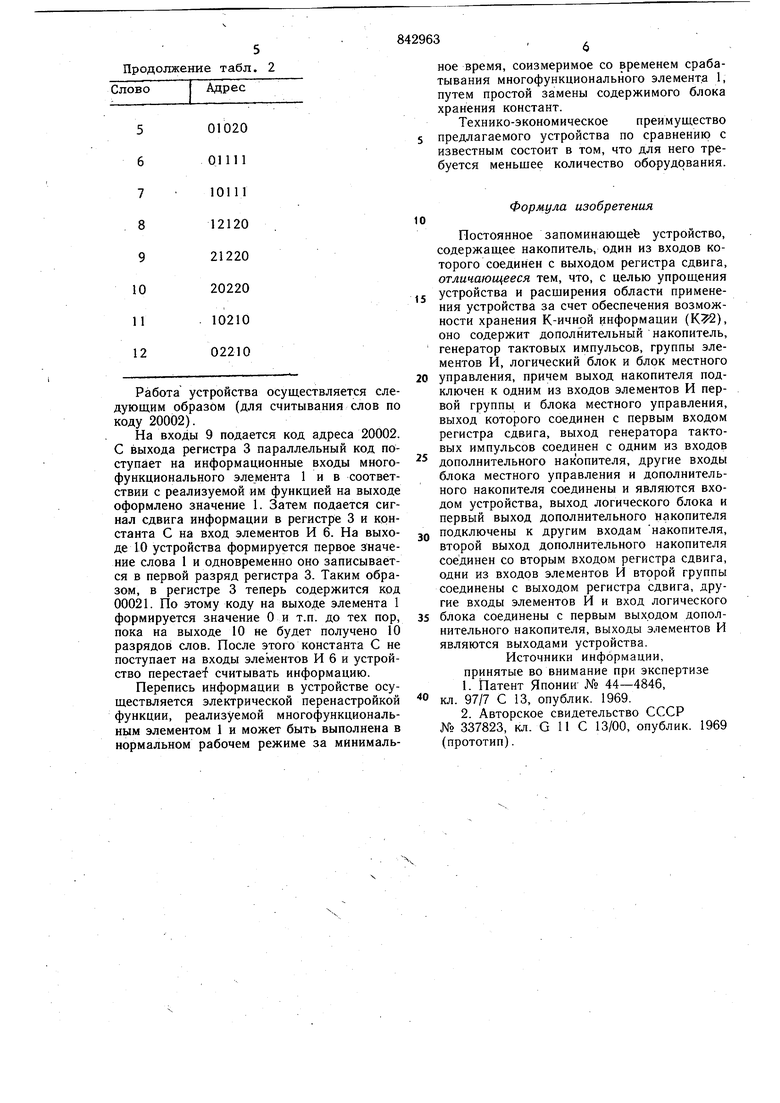

Таблица 2

Слово

Адрес

00000 20001 20002 20101

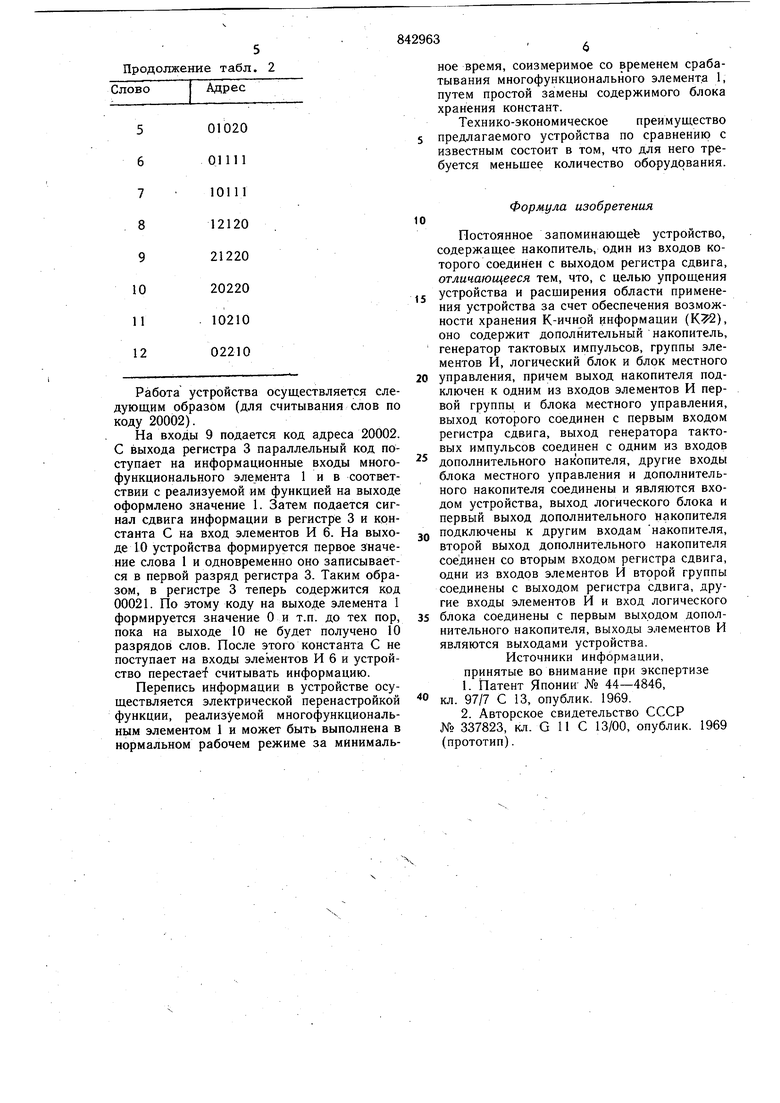

Продолжение табл. 2

Работа устройства осуществляется следующим образом (для считывания слов по коду 20002).

На входы 9 подается код адреса 20002. С выхода регистра 3 параллельный код поступает на информационные входы многофункционального эле мента 1 и в соответствии с реализуемой им функцией на выходе оформлено значение 1. Затем подается сигнал сдвига информации в регистре 3 и константа С на вход элементов И 6. На выходе 10 устройства формируется первое значение слова 1 и одновременно оно записывается в первой разряд регистра 3. Таким образом, в регистре 3 теперь содержится код 00021. По этому коду на выходе элемента 1 формируется значение О и т.п. до тех пор, пока на выходе 10 не будет получено 10 разрядов слов. После этого константа С не поступает на входы элементов И 6 и устройство перестает считывать информацию.

Перепись информации в устройстве осуществляется электрической перенастройкой функции, реализуемой многофункциональным элементом 1 и может быть выполнена в нормальном рабочем режиме за минимальное время, соизмеримое со временем срабатывания многофункционального элемента 1, путем простой замены содержимого блока хранения констант.

Технико-экономическое преимущество предлагаемого устройства по сравнению с известным состоит в том, что для него требуется меньшее количество оборудования.

Формула изобретения

10

Постоянное запоминающей устройство, содержащее накопитель, один из входов которого соединен с выходом регистра сдвига, отличающееся тем, что, с целью упрощения

устройства и расщирения области применения устройства за счет обеспечения возможности хранения К-ичной информации (К), оно содержит дополнительный накопитель, генератор тактовых импульсов, группы элементов И, логический блок и блок местного

управления, причем выход накопителя подключен к одним из входов элементов И первой группы и блока местного управления, выход которого соединен с первым входом регистра сдвига, выход генератора тактовых импульсов соединен с одним из входов дополнительного накопителя, другие входы блока местного управления и дополнительного накопителя соединены и являются входом устройства, выход логического блока и первый выход дополнительного накопителя

подключены к другим входам накопителя, второй выход дополнительного накопителя соединен со вторым входом регистра сдвига, одни из входов элементов И второй группы соединены с выходом регистра сдвига, другие входы элементов И и вход логического

блока соединены с первым выходом дополнительного накопителя, выходы элементов И являются выходами устройства.

Источники информации, принятые во внимание при экспертизе

№ 337823, кл. G 11 С 13/00, опублик. 1969 (прототип).

Авторы

Даты

1981-06-30—Публикация

1978-09-13—Подача