(5) ЦЕНТРАЛЬНЫЙ ПРОЦЕССОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Процессор цифровой вычислительной машины | 1979 |

|

SU1164723A1 |

| Трехканальная мажоритарно-резервированная система | 1981 |

|

SU1104696A1 |

| Центральный процессор | 1980 |

|

SU890400A1 |

| Асинхронное устройство управления | 1979 |

|

SU826351A1 |

| Устройство для обработки данных | 1990 |

|

SU1742813A1 |

| Арифметико-логическое устройство двухадресной ЦВМ | 1980 |

|

SU890390A1 |

| Вычислительное устройство для реализации логических функций | 1983 |

|

SU1269130A1 |

| Операционное устройство процессора | 1979 |

|

SU809189A1 |

| Устройство управления микропроцессором | 1983 |

|

SU1156072A1 |

| Микропрограммный процессор | 1982 |

|

SU1070557A1 |

Изобретение относится к вычислительной технике и предназначено для построения быстродействующих вычислительных машин.

Известно устройство, содержащее регистры, схему десятичного заполнителя, буфер перекоса, соединительный узел сумматора, схему сдвига вправо, сумматор, узел переноса, триггеры состояний переноса и десятичный кор- jo ректор младших и старших значащих разрядов l.

Недостатком данного устройства является то, что отсутствует возможность при выполнении команд сдвига одновре- is менно производить сдвиг операнда и уменьшить константу, задающую число сдвигов, с последующим анализом окончания сдвига. Это существенно сокращает быстродействие устройства при вы- 20 полнении команд сдвига, что снижает, эффективное быстродействие вычислительной машины в целом.

Известен также центральный процессор, содержащий устройство управления, арифметическое устройство, состоящее из блока управления и блока операций, запоминающее устройство, регистры команд, кодов арифметических операций, групп кодов, схемы разрешения запроса памяти и готовности арифметического устройства С 2 .

Однако в этом центральном процессоре отсутствуют средства распараллеливания выполнения команд сдвига в арифметическом устройстве, при котором можно было бы одновременно производить как сдвиг операнда, так и уменьшение константы сдвига на величину произведенного сдвига с анализом окончания сдвига. Это снижает эффективное быстродействие центрального процессо(эа.

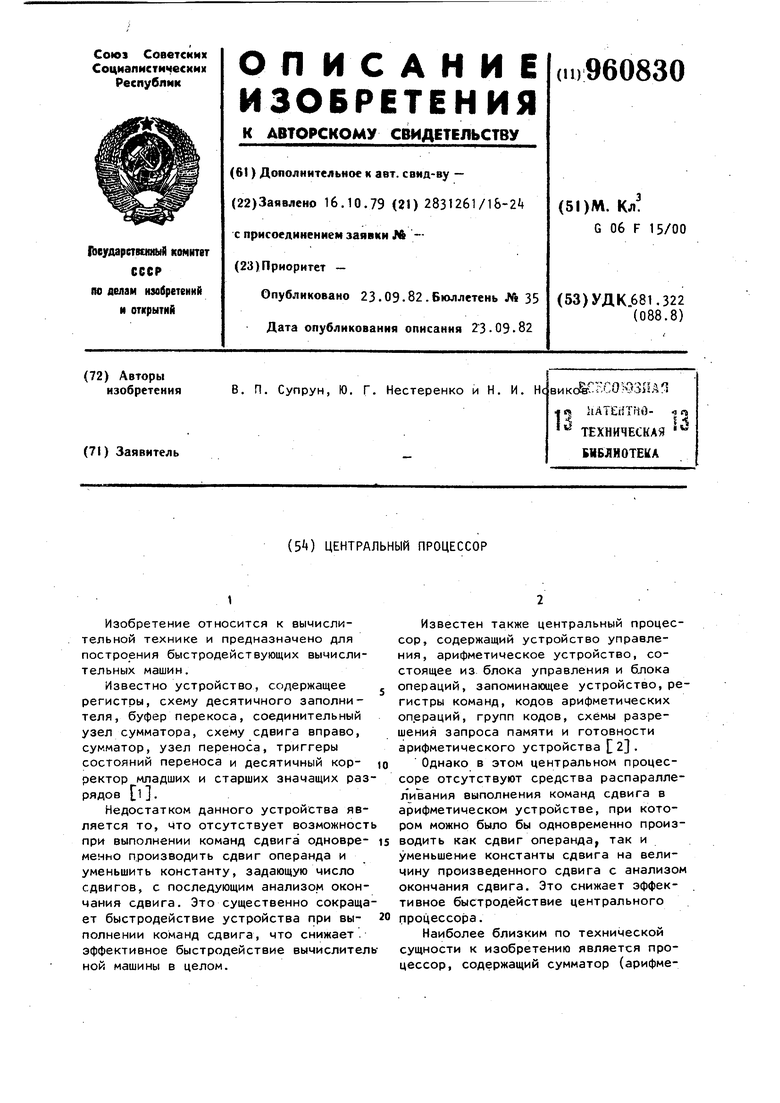

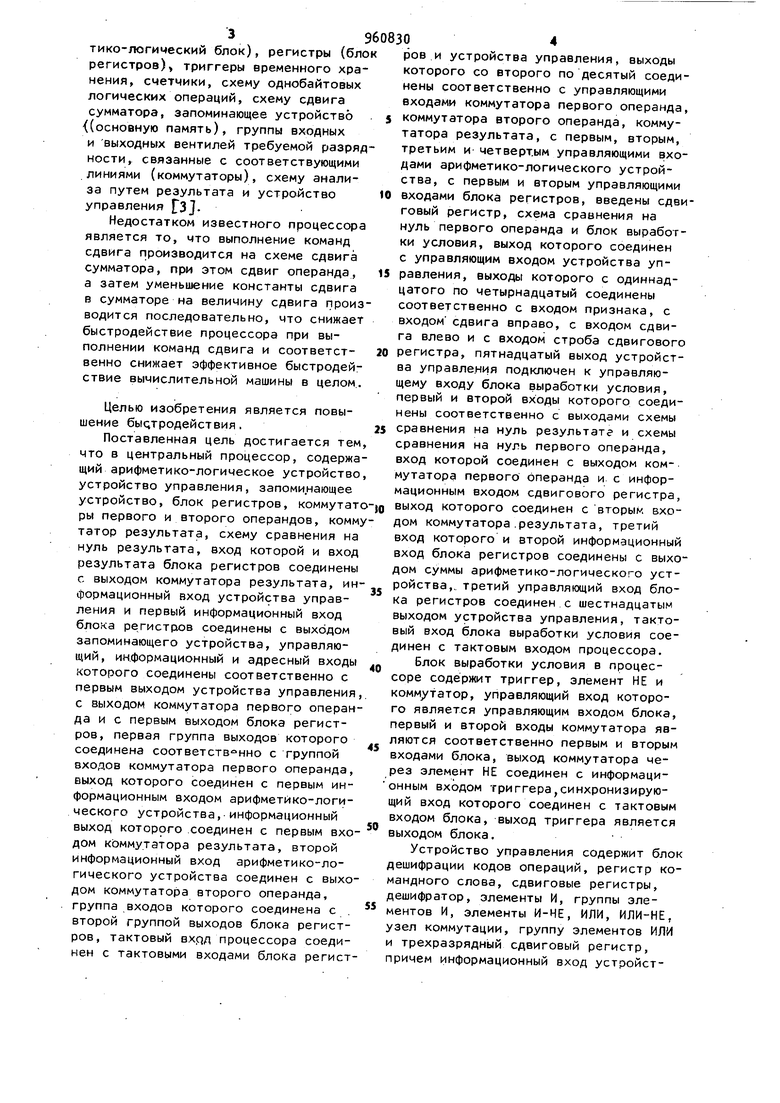

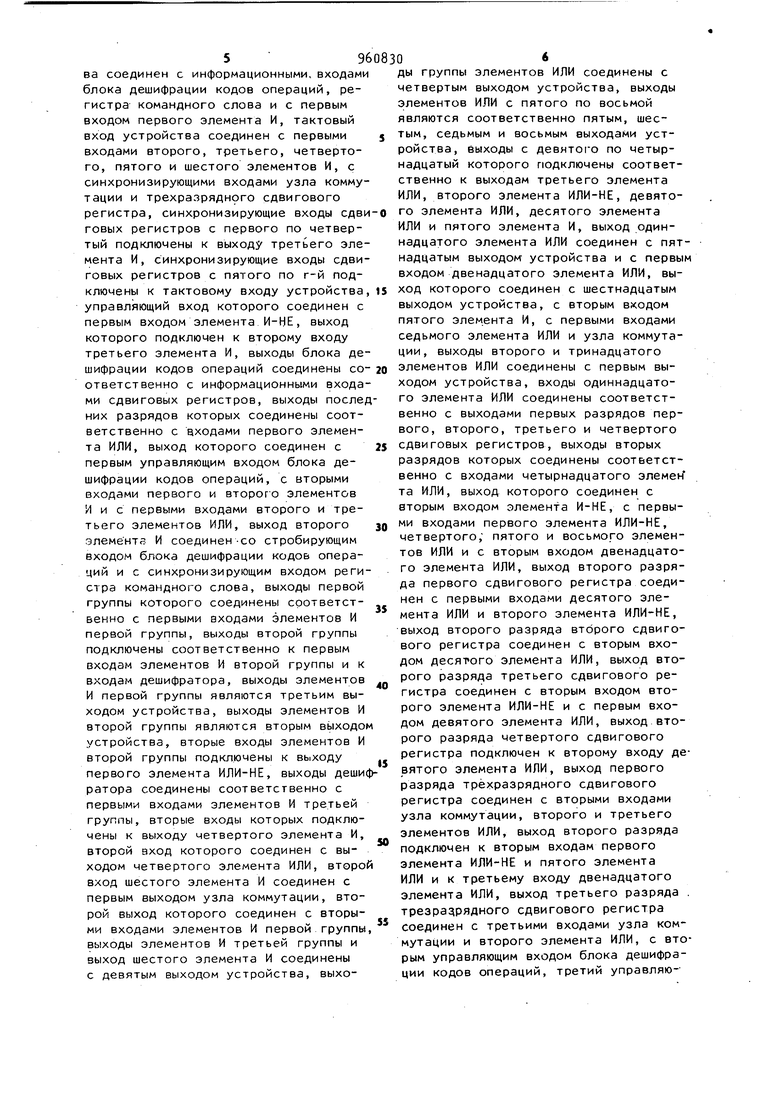

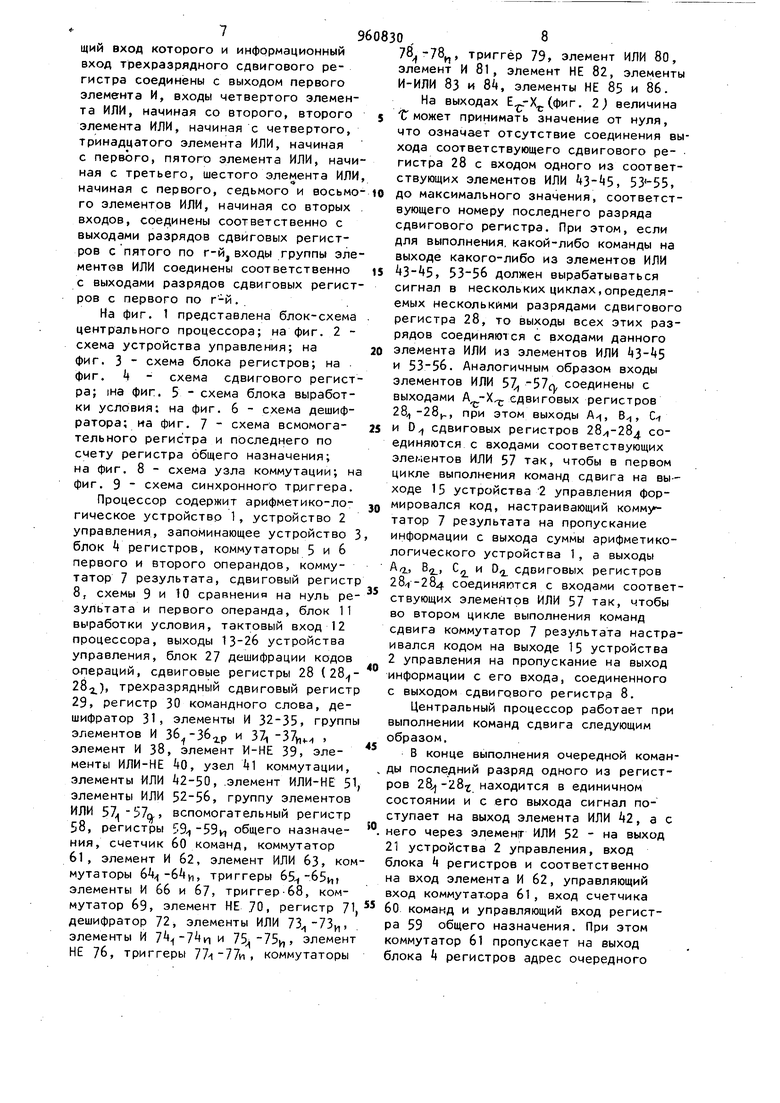

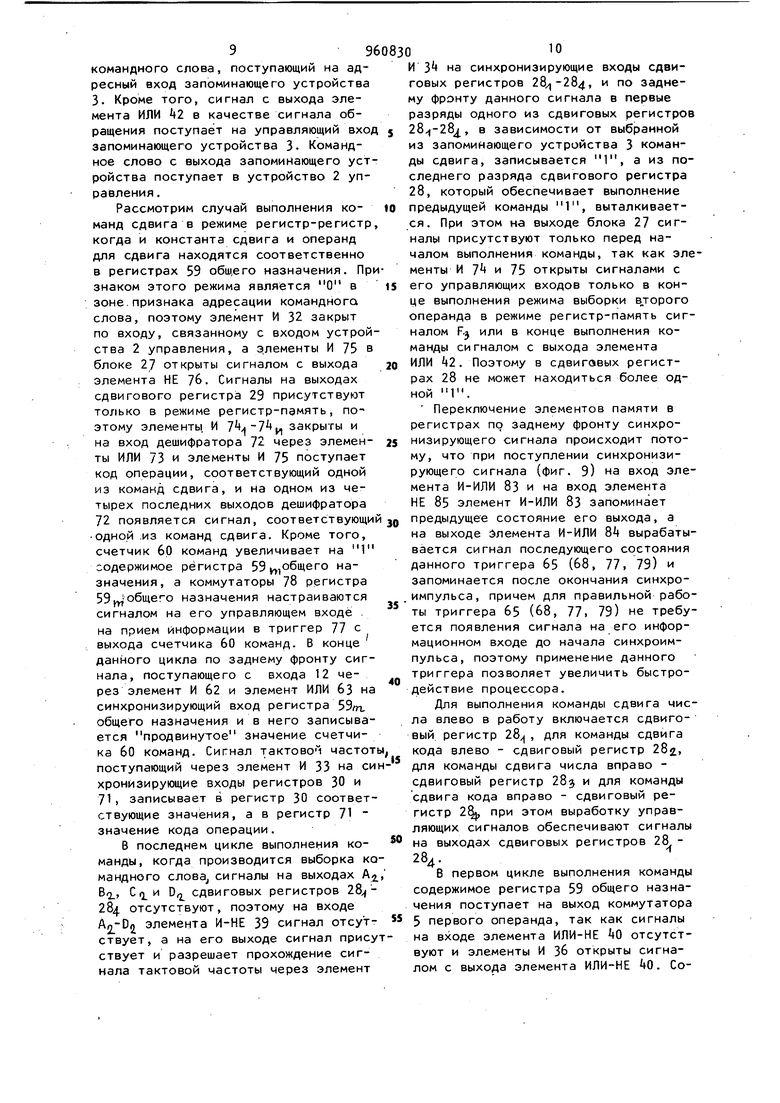

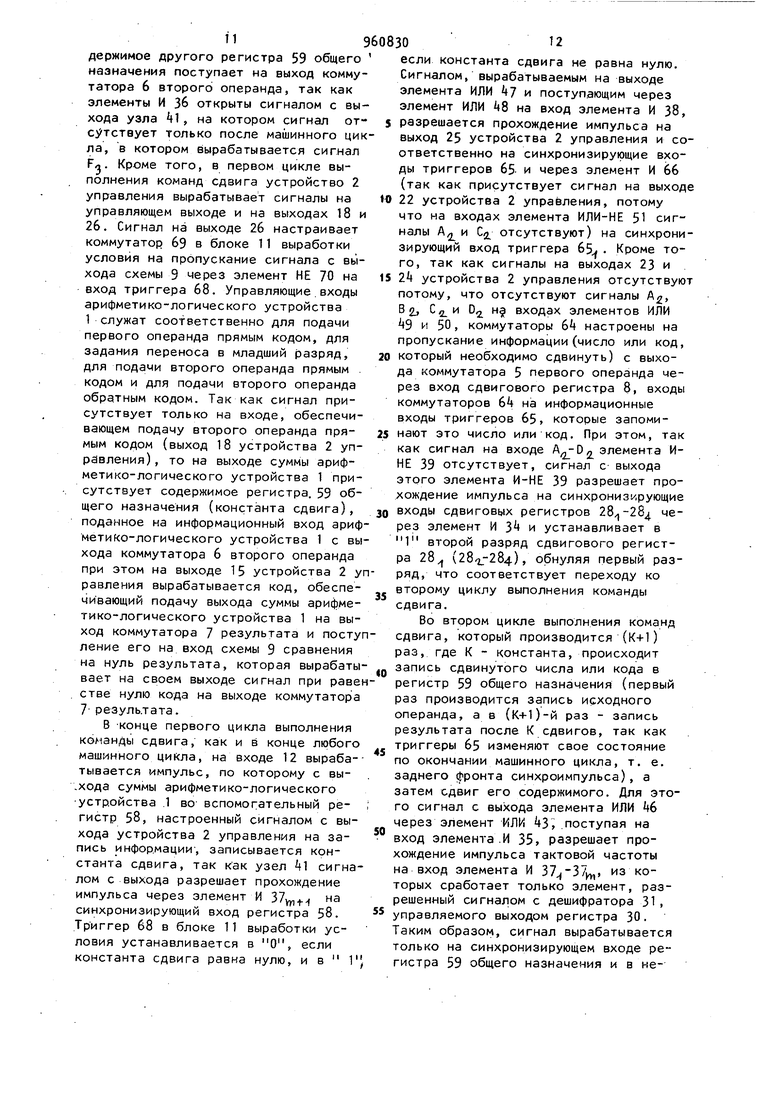

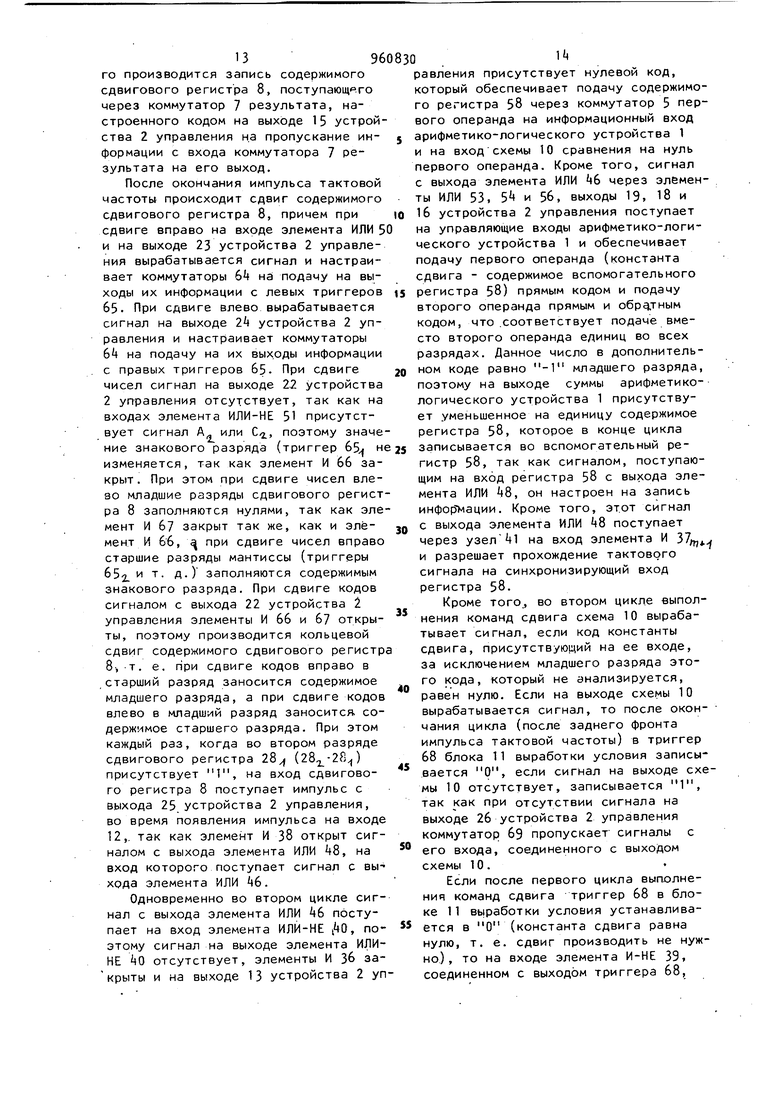

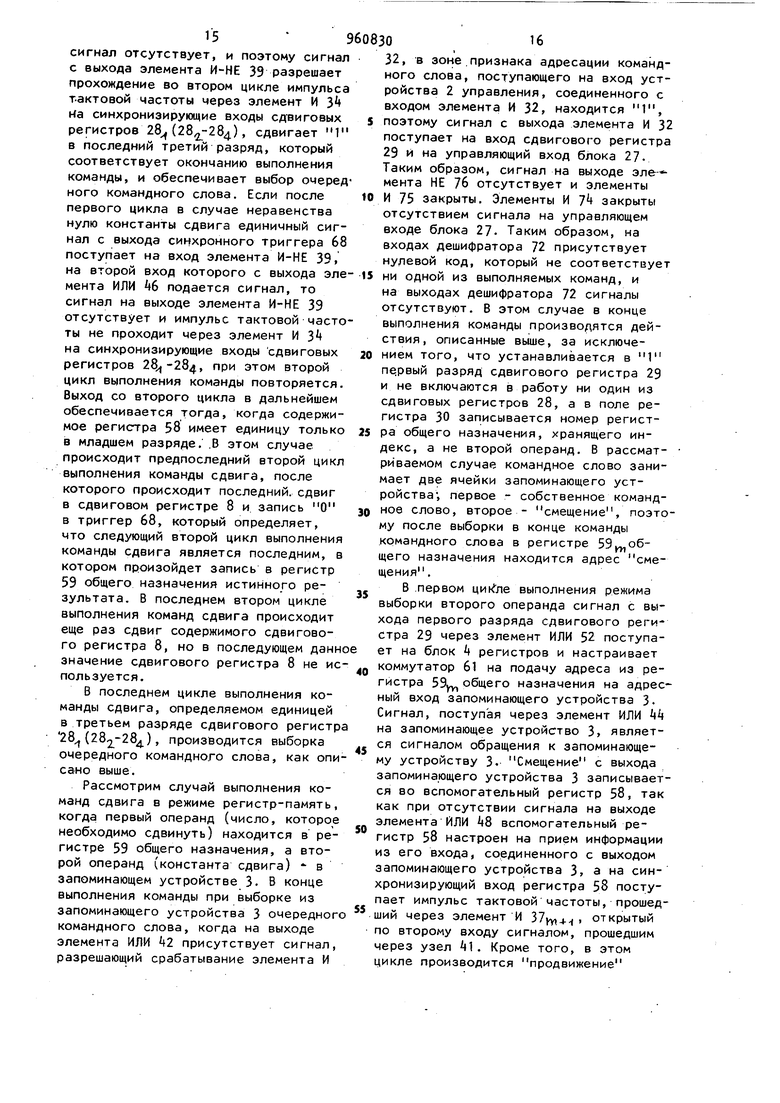

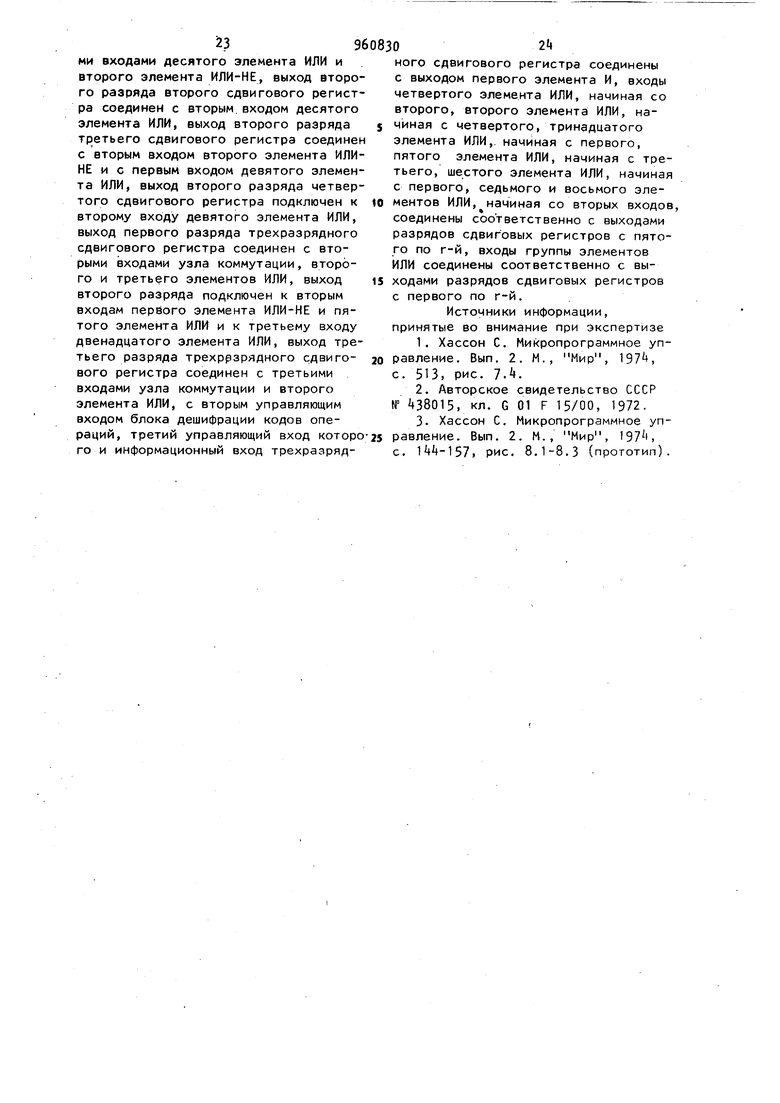

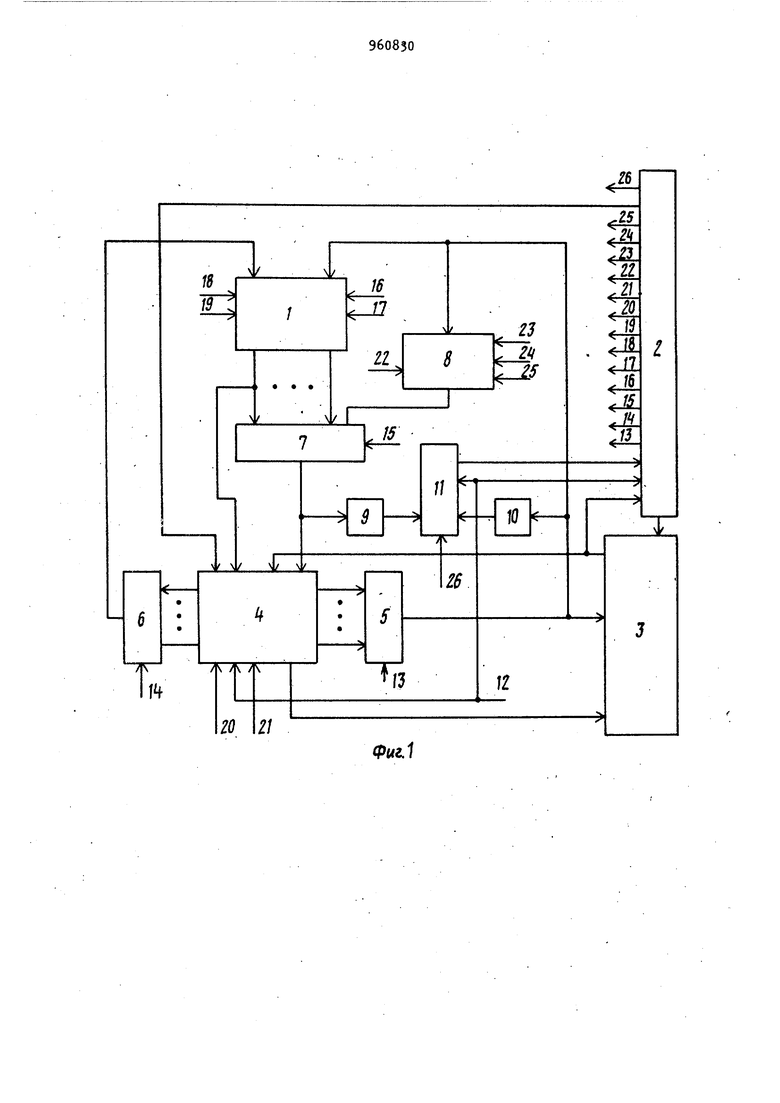

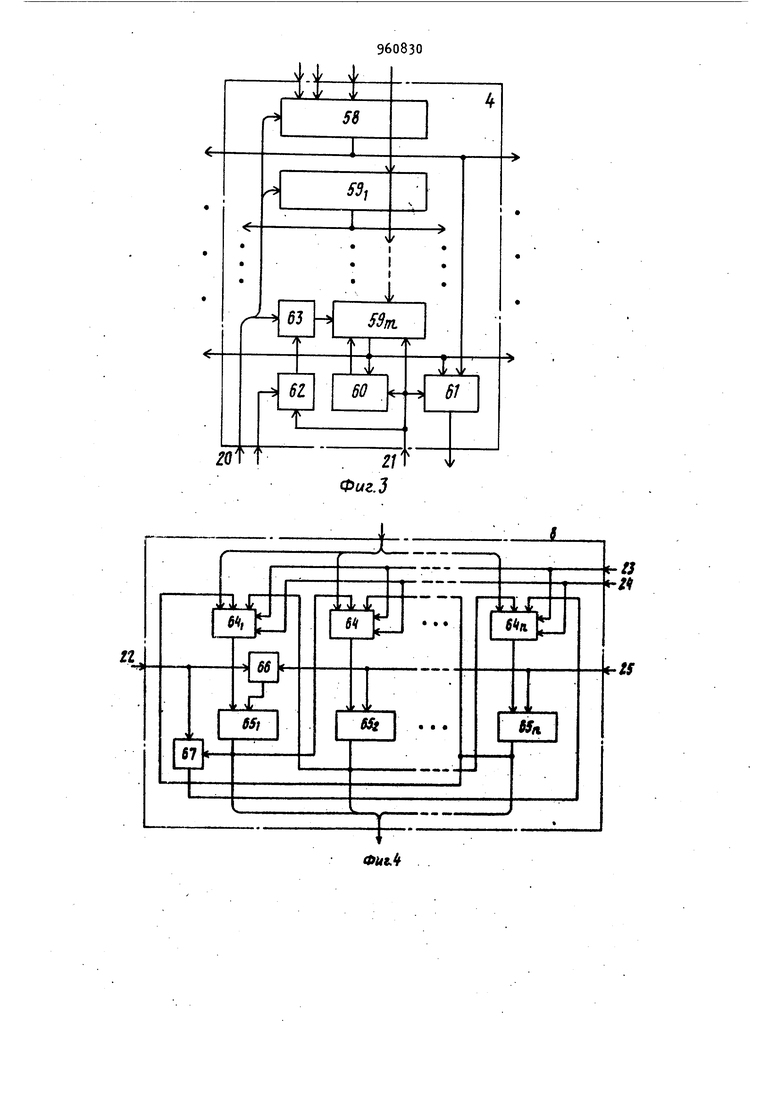

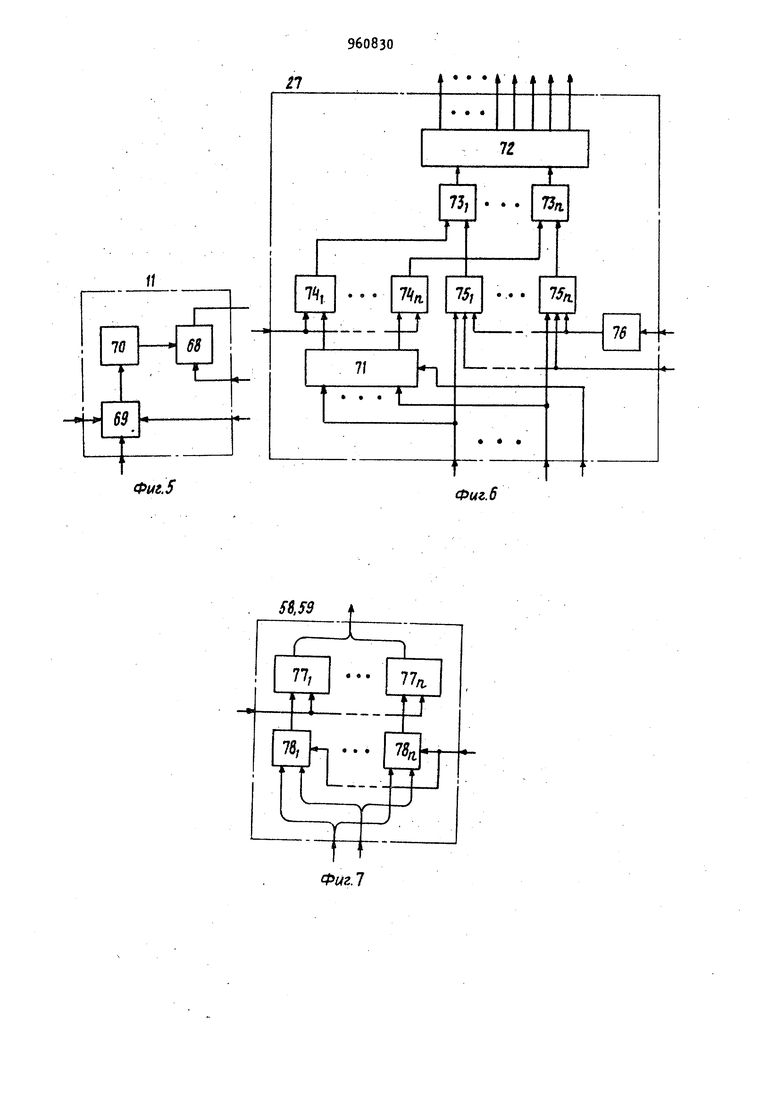

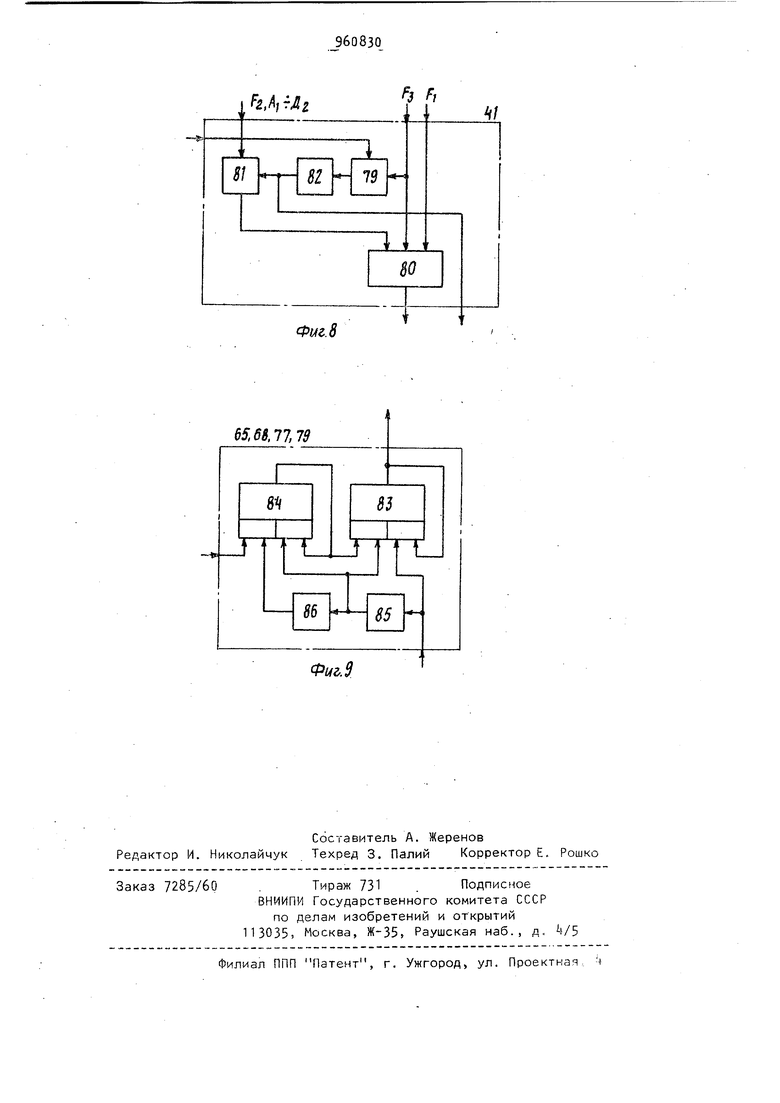

Наиболее близким по технической сущности к изобретению является процессор, содержащий сумматор (арифметико-логический блок), регистры (бло регистров), триггеры временного хранения, счетчики, схему однобайтовых логических операций, схему сдвига сумматора, запоминающее устройство ((основную память), группы входных и выходных вентилей требуемой разряд ности, связанные с соответствующими линиями (коммутаторы), схему анализа путем результата и устройство управления ГЗ}Недостатком известного процессора является то, что выполнение команд сдвига ПРОИЗВОДИТСЯ на схеме сдвига сумматора, при этом сдвиг операнда, а затем уменьшение константы сдвига в сумматоре на величину сдвига произ водится последовательно, что снижает быстродействие процессора при выполнении команд сдвига и соответственно снижает эффективное быстродействие вычислительной машины в целом.. Целью изобретения является повышение быQTpoдeйcтвия. Поставленная цель достигается тем что в центральный процессор, содержа щий арифметико-логическое устройство устройство управления, запоминающее устройство, блок регистров, коммутато ры первого и второго операндов, комму татор результата, схему сравнения на нуль результата, вход которой и вход результата блока регистров соединены с выходом коммутатора результата, ин формационный вход устройства управления и первый информационный вход блока регистров соединены с выходом запоминающего устройства, управляющий, информационный и адресный входы которого соединены соответственно с первым выходом устройства управления с выходом коммутатора первого операн да и с первым выходом блока регистров, первая группа выходов которого соединена соответственно с группой входов коммутатора первого операнда, выход которого соединен с первым информационным входом арифметико-логического устройства, информационный выход которого .соединен с первым вхо дом коммутатора результата, второй информационный вход арифметико-логического устройства соединен с выхо дом коммутатора второго операнда, группа входов которого соединена с . второй группой выходов блока регистров, тактовый вх.пд процессора соединен с тактовыми входами блока регист ров И устройства управления, выходы которого со второго по десятый соединены соответственно с управляющими входами коммутатора первого операнда, коммутатора второго операнда, коммутатора результата, с первым, вторым, третьим и четвертым управляющими входами арифметико-логического устройства, с первым и вторым управляющими входами блока регистров, введены сдвиговый регистр, схема сравнения на нуль первого операнда и блок выработки условия, выход которого соединен с управляющим входом устройства управления, выходы которого с одиннадцатого по четырнадцатый соединены соответственно с входом признака, с входом сдвига вправо, с входом сдвига влево и с входом строба сдвигового регистра, пятнадцатый выход устройства управле.ния подключен к управляющему входу блока выработки условия, первый и второй входы которого соединены соответственно с выходами схемы сравнения на нуль результате и схемы сравнения на нуль первого операнда, вход которой соединен с выходом коммутатора первого операнда и с информационным входом сдвигового регистра, выход которого соединен с вторым входом коммутатора .результата, третий вход которого и второй информационный вход блока регистров соединены с выходом суммы арифметико-логического устройства,, третий управляющий вход блока регистров соединен с шестнадцатым выходом устройства управления, тактовый вход блока выработки условия соединен с тактовым входом процессора. Блок выработки условия в процессоре содержит триггер, элемент НЕ и коммутатор, управляющий вход которого является управляющим входом блока, первый и второй входы коммутатора являются соответственно первым и вторым входами блока, выход коммутатора через элемент НЕ соединен с информационным входом триггера,синхронизирующий вход которого соединен с тактовым входом блока, выход триггера является выходом блока. Устройство управления содержит блок дешифрации кодов операций, регистр командного слова, сдвиговые регистры, дешифратор, элементы И, группы элементов И, элементы И-ЧЕ, ИЛИ, ИЛИ-НЕ, узел коммутации, группу элементов ИЛИ и трехразрядный сдвиговый регистр, причем информационный вход устройства соединен с информационными, входам блока дешифрации кодов операций, регистра командного слова и с первым входом первого элемента И, тактовый вход устройства соединен с первыми входами второго, третьего, четвертого, пятого и шестого элементов И, с синхронизирующими входами узла комму тации и трехразрядного сдвигового регистра, синхронизирующие входы сдв говых регистров с первого по четвертый подключены к выходу третьего эле мента И, синхронизирующие входы сдви говых регистров с пятого по г-й подключены к тактовому входу устройства управляющий вход которого соединен с первым входом элемента И-НЕ, выход которого подключен к второму входу третьего элемента И, выходы блока де шифрации кодов операций соединены со ответственно с информационными входа ми сдвиговых регистров, выходы после них разрядов которых соединены соответственно с входами первого элемента ИЛИ, выход которого соединен с первым управляющим входом блока дешифрации кодов операций, с вторыми входами первого и второго элементов И и с первыми входами второго и третьего элементов ИЛИ, выход второго элемента И соединен-со стробирующим входом блока дешифрации кодов операций и с синхронизирующим входом реги стра командного слова, выходы первой группы которого соединены соответственно с первыми входами элементов И первой группы, выходы второй группы подключены соответственно к первым входам элементов И второй группы и к входам дешифратора, выходы элементов И первой группы являются третьим выходом устройства, выходы элементов И второй группы являются вторым ВЬ1ХОДО устройства, вторые входы элементов И второй группы подключены к выходу первого элемента ИЛИ-НЕ, выходы деши ратора соединены соответственно с первыми входами элементов И третьей группы, вторые входы которых подключены к выходу четвертого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, второ вход шестого элемента И соединен с первым выходом узла коммутации, второй выход которого соединен с вторыми входами элементов И первой группы выходы элементов И третьей группы и выход шестого элемента И соединены с девятым выходом устройства, выходы группы элементов ИЛИ соединены с четвертым выходом устройства, выходы элементов ИЛИ с пятого по восьмой являются соответственно пятым, шестым, седьмым и восьмым выходами устройства, выходы с девнто|-о по четырнадцатый которого подключены соответственно к выходам третьего элемента ИЛИ, второго элемента ИЛИ-НЕ, девятого элемента ИЛИ, десятого элемента ИЛИ и пятого элемента И, выход одиннадцатого элемента ИЛИ соединен с пятнадцатым выходом устройства и с первым входом двенадцатого элемента ИЛИ, выход которого соединен с шестнадцатым выходом устройства, с вторым входом пятого элемента И, с первыми входами седьмого элемента ИЛИ и узла коммутации, выходы второго и тринадцатого элементов ИЛИ соединены с первым выходом устройства, входы одиннадцатого элемента ИЛИ соединены соответственно с выходами первых разрядов первого, второго, третьего и четвертого сдвиговых регистров, выходы вторых разрядов которых соединены соответственно с входами четырнадцатого элемеьГ та ИЛИ, выход которого соединен с вторым входом элемента И-НЕ, с первыми входами первого элемента ИЛИ-НЕ, четвертого; пятого и восьмого элементов ИЛИ и с вторым входом двенадцатого элемента ИЛИ, выход второго разряда первого сдвигового регистра соединен с первыми входами десятого элемента ИЛИ и второго элемента ИЛИ-НЕ, выход второго разряда второго сдвигового регистра соединен с вторым входом десятого элемента ИЛИ, выход второго разряда третьего сдвигового регистра соединен с вторым входом второго элемента ИЛИ-НЕ и с первым входом девятого элемента ИЛИ, выход второго разряда четвертого сдвигового регистра подключен к второму входу девятого элемента ИЛИ, выход первого разряда трёхразрядного сдвигового регистра соединен с вторыми входами узла коммутации, второго и третьего элементов ИЛИ, выход второго разряда подключен к вторым входам первого элемента ИЛИ-НЕ и пятого элемента ИЛИ и к третьему входу двенадцатого элемента ИЛИ, выход третьего разряда . трезрадрядного сдвигового регистра соединен с третьими входами узла коммутации и второго элемента ИЛИ, с вторым управляющим входом блока дешифрации кодов операций, третий управляющии вход которого и информационный вход трехразрядного сдвигового регистра соединены с выходом первого элемента И, входы четвертого элемента ИЛИ, начиная со второго, второго элемента ИЛИ, начиная с четвертого, тринадцатого элемента ИЛИ, начиная с первого, пятого элемента ИЛИ, начиная с третьего, шестого элемента ИЛИ, начиная с первого, седьмого и восьмого элементов ИЛИ, начиная со вторых . входов, соединены соответственно с выходами разрядов сдвиговых регистров с пятого по г-й входы группы элементов ИЛИ соединены соответственно с выходами разрядов сдвиговых регистров с первого по г-й, На фиг. 1 представлена блок-схема центрального процессора; на фиг. 2 схема устройства управления; на фиг. 3 схема блока регистров; на фиг. 4 - схема сдвигового регистра; |на фиг. 5 - схема блока выработки условия; на фиг. 6 - схема дешифратора; на фиг. 7 схема всмомогательного регибтра и последнего по счету регистра общего назначения; на фиг. 8 - схема узла коммутации; на фиг. 9 схема синхронного триггера. Процессор содержит арифметико-логическое устройство 1, устройство 2 управления, запоминающее устройство 3 блок регистров, коммутаторы 5 и 6 первого и второго операндов, коммутатор 7 результата, сдвиговый регистр 8, схемы 9 и 10 сравнения на нуль результата и первого операнда, блок 11 выработки условия, тактовый вход 12 процессора, выходы устройства управления, блок 27 дешифрации кодов операций, сдвиговью регистры 28 (), трехразрядный сдвиговый регистр 29, регистр 30 командного слова, дешифратор 31, элементы И 32-35, группы элементов И и 37., 37у, , элемент И 38, элемент И-НЕ 39, элементы ИЛИ-НЕ 0, узел 1 коммутации, элементы ИЛИ 42-50, .элемент ИЛИ-НЕ 51 элементы ИЛИ 52-56, группу элементов ИЛИ .) вспомогательный регистр 58, регистры i;9., 59ц общего назначения, счетчик 60 команд, коммутатор 61, элемент И 62, элемент ИЛИ 63, ком мутаторы , триггеры 65 -б5и1 элементы И 66 и 67, триггер-68, коммутатор б9, элемент НЕ 70, регистр 71 дешифратор 72, элементы ИЛИ элементы И и элемент НЕ 76, триггеры 77 77и , коммутаторы 96 0 , триггер 79, элемент ИЛИ 80, элемент И 81, элемент НЕ 82, элементы И-ИЛИ 83 и 84, элементы НЕ 85 и 86. На выходах (фиг. 2) величина Т может принимать значение от нуля, что означает отсутствие соединения выхода соответствующего сдвигового регистра 28 с входом одного из соответствующих элементов ИЛИ 43-45, 53-55, до максимального значения, соответствующего номеру последнего разряда сдвигового регистра. При этом, если для выполнения, какой-либо команды на выходе какого-либо из элементов ИЛИ 43-45, 53-56 должен вырабатываться сигнал в нескольких циклах,определяемых несколькими разрядами сдвигового регистра 28, то выходы всех этих разрядов соединяются с входами данного элемента ИЛИ из элементов ИЛИ 43-45 и 53-56. Аналогичным образом входы элементов ИЛИ 5Z, 57а соединены с выходами А -Х сдвиговых регистров ,, при этом выходы A-i, В, С и 0 сдвиговых регистров 28 1-284 соединяются с входами соответствующих элементов ИЛИ 57 так, чтобы в первом цикле выполнения команд сдвига на вы- ходе 15 устройства 2 управления формировался код, настраивающий комму татор 7 результата на пропускание информации с выхода суммы арифметикологического устройства 1, а выходы AI В2, С и 0 сдвиговых регистров 28/1-284 соединяются с входами соответствующих элементов ИЛИ 57 так, чтобы во втором цикле выполнения команд сдвига коммутатор 7 результата настраивался кодом на выходе 15 устройства 2 управления на пропускание на выход информации с его входа, соединенного с выходом сдвигового регистра 8. Центральный процессор работает при выполнении команд сдвига следующим образом. В конце выполнения очередной команды последний разряд одного из регистров 28 -28 находится в единичном состоянии и с его выхода сигнал поступает на выход элемента ИЛИ 42, а с него через элемент ИЛИ 52 - на выход 21 устройства 2 управления, вход блока 4 регистров и соответственно на вход элемента И б2, управляющий вход коммутат-ора 61 , вход счетчика 60 команд и управляющий вход регистра 59 общего назначения. При этом коммутатор б1 пропускает на выход блока 4 регистров адрес очередного

командного слова, поступающий на адресный вход запоминающего устройства 3. Кроме того, сигнал с выхода элемента ИЛИ 2 в качестве сигнала обращения поступает на управляющий вход запоминающего устройства 3. Командное слово с выхода запоминающего устройства поступает в устройство 2 управления.

Рассмотрим случай выполнения команд сдвига в режиме регистр-регистр когда и константа сдвига и операнд для сдвига находятся соответственно в регистрах 59 общего назначения. Признаком этого режима является О в зоне.признака адресации командного слова, поэтому элемент И 32 закрыт по входу, связанному с входом устройства 2 управления, а э.лементы И 75 в блоке 27 открыты сигналом с выхода элемента НЕ 7б. Сигналы на выходах сдвигового регистра 29 присутствуют только в режиме регистр-память, поэтому элементы. И закрыты и на вход дешифратора 72 через элементы ИЛИ 73 и элементы И 75 поступает код операции, соответствующий одной из команд сдвига, и На одном из четырех последних выходов дешифратора 72 появляется сигнал, соответствующи ОДНОЙ .из команд сдвига. Кроме того, счетчик 60 команд увеличивает на 1 содержимое регистра 59,,общего назначения, а коммутаторы 78 регистра 59 общего назначения настраиваются сигналом на его управляющем входе . на прием информации в триггер 77 с выхода счетчика 60 команд. В конце данного цикла по заднему фронту сигнала, поступающего с входа 12 через элемент И 62 и элемент ИЛИ 63 на синхронизирующий вход регистра 59fn. общего назначения и в него записывается продвинутое значение счетчика 60 команд. Сигнал тактовой частот поступающий через элемент И 33 на си хронизирующие входы регистров 30 и 71, записывает в регистр 30 соответствующие значения, а в регистр 71 значение кода операции. В последнем цикле выполнения команды, когда производится выборка ко мандного слова сигналы на выходах А/ BQ., D сдвиговых регистров отсутствуют, поэтому на входе элемента И-НЕ 39 сигнал отсут ствует, а на его выходе сигнал прису ствует и разрешает прохождение сигнала тактовой частоты через элемент

И 3 на синхронизирующие входы сдвиговых регистров , и по заднему фронту данного сигнала в первые разряды одного из сдвиговых регистров , в зависимости от выбранной из запоминающего устройства 3 команды сдвига, записывается 1, а из последнего разряда сдвигового регистра 28, который обеспечивает выполнение предыдущей команды 1, выталкивается. При этом на выходе блока 27 сигналы присутствуют только перед началом выполнения команды, так как элементы И 7 и 75 открыты сигналами с его управляющих входов только в конце выполнения режима выборки sjoporo операнда в режиме регистр-память сигналом F.J или в конце выполнения команды сигналом с выхода элемента ИЛИ k2. Поэтому в сдвиговых регистрах 28 не может находиться более одной 1.

Переключение элементов памяти в регистрах по заднему фронту синхронизирующего сигнала происходит потому, что при поступлении синхронизирующего сигнала (фиг. 9) на вход элемента И-ИЛИ 83 и на вход элемента НЕ 85 элемент И-ИЛИ 83 запоминает предыдущее состояние его выхода, а на выходе Элемента И-ИЛИ 8 вырабатывается сигнал последующего состояния данного триггера 65 (68, 77, 79) и запоминается после окончания синхроимпульса, причем для правильной работы триггера б5 (68, 77, 79) не требуется появления сигнала на его информационном входе до начала синхроимпульса, поэтому применение данного триггера позволяет увеличить быстродействие процессора. Для выполнения команды сдвига числа влево в работу включается сдвиговый, регистр 28, для команды сдвига кода влево - сдвиговый регистр 28 для команды сдвига числа вправо сдвиговый регистр 28з и для команды сдвига кода вправо - сдвиговый регистр 2 при этом выработку управляющих сигналов обеспечивают сигналы на выходах сдвиговых регистров первом цикле выполнения команды содержимое регистра 59 общего назначения поступает на выход коммутатора 5 первого операнда, так как сигналы на входе элемента ИЛИ-НЕ 0 отсутствуют и элементы И Зб открыты сигналом с выхода элемента ИЛИ-НЕ tO. Содержимое другого регистра 59 общего назначения поступает на выход коммутатора 6 второго операнда, так как элементы И 36 открыты сигналом с выхода узла 41, на котором сигнал отсутствует только после машинного цик ла, в котором вырабатывается сигнал Frt. Кроме того, в первом цикле выполнения команд сдвига устройство 2 управления вырабатывает сигналы на управляющем выходе и на выходах 18 и 26. Сигнал на выходе 2б настраивает коммутатор б9 в блоке 11 выработки условия на пропускание сигнала с выхода схемы 9 через элемент НЕ 70 на вход триггера 68. Управляющие.входы арифметико-логического устройства 1 служат соответственно для подачи первого операнда прямым кодом, для задания переноса в младший разряд, для подачи второго операнда прямым . кодом и для подачи второго операнда обратным кодом. Так как сигнал присутствует только на входе, обеспечивающем подачу второго операнда прямым кодом (выход 18 устройства 2 управления) , то на выходе суммы арифметико-логического устройства 1 присутствует содержимое регистра. 59 общего назначения (константа сдвига), поданное на информационный вход ариф метико-логического устройства 1 с вы хода коммутатора 6 второго операнда при этом на выходе 15 устройства 2 у равления вырабатывается код, обеспечивающий подачу выхода суммы арифметико-логического устройства 1 на выход коммутатора 7 результата и посту ление его на вход схемы 9 сравнения на нуль результата, которая вырабаты вает на своем выходе сигнал при раве стве нулю кода на выходе коммутатора 1 результата. В -конце первого цикла выполнения команды сдвига, как и в конце любого машинного цикла, на входе 12 вырабатывается импульс, по которому с вы-хода суммы арифметико-логического устройства .1 во вспомогательный регистр 58, настроенный сигналом с выхода устройства 2 управления на запись информации, записывается константа сдвига, так как узел 1 сигна лом с выхода разрешает прохождение импульса через элемент И 37 на синхронизирующий вход регистра 58. Триггер 68 в блоке 11 выработки условия устанавливается в О, если константа сдвига равна нулю, и в если константа сдвига не равна нулю. Сигналом, вырабатываемым на выходе элемента ИЛИ kj и поступающим через элемент ИЛИ 8 на вход элемента И 38, разрешается прохождение импульса на выход 25 устройства 2 управления и соответственно на синхронизирующие входы триггеров б5 и через элемент И 66 (так как присутствует сигнал на выходе 22 устройства 2 управления, потому что на входах элемента ИЛИ-НЕ 51 си1- налы АЛ и Cf отсутствуют) на синхронизирующий вход триггера 65. Кроме того, так как сигналы на выходах 23 и 2 устройства 2 управления отсутствуют потому, что отсутствуют сигналы Ag, В 21, С 2 и О,; 2. входах элементов 49 и 50, коммутаторы 64 настроены на пропускание информации (число или код, который необходимо сдвинуть) с выхода коммутатора 5 первого операнда через вход сдвигового регистра 8, входы коммутаторов 64 на информационные входы триггеров б5, которые запоминают это число или код. При этом, так как сигнал на входе 2 элемента ИНЕ 39 отсутствует, сигнал с выхода этого элемента И-НЕ 39 разрешает прохождение импульса на синхронизирующие входы сдвиговых регистров через элемент И 34 и устанавливает в 1 второй разряд сдвигового регистра 28 (), обнуляя первый разряд, что соответствует переходу ко второму циклу выполнения команды сдвига. Во втором цикле выполнения команд сдвига, который производится (К+1) раз, где К - константа, происходит запись сдвинутого числа или кода в регистр 59 общего назначения (первый раз производится запись исходного операнда, а в (К4-1)-й раз - запись результата после К сдвигов, так как триггеры б5 изменяют свое состояние по окончании машинного цикла, т. е. заднего iJipOHTa синхроимпульса), а затем сдвиг его содержимого. Для этого сигнал с выхода элемента ИЛИ 46 через элемент ИЛИ 43, .поступая на вход элементами 35, разрешает прохождение импульса тактовой частоты на вход элемента И , из которых сработает только элемент, разрешенный сигналом с дешифратора 31, управляемого выходом регистра 30. Таким образом, сигнал вырабатывается только на синхронизирующем входе регистра 59 общего назначения и в него производится запись содержимого сдвигового регистра 8, поступающего через коммутатор 7 результата, настроенного кодом на выходе 15 устрой ства 2 управления на пропускание информации с входа коммутатора 7 результата на его выход. После окончания импульса тактовой частоты происходит сдвиг содержимого сдвигового регистра 8, причем при сдвиге вправо на входе элемента ИЛИ 5 и на выходе 23 устройства 2 управления вырабатывается сигнал и настраивает коммутаторы 6 на подачу на выходы их информации с левых триггеров б5. При сдвиге влево вырабатывается сигнал на выходе 2 устройства 2 управления и настраивает коммутаторы на подачу на их выходы информации с правых триггеров б5. При сдвиге чисел сигнал на выходе 22 устройства 2 управления отсутствует, так как на входах элемента ИЛИ-НЕ 51 присутствует сигнал А- или С,, поэтому значе ние знакового разряда (триггер б5, И 66 заизменяется, так как элемент крыт. При этом при сдвиге чисел влево младшие разряды сдвигового регист ра 8 заполняются нулями, так как эле мент И 67 закрыт так же, как и элемент И 66, при сдвиге чисел вправо старшие разряды мантиссы (триггеры 65. и т. д.) заполняются содержимым знакового разряда. При сдвиге кодов сигналом с выхода 22 устройства 2 управления элементы И 66 и 67 открыты, поэтому производится кольцевой сдвиг содержимого сдвигового регистр В-, -т. е. Нри сдвиге кодов вправо в .старший разряд заносится содержимое младшего разряда, а при сдвиге кодов влево в младший разряд заносится содержимое старшего разряда. При этом каждый раз, когда во втором разряде сдвигового регистра 28 (28.-28) присутствует 1, на вход сдвигового регистра 8 поступает импульс с выхода 25 устройства 2 управления, во время появления импульса на входе 12,. так как элемент И ЗВ открыт сигналом с выхода элемента ИЛИ , на вход которого поступает сигнал с выхода элемента ИЛИ . Одновременно во втором цикле сигнал с выхода элемента ИЛИ 46 поступает на вход элемента ИЛЙ-НЕ , поэтому сигнал на выходе элемента ИЛИНЕ 0 отсутствует, элементы И Зб закрыты и на выходе 13 устройства 2 уп 9 ц н 1 равления присутствует нулевой код, который обеспечивает подачу содержимого регистра 58 через коммутатор 5 первого операнда на информационный вход арифметико-логического устройства 1 и на входсхемы 10 сравнения на нуль первого операнда. Кроме того, сигнал с выхода элемента ИЛИ 46 через элементы ИЛИ 53, 5 и 56, выходы 19, 18 и 16 устройства 2 управления поступает на управляющие входы арифметико-логического устройства 1 и обеспечивает подачу первого операнда (константа сдвига - содержимое вспомогательного регистра 58) прямым кодом и подачу второго операнда прямым и обратным кодом, что .соответствует подаче вместо второго операнда единиц во всех разрядах. Данное число в дополнительном коде равно -1 младшего разряда, поэтому на выходе суммы арифметикологического устройства 1 присутствует уменьшенное на единицу содержимое регистра 58, которое в конце цикла записывается во вспомогательный регистр 58, так как сигналом, поступающим на вход регистра 58 с выхода элемента ИЛИ 48, он настроен на запись инфО(5мации. Кроме того, этот сигнал с выхода элемента ИЛИ 48 поступает через узел41 на вход элемента И 37, и разрешает прохождение тактового сигнала на синхронизирующий вход регистра 58. Кроме того,, во втором цикле выполнения команд сдвига схема 10 вырабатывает сигнал, если код константы сдвига, присутствую1дий на ее входе, за исключением младшего разряда этого кода, который не анализируется, равен нулю. Если на выходе схемы 10 вырабатывается сигнал, то после окон- чания цикла (после заднего фронта импульса тактовой частоты) в триггер 68 блока 11 выработки условия записывается О, если сигнал на выходе схемы 10 отсутствует, записывается 1, так как при отсутствии сигнала на выходе 2б устройства 2 управления коммутатор б9 пропускает сигналы с его входа, соединенного с выходом схемы 10. Если после первого цикла выполнения команд сдвига триггер 68 в блоке 11 вь1работки условия устанавливается в О (константа сдвига равна нулю, т. е. сдвиг производить не нужно), то на входе элемента И-НЕ 39, соединенном с выходом триггера 68, сигнал отсутствует, и поэтому сигнал с выхода элемента И-НЕ 39 разрешает прохождение во втором цикле импульса тактовой частоты через элемент И 3 Иа синхронизирующие входы сдвиговых регистров 28(2827284), сдвигает 1 в последний третий разряд, который соответствует окончанию выполнения команды, и обеспечивает выбор очеред ного командного слова. Если после первого цикла в случае неравенства нулю константы сдвига единичный сигнал с выхода синхронного триггера 68 поступает на вход элемента И-НЕ 39, на второй вход которого с выхода эле мента ИЛИ 46 подается сигнал, то сигнал на выходе элемента И-НЕ 39 отсутствует и импульс тактовой часто ты не проходит через элемент ИЗ на синхронизирующие входы сдвиговых регистров , при этом второй цикл выполнения команды повторяется. Выход со второго цикла в дальнейшем обеспечивается тогда, когда содержимое регистра 58 имеет единицу только в младшем разряде. .В этом случае происходит предпоследний второй цикл выполнения команды сдвига, после которого происходит последний, сдвиг в сдвиговом регистре 8 и запись О в триггер 68, который определяет, что следующий второй цикл выполнения команды сдвига является последним, в котором произойдет запись в регистр 59 общего назначения истинного результата. В последнем втором цикле выполнения команд сдвига происходит еще раз сдвиг содержимого сдвигового регистра 8, но в последующем данн значение сдвигового регистра 8 не ис пользуется. В последнем цикле выполнения команды сдвига, определяемом единицей в третьем разряде сдвигового регистр 28(282-284), производится выборка очередного командного слова, как опи сано выше. Рассмотрим случай выполнения команд сдвига в режиме регистр-память, когда первый операнд (число, которое необходимо сдвинуть) находится в регистре 59 общего назначения, а второй операнд (константа сдвига) - в запоминающем устройстве 3. В конце выполнения команды при выборке из запоминающего устройства 3 очередног командного слова, когда на выходе элемента ИЛИ k2 присутствует сигнал, разрешающий срабатывание элемента И 32, в зоне.признака адресации командного слова, поступающего на вход устройства 2 управления, соединенного с входом элемента И 32, находится 1, поэтому сигнал с выхода элемента И 32 поступает на вход сдвигового регистра 29 и на управляющий вход блока 27Таким образом, сигнал на выходе эле- мента НЕ 7б отсутствует и элементы И 75 закрыты. Элементы И закрыты отсутствием сигнала на управляющем входе блока 27. Таким образом, на входах дешифратора 72 присутствует нулевой код, который не соответствует ни одной из выполняемых команд, и на выходах дешифратора 72 сигналы отсутствуют. В этом случае в конце выполнения команды производятся действия, описанные выше, за исключением того, что устанавливается в первый разряд сдвигового регистра 29 и не включаются в работу ни один из сдвиговых регистров 28, а в поле регистра 30 записывается номер регистра общего назначения, хранящего индекс, а не второй операнд. В рассмат- риваемом случае командное слово занимает две ячейки запоминающего устройства, первое - собственное командное слово, второе - смещение, поэтому после выборки в конце команды командного слова в регистре 59 общего назначения находится адрес смещения. В .первом выполнения режима выборки второго операнда сигнал с выхода первого разряда сдвигового регистра 29 через элемент ИЛИ 52 поступает на блок регистров и настраивает коммутатор 61 на подачу адреса из регистра 59уу, общего назначения на адресный вход запоминающего устройства 3. Сигнал, поступая через элемент ИЛИ А4 на запоминающее устройство 3, является сигналом обращения к запоминающему устройству 3. Смещение с выхода запоминающего устройства 3 записывается во вспомогательный регистр 58, так как при отсутствии сигнала на выходе элемента ИЛИ 48 вспомогательный регистр 58 настроен на прием информации из его входа, соединенного с выходом запоминающего устройства 3, а на синхронизирующий вход регистра 58 поступает импульс тактовой частоты, прошедший через элемент И 37. , открытый по второму входу сигналом, прошедшим через узел 1, Кроме того, в этом цикле производится продвижение счетчика 60 команд, запись продвину того значения в регистр 59) общего назначения и сдвиг 1 из первого и во второй разряд сдвигового регистра 29. Во втором цикле выполнения режима выборки второго операнда сигнал с вы хода второго разряда сдвигового регистра 29 поступает на входы элемента ИЛИ-НЕ 40 и элемента ИЛИ 56 и через элемент ИЛИ 48 на входы элемента ИЛИ St и узла k. Сигнал на выходе элемента ИЛИ-НЕ 0 отсутствует, поэтому нулевой код с выходов элементов И настраивает коммутатор 5 первого операнда на подачу смещения из вспомогательного регистра 58 на информационный вход арифметико логического устройства 1. Так как на выходе узла tl сигнал отсутствует только в цикле, последующем за циклом, в котором вырабатывается сигнал Fg, то элементы И 36 р. открыт и на их выходах установлен код, обеспечивающий подачу индекса из регистра 59 общего назначения на второй информационный вход арифметико-логического устройства 1. Кроме того, сигналы с выходов 16 и 18 устройства 2 управления обеспечивают выработку на его выходе устройства 1 суммы исполнительного адреса второго операнд (сумма значений смещения и индекса который записывается во вспомогатель ный регистр 58 импульсом тактовой частоты., поступающим через элемент И 37nif-f( открытый сигналом с выхода узла 41, на синхронизирующий вход регистра 58. Далее 1 сдвигается со второго в третий разряд сдвигового регистра 29 вырабатывающего сигнал и определяюще го выполнение .третьего цикла режима выборки второго операнда. В третьем цикле режима выборки вт рого операнда сигнал на выходе 21 устройства 2 управления отсутствует, поэтому коммутатор 61 настроен на подачу исполнительного адреса с выхода регистра 58 на адресный вход запоминающего устройства 3. Через элемент ИЛИ 44 сигнал поступает на управляющий вход запоминающего устройства 3 в качестве сигнала обращения и на его выход и соответственно на информационный вход блока 4 регистров поступает код второго операнда, который записывается во вспом гательный регистр 58, настроенный отсутствием сигнала на его управляющем входе на прием информации с входа, соединенного с информационным входом блока регистров, тактовым импульсом, поступающим с выхода элемента И открытого сигналом, прошедшим через элемент ИЛИ 80 на выход узла . Одновременно разрешается подача запомненного на регистре 71 в блоке 27 кода операции очередной команды через элементы И Jk, элементы ИЛИ 73 наВХОД дешифратора 72, на одном из четырех последних выходов которого вырабатывается сигнал. и импульсом тактовой частоты, -прошедшим через элемент И 34 на синхронизирующие входы сдвиговых регистров 28 28, записывается в сдвиговый регистр 28 (). Элемент И 34 открыт, так как на входе элемента И-НЕ 39 сигнал отсутствует. После этого начинается выполнение собственнокоманды сдвига, как описано выше. Отличие состоит лишь в том, что второй операнд (константа сдвига) уже Находится в регистре 58, поэтому в первом цикле выполнения команды после режима выборки сигнал на синхронизирующем входе регистра 58 не вырабатывается, так как элемент И 37./| закрыт отсутствием сигнала на первом выходе узла 41. На первом и втором выходах узла 41 сигнал отсутствует, так как после окончания цикла, в котором вырабатывается сигf, В триггер 79 записывается нал а на выходе элемента НЕ 82 сигнал отсутствует, что определяет отсутствие сигнала на выходах узла 41, при этом отсутствие сигнала на втором выходе узла 41, закрывающего элементы И .р, необходимо для тех команд, а которых требуется подача второго операнда на второй информационный вход арифметико-логического устройства 1 в первом цикле их выполнения. Константа сдвига, указывающая на число сдвигов, не несет информаци9нной нагрузки и служит для задания определенных временных задержек, используемых в многопроцессорных комплексах для ввода процессоров в синхронизм. Команды отличные от команд сдвига, выполняются в соответствии с известными алгоритмами их исполнения. Например, при выполнении команды сложения в формате RR операнды хранятся в регистрах 59 общего назначения, а в формате RX - в регистре 59 общего назначения и на регистре 58. Если принять команде сложения в соответствие регистр 285- сигнал Е, с его выхода (при этом Е и Ej совпадают, так как команда сложения одноцикловая) подается на выходы элемен тов ИЛИ 5б и обеспечивающих подачу операндов в арифметико-логическое устройство 1 прямым кодом, на выходы соответствующих элементов ИЛИ 57, обеспечивающих пропуск результата с выхода суммы арифметико-логического устройства 1 через коммутатор 7 результата на вход регистра 59 общего назначения. Кроме того, сигнал Е с выхода регистра 28 подается через элемент ИЛИ З на вход элемента И 35 сигнал на выходе которого вырабатывается во время появления сигнала на входе 12 тактовой частоты и проходит через тот элемент И 37, который соответствует регистру 59 общего назначения, указываемого полем R1 регистра 30. Поэтому результат сложения двух операндов записывается на регист 59 общего назначения. Так как в этом случае регистр 28 является одноразрядным, сигнал Е , являющийся.в этом случае сигналом поступает на вход элемента ИЛИ 2 и соответствует последнему циклу выполнения команды сло жения, приведенной в качестве примера Таким образом, данный центральный процессор позволяет распараллелить во времени выполнение собственного , сдвига и уменьшение константы сдвига в арифметико-логическом устройстве при выполнении команд сдвига и производить данные действия при выполнении одного и того же машинного цикла. Формула изобретения 1. Центральный процессор, содержащий арифметико-логическое устройство устройство управления, запоминающее устройство, блок регистров, коммутаторы первого и второго операндов, коммутатор результата, схему сравнения на нуль результата, вход которой и вход результата блока регистров соединены с выходом коммутатора результата, информационный вход устройства управления и первый информационный вход блока регистров соединены с выходом запоминающего устройства, управляющий, информационный и адресный Э 020 входы которого соединены соответствен НО с первым выходом устройства управления, с выходом коммутатора первого операнда и с первым выходом блока регистров, первая группа выходов которого соединена соответственно с группой входов коммутатора, первого операнда, выход которого соединен с первым информационным входом арифметико-логического устройства, информационный выход которого соединен с первым входом коммутатора результата, второй информационный вход арифметико-логического устройства соединен с выходом коммутатора второго операнда, группа входов которого соединена с второй группой выходов блока регистров, тактовый вход процессора соединен с тактовыми входами блока регистров и устройства управления, выходы которого со второго по десятый соединены соответственно с управляющими входами коммутатора первого операнда, коммутатора второго операнда, коммутатора результата, с первым, вторым, третьим и четвертым управляющими входами арифметико-логического устройства, с первым и вторым управляющими входами блока регистров, отличающийся тем, что, с целью повышения быстродействия, Е него введены сдвиговый регистр, схема сравнения на нуль первого операнда и блок выработки условия, выход которого соединен с управляющим входом устройства управления, выходы которого с одиннадцатого по четырнадцатый соединены соответственно с входом признака, с входом сдвига вправо, с входом сдвига влево и с входом строба сдвигового регистра, пятнадцатый -выход устройства управления подключен к управляющему входу блока выработки условия, первый и второй входы которого соединены соответственно с выходами схемы сравнения на нуль результата и. схемы сравнения на нуль первого операнда, вход которой соединен с выходом коммутатора первого операнда и с информационным входом сдвигового регистра, выход которого соединен с вторым входом коммутатора результата, третий вход которого и второй информационный вход блока регистров соединены с выходом суммы арифметико-логического устройства, третий управляющий вход блока регистров соединен с щестнадцатым выходом устройства управления, тактовый вход блока выработки условия соединен с тактовым входом процессора.

ции кодов операций, с вторыми входами первого и второго элементов И и с первыми входами второго и третьего элементов ИЛИ, выход второго элемента И соединен со стробирующим входом блока дешифрации кодов операций и с синхронизирующим входом регистра командного слова, выходы первой группы

которого соединены соответственно с первыми входами элементов И первой группы, выходы второй группы подключены соответственно к первым входам

элементов И второй группы и к входам дешифратора, выходы элементов И первой группы являются третьим выходом устройства, выходы элементовИ второй группы являются вторым выходом устройства, вторые входы элементов И второй группы подключены к выходу .первого элемента ИЛИ-НЕ, выходы дешифратора соединены соответственно с первыми входами элементов И третьей

группы, вторые входы которых подключены к выходу четвертого элемента И, второй вход которого соединен с выходом четвертого элемента ИЛИ, второй вход шестого элемента И соединен

с входами четырнадцатого элемента ИЛИ, выход которого соединен с вторым входом элемента И-НЕ, с первыми входами первого элемента ИЛИ-НЕ, четвертого пятого и восьмого элементов ИЛИ и с вторым входом двенадцатого элемента ИЛИ, выход второго разряда первого сдвигового регистра соединен с первыс первым выходом узла коммутации. второй выход которого соединен с вторыми вхрдами элементов И первой группы, выходы элементов И третьей группы и выход шестого элемента И соединены с девятым выходом устройства, выходы группы элементов ИЛИ соединены с четвертым выходом устройства, выходы элементов ИЛИ с пятого по восьмой являются соответственно пятым, шестым, седьмым и восьмым выходами устройства, выходы с десятого по четырнадцатый которого подключены соответст:.снно к выходам третьего элемента ИЛИ, второго элемента ИЛИ-НЕ, девятого элемента ИЛИ, десятого элемента ИЛИ и пятого элемента И, выход одиннадцатого элемента ИЛИ соединен с пятнадцатым выходом устройства и с первым входом двенадцатого элемента ИЛИ, выход которого соединен с шестнадцатым выходом устройства, с вторым входом пятого элемента И, с первыми входами седьмого элемента ИЛИ и узла коммутации, выходы второго и тринадцатого элементов ИЛИ соединены с первым выходом устройства, входы одиннадцатого элемента ИЛИ соединены, соответственно с выходами п.ервых разрядов первого, второго, третьего и четвертого сдвиговых регистров, выходы вторых разрядов которых соединены соответственно ми входами десятого элемента ИЛИ и второго элемента ИЛИ-НЕ, выход второго разряда второго сдвигового регистра соединен с вторым входом десятого элемента ИЛИ, выход второго разряда третьего сдвигового регистра соединен с вторым входом второго элемента ИЛИНЕ и с первым входом девятого элемента ИЛИ, выход второго разряда четвертого сдвигового регистра подключен к второму входу девятого элемента ИЛИ, выход первого разряда трехразрядного сдвигового регистра соединен с вторыми входами узла коммутации, второго и третьего элементов ИЛИ, выход второго разряда подключен к вторым входам первого элемента ИЛИ-НЕ и пятого элемента ИЛИ и к третьему входу двенадцатого элемента ИЛИ, выход третьего разряда трехррзрядного сдвигового регистра соединен с третьими входами узла коммутации и второго элемента ИЛИ, с вторым управляющим входом блока дешифрации кодов операций, третий управляющий вход которо го и информационный вход трехразряд9602 ного сдвигового регистра соединены с выходом первого элемента И, входы четвертого элемента ИЛИ, начиная со второго, второго элемента ИЛИ, начиная с четвертого, тринадцатого элемента ИЛИ,, начиная с первого, пятого элемента ИЛИ, начиная с третьего, шестого элемента ИЛИ, начиная с первого, седьмого и восьмого элементов ИЛИ, начиная со вторых входов, соединены соответственно с выходами разрядов сдвиговых регистров с пятого по г-й, входы группы элементов ИЛИ соединены соответственно с выходами разрядов сдвиговых регистров с первого по г-й. Источники информации, принятые во внимание при экспертизе 1.Хассон С, Микропрограммное управление. Вып. 2. М., Мир, Э, с. 513, рис. 7.. 2.Авторское свидетельство СССР №438015, кл. G 01 F 15/00, 1972. 3.Хассон С. Микропрограммное управление. Вып. 2. М. , Мир, 197i, с. 1+4-157 рис. 8.1-8.3 (прототип). . 2 ff F) f Jtf f r J y w y y X 5r

Фиг.З

Фиг. 7

Фи&.д

Авторы

Даты

1982-09-23—Публикация

1979-10-16—Подача