входу второго элемента ИЛИ, второй вход которого соединен с входом элемента НЕ и выходок элемента задержки,, вход которого соеддинен с выходом третьего элемента И, второй вход которого поддключен к второму входу первого элемента И и выходу третьего элемента ИЛИ, входы которого соединены с первым и вторым выходами дешифратора команд, причем информационный вход первого, тактовый вход третЕ:его регистров сдвига и одир из входов деИ-и(Оратора комснл; являются входсчми блока, выходами которого Я1:ляются соо:гВетстВвнно выходы первого элемента И третьего мента ИЛИ,третий и четвертый выходы де 1Ифра Ора , выход второго элемег та ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Резервированное запоминающее устройство | 1981 |

|

SU982086A1 |

| Запоминающее устройство с обнаружением и исправлением ошибок | 1980 |

|

SU959167A1 |

| Резервированное запоминающее устройство | 1983 |

|

SU1164789A1 |

| Запоминающее устройство с самоконтролем | 1980 |

|

SU877614A1 |

| ЗАПОМИНАЮЩЕЕ УСТРОЙСТВО С ДИНАМИЧЕСКИМ РЕЗЕРВИРОВАНИЕМ | 1990 |

|

RU2028677C1 |

| Способ магнитной записи асинхронных потоков цифровой информации и устройство для его осуществления | 1990 |

|

SU1788520A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В БАЙТЕ ИНФОРМАЦИИ | 2021 |

|

RU2758065C1 |

| АРИФМЕТИЧЕСКОЕ УСТРОЙСТВО ДЛЯ ВЫПОЛНЕНИЯ ДИСКРЕТНОГО ПРЕОБРАЗОВАНИЯ ФУРЬЕ | 1991 |

|

RU2015550C1 |

| Резервированное запоминающее устройство | 1987 |

|

SU1513526A1 |

| ОТКАЗОУСТОЙЧИВЫЙ ПРОЦЕССОР С КОРРЕКЦИЕЙ ОШИБОК В ДВУХ БАЙТАХ ИНФОРМАЦИИ | 2021 |

|

RU2758410C1 |

1. РЕЗЕРВИРОВ/5НИОЕ ЗАПОМИНАЮЩЕЕ УСТРОПСТВО, содержащее регистр адреса, выходы которого подключены к адресным входам первого и второго основных и резервного блоков памяти , первый и второй сумматоры, первые входьт которых подключены к выходам основных блоков памяти ,первые и вторые группы элементов И ,выxoд J которых являются информационными выходами устройства, отличающееся тем, что, с целью повышения надежности устройства, в него введены третья, четвертая и пятая группы элементов И, третий и четвертый сумматоры, регистры числа, дешифратор ошибки и блок местного управления, один из выходов которого является управляющим выходом устройства, а другие выходы подключены к первым входам элементов И первой и второй групп, к управляющим входам блоков памяти и к установочным входам регистров числа, одни из входов блока местного управления являются управляющими входами устройства, а другой вход подключен к выходу дешифратора ошибки, вход которого подключен соответственно к первьтм входам элементов И третьей, четвертой и пятой групп и к выходу четвертого сумматора, входы которого подключены соответственно х вторым входам элементов И первой группы и прямому выходу первого регистра числа, к прямому выходу третьего регистра числа. к вторым входам элементов И второй группы и прямому выходу второго регистра числа, инверсные выходы регистров числа подключены к информационным входам соответствукхдих блоков памяти, первому входу третьего сумматора и вторым входсич1 первого и второго сумматоров, а счетные входы регистров числа соединены с выходами элементов И третьей, четвертой и пятой групп, вторые входы которых подключены к выходам соответствующих сумматоров, второй вход третьего сумматора подключен к выходу резервного блока памяти. 2. Устройство по п. 1, отличающееся тем, что, блок местного управления содержит регистры (Л Ьявига, элементы И, элементы ИЛИ, RS -триггер, элемент задержки, элемент НЕ и дешифратор команд, входы которого подключены соответственно к первым входам первого и второго элементов И, к одному из входов RS -триггера, выходу последнего разряда первого и информационному входу второго регистров сдвига, к выходу второго разряда второгорегистра сдвига, к тактовым входам первого, второго и информационному входу третьего регистров сдвига и выходу первого элемента ИЛИ, первый вход которого соединен с информационным входом первого регистра и другим входом RS-триг гера, а второй вход - с выходом второго разряда третьего регистра сдвига, выход первого разряда которого подключен к второму входу второго элемента и, а установочный и тактовый входы - соответственно к выходу элемента НЕ и установочным входам первого и второго регистров сдвига, к первому входу третьего и третьему входу второго элементов И соответственно, причем четвертый вхЬд второго элемента И подключен к инверсному выходу триггера, а выход - к первому

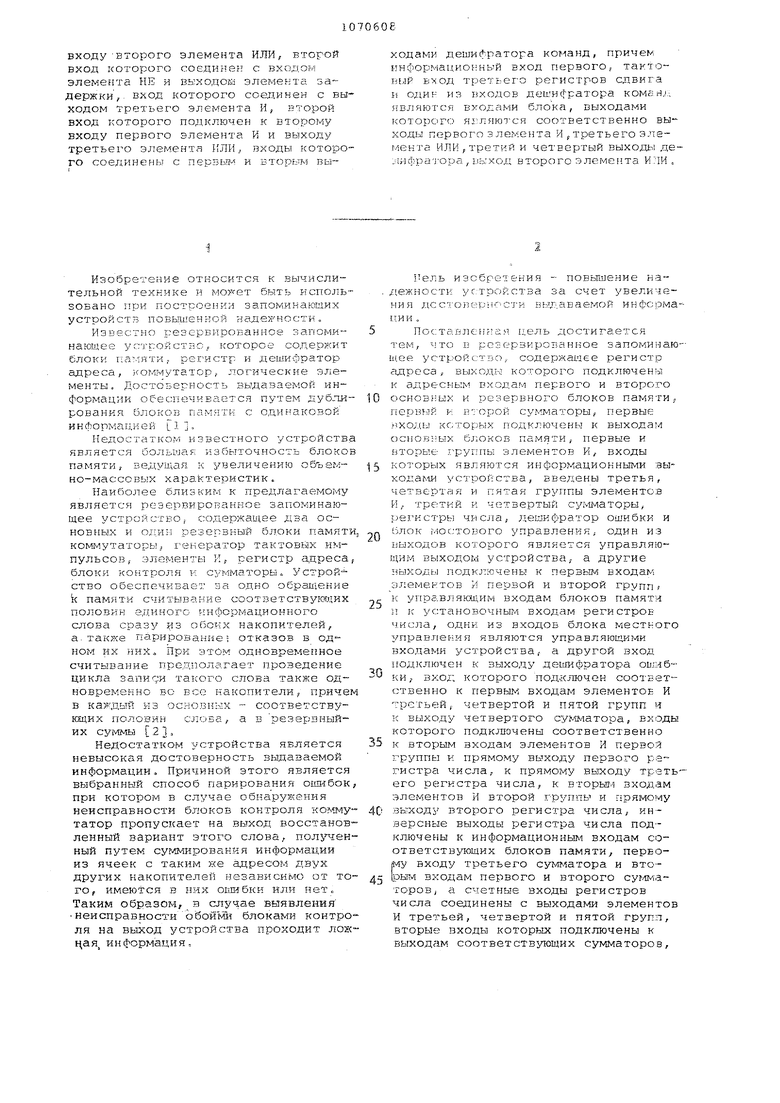

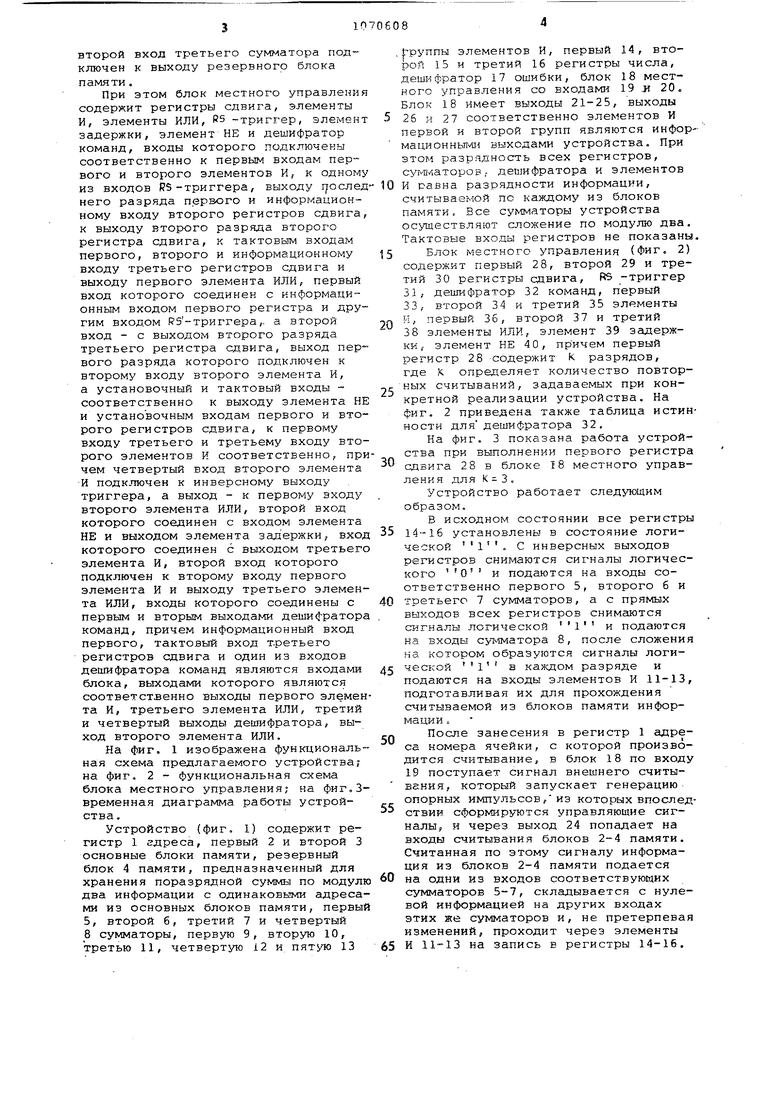

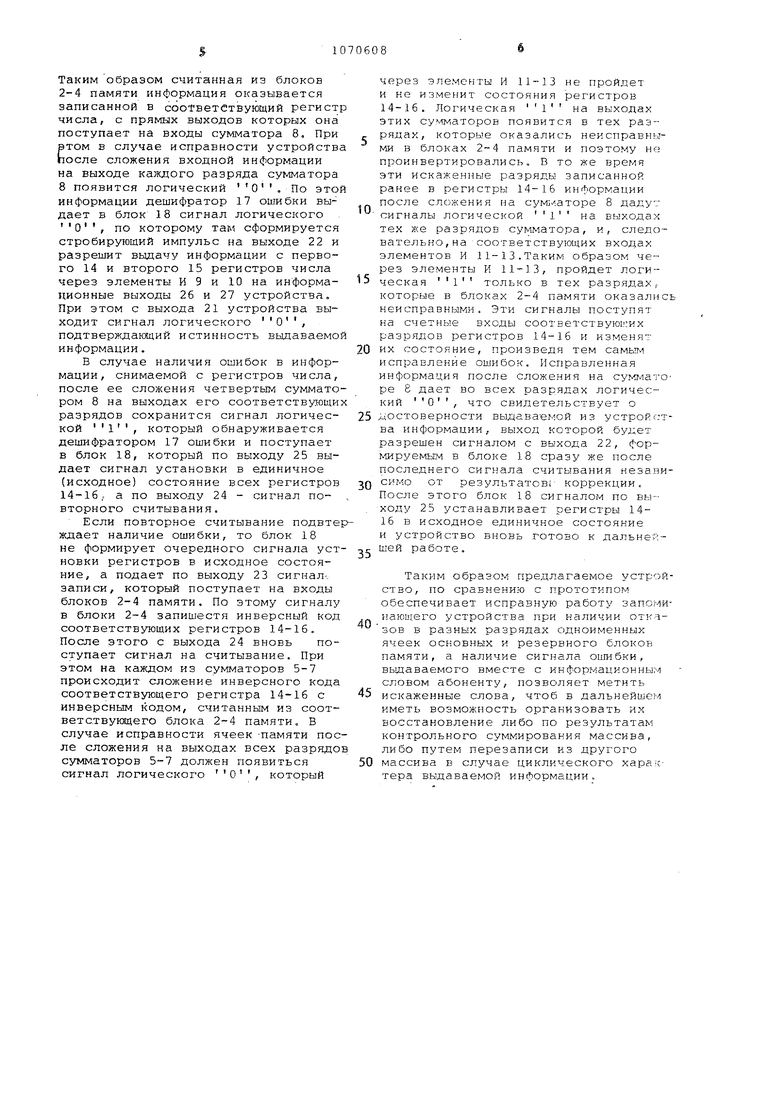

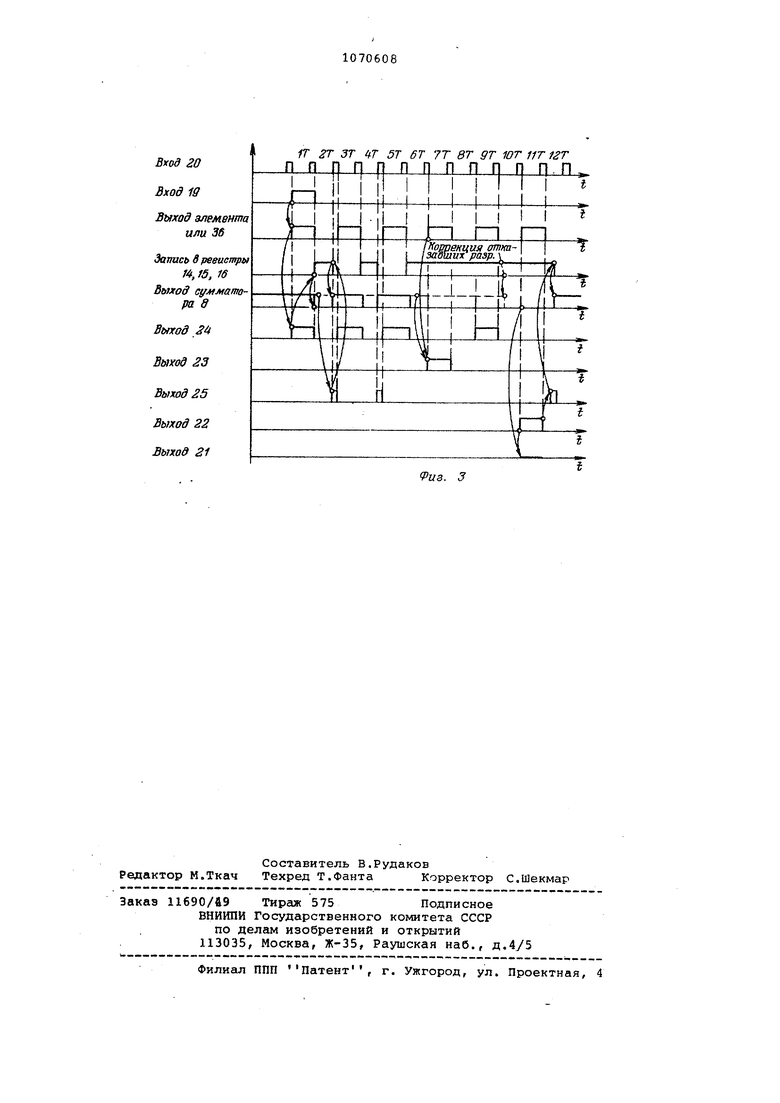

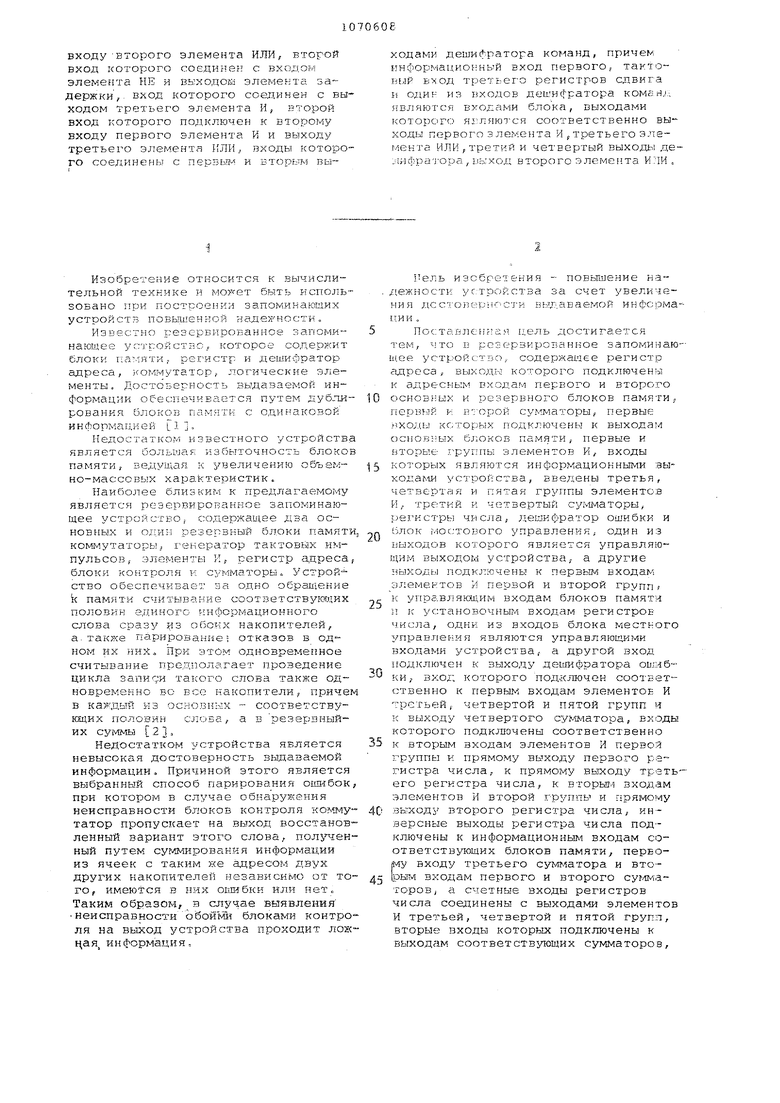

Изобретение ОТНОСРЕТОЯ к вычислительной технике и может бглть использовано при построении запоминающих устройств повышенной надежности. Известно резервированное запоми-нающее ycjpOKCTBO, которое содержит блоки гтамяти, регистр и дешифратор адреса, jcoMMyTaTOp, логические элементы. Достоверность выдаваемой информации обеспечивается путем дуб.пирования блогсов памяти с одинаковой информацией 11. Недостатком изве стного устройств является большая: } 3быточность блоко памяти, ведущая к увеличению объемно-массовых характеристик. Наиболее близким к предлагаемоучу является резервированное запоминающее устройство, содержащее два основных и ол.ин резервный блоки памят ком1иутаторы, генефатор тактовых импульсов, SHeMBHiH И, регистр адреса блоки контроля к сумматоры. Устройство обеспечивает за одно обраи-ение к памяти считывание соответствуюгдих половин единого информационного слова сразу ззз обоих накопителей, а-также парирование; отказов в их них При этом одновремеЕШое считывание предполагает проведение цикла записи татсого слова также одновременно во все накопители приче в каждый из основных - соответствующих половин слова, а в резервныйих суммы 2 Недостатком устройства является невысокая достоверность выдаваемой информации. Причиной этого является выбранный способ парирования при котором в случае обнаружения неисправности блоков контроля ко: В1у татор пропускает на выход, восстанов ленный вариант этого слова, ный путем су.1мированйя информации из ячеек с таким не а,цресом двух других накопителей независимо от то тоf имеются в них или нет Таким образом, а случае выявления неисправности обой№ блоками контро ля на выход устройства проходит лож ца я, и и Формаци я Иель изобретения - повышение надежности угтройства за счет увеличения дсстоверисС и выдаваемой информа Поставленгам. и.ель достигается тем, что D резервировсНное запоминающее устройство, содержащее регистр гцдреса ,- выходы которого подключены к адресным входам первого и второго основных и резервного блоков памяти, пепвнк и в-горой сумматоры, первые входы которых подключен к выходам основ;1ых блоков памяти, первые и вторые 1руппы элементов И, входы которых являются информационными выходами устройства, введены третья, четвертая- и пятая группы элементов И,, третий и четвертый сумматоры, регистры числа, дешифратор ошибки и (хпок мос:тового управления, один из выходов которого является управляющим выходом устройства, а другие выходы подключены к первьм входам элементов И первой и второй групп ,к управляющим входам блоков памяти п к установочнв1м входам регистров ч.исла, одни из входов блока местного управлер;ия являются управляющими входами устройства,- а другой вход подключен к выходу дешифратора ошибки, вход которого под-ключен соответственно к первым входам элементоЕ И третьей, четвертой и пятой групп и к выходу четвертого сумгдатора, входы которого подключены соответственно к вторым входам элементов И первой группы и прямому выходу первого ра гистрс числа, к прямому выходу третьего регистра числа, к вторыг входам элементов И второй группы и ггоямому выходу второго регистра числа, инверсные выходы регистра числа подключены к ин формацией входам соответствующих блоков памяти, перво1му входу третьего cy л лaтopa и входам первого и второго суг.паторов, а счетные входы регистров числа соединены с выходами элементов И третьей, четвертой и пятой групп, вторые входы которых подключены к выходам соответствующих сумматоров. второй вход третьего сумматора подключен к выходу резервного блока памяти. При этом блок местного управлени содержит регистры сдвига, элементы И, элементы ИЛИ, RS -триггер, элемен задержки, элемент НЕ и дешифратор команд, входы которого подключены соответственно к первым входам первого и второго элементов И, к одном из входов i S-триггера, выходу него разряда первого и информационному входу второго регистров сдвига к выходу второго разряда второго регистра сдвига, к тактовым входам первого, второго и информационному входу третьего регистров сдвига и выходу первого элемента ИЛИ, первый вход которого соединен с информационным входом первого регистра и дру гим входом RS-триггера,. а второй вход - с выходом второго разряда третьего регистра сдвига, выход пер вого разряда которого подключен к второму входу второго элемента И, а установочный и тактовый входы соответственно к выходу элемента Н и установочным входам первого и вто рого регистров сдвига, к первому входу третьего и третьему входу вто рого элементов И соответственно, пр чем четвертый вход второго элемента И подключен к инверсному выходу триггера, а выход - к первому входу второго элемента ИЛИ, второй вход которого соединен с входом элемента НЕ и выходом элемента задержки, вхо которого соединен с выходом третьег элемента И, второй вход которого подключен к второму входу первого элемента И и выходу третьего элемен та ИЛИ, входы которого соединены с первым и вторым выходами дешифратор команд, причем информационный вход первого, тактовый вход третьего регистров сдвига и один из входов дешифратора команд являются вxoдa ш блока, выходами которого являются соответственно выходы первого элемен та И, третьего элемента ИЛИ, третий и четвертый выходы дешифратора, выход второго элемента ИЛИ. На фиг. 1 изображена функциональная схема предлагаемого устройства; на фиг. 2 - функциональная схема блока местного управления; на фиг.Звременная диаграмма работы устройства. Устройство (фиг, 1) содержит регистр 1 гдреса, первый 2 и второй 3 основные блоки памяти, резервный блок 4 памяти, предназначенный для хранения поразрядной суммы по модулю два информации с одинаковыми адресами из основных блоков памяти, первый 5, второй 6, третий 7 и четвертый 8 сумматоры, первую 9, вторую 10, третью 11, четвертую 12 и пятую 13 группы элементов И, первый 14, второй 15 и третий 16 регистры числа, дешифратор 17 ошибки, блок 18 местного управления со входами 19 л 20. Блок 18 имеет выходы 21-25, выходы 26 и 27 соответственно элементов И первой и второй групп являются информационныт т выходами устройства. При этом разрядность всех регистров, сум шторов,- дешифратора и элементов И равна разрядности информации, считываемой по каждому из блоков памяти Все сумматоры устройства осушестБляют сложение по модулю два. Тактовые входы регистров не показаны. Блок местного управления (фиг. 2) содержит первый 28, второй 29 и третий 30 регистры сдвига, RS -триггер 31, дешифратор 32 команд, первый 33,- второй 34 и третий 35 элементы И, первый 36, второй 37 и третий 38 элементы ИЛИ, элемент 39 задержки, элемент НЕ 40, причем первый регистр 28 содержит К разрядов, где К. определяет количество повторных считываний, задаваемых при конкретной реализации устройства. На фиг. 2 приведена также таблица истинности для дешифратора 32, На фиг. 3 показана работа устройства при выполнении первого регистра сдвига 28 в блоке 18 местного управления для к - 3. Устройство работает следующим образом. В исходном состоянии все регистры 14--16 установлены в состояние логиС инверсных выходов ческой регистров снимаются сигналы логического О и подаются на входы соответственно первого 5, второго 6 и третьего 7 сумматоров, а с прямых выходов всех регистров снимаются сигналы логической j и подаются на входы су1 1матора 8, после сложения на котором образуются сигналы логической 1 в каждом разряде и подаются на входы элементов И 11-13, подготавливая их для прохождения считываемой из блоков памяти информацииПосле занесения в регистр 1 адреса номера ячейки, с которой производится считывание, в блок 18 по входу 19 поступает сигнал внешнего считывания, который запускает генерацию опорных импульсов ,из которых впоследствии сформируются управляющие сигналы, и через выход 24 попадает на входы считывания блоков 2-4 памяти. Считанная по этому сигналу информация из блоков 2-4 памяти подается на одни из входов соответствующих сумматоров 5-7, складывается с нулевой информацией на других входах этих же сумматоров и, не претерпевая изменений, проходит через элементы И 11-13 на запись в регистры 14-16.

Таким образом считанная из блоков 2-4 памяти информация оказывается записанной в соответСтвующий регистр числа, с прямых выходов которых она поступает на входы сумматора 8. При ВТОМ в случае исправности устройства после сложения входной информации на выходе каждого разряда сумматора 8 появится логический О, По этой информации дешифратор 17 ошибки выдает в блок 18 сигнал логического О, по которому там сформируется стробиругощий импульс на выходе 22 и разрешит выдачу информации с первого 14 и второго 15 регистров числа через элементы И 9 и 10 на информационные выходы 26 и 27 устройства. При этом с выхода 21 устройства выходит сигнал логического О, подтверждагаций истинность выдаваемой информации.

В случае наличия ошибок в информации, снимаемой с регистров числа, после ее сложения четвертым сумматором 8 на выходах его соответствующих разрядов сохранится сигнал логической , который обнаруживается дешифратором 17 ошибки и поступает в блок 18, который по выходу 25 выдает сигнал установки в единичное (исходное) состояние всех регистров 14-16, а по выходу 24 - сигнал повторного считывания.

Если повторное считывание подвтерждает наличие ошибки, то блок 18 не формирует очередного сигнала устновки регистров в исходное состояние, а подает по выходу 23 сигнал записи, который поступает на входы блоков 2-4 памяти. По этому сигналу в блоки 2-4 запишестя инверсный код соответствующих регистров 14-16. После этого с выхода 24 вновь поступает сигнал на. считывание. При этом на каждом из сумматоров 5-7 происходит сложение инверсного кода соответствующего регистра 14-16 с инверсным кодом, считанным из соответствующего блока 2-4 памяти. В случае исправности ячеек -памяти после сложения на выходах всех разрядо сумматоров должен появиться

О

который

сигнал логического

через элементы И 11-13 не пройдет и не изменит состояния регистров 14-16. Логическая на выходах этих су лматоров появится в тех разрядах, которые оказались неисправными в блоках 2-4 памяти и поэтому не проинвертировались. В то же время эти искаженные разряды записанной ранее в регистры 14-16 информации после сложения на .аторе В дадут сигналы логической М на выходах тех же разрядов сумматора, и, следователь(, на соответствующих входах элементов И 11-13.Таким образом через элементы И 11-13, пройдет логическая только в тех разрядах г которые в блоках 2-4 памяти оказали неисправными. Эти сигналы поступят на счетные входы соответствую1 ;их разрядов регистров 14-16 и изменят их состояние, произведя тем caMHTvi исправление ошибок. Исправленная информация после сложения на ре 8 дает во всех разрядах логичесО

что свидетельствует о

достоверности выдаваемой из устройс.-тва информации, выход которой будет разрешен сигналом с выхода 22, формируемым в блоке 18 сразу же после последнего сигнала считывания независимо от результатов коррекции. После этого блок 18 сигналом по выходу 25 устанавливает регистры 1416 в исходное единичное состояние и устройство вновь готово к дальнейшей работе.

Таким образом предлагаемое устройство, по сравнению с прстстипом обеспечивает исправную работу запоминающего устройства при наличии oTi-ca0

ов в разных разрядах одноименных ячеек основных и резервного блоков памяти, а наличие сигнала ошибки, вьщаваемого вместе с инф-ормационным словом абоненту, позволяет метить искаженные слова, чтоб в дальнейшем иметь возможность организовать их восстановление либо по результатам контрольного суммирования массива, либо путем перезаписи из другого массива в случае циклического характера выдаваемой информации.

от 18

omiB

j т up

26 I i

21 Z3

Раг. 1

Табтца истинности для дешифратора 32

лоз. о или 1

Риа. 2

IT 2Т ЭТ ЧТ 5Т 6Т 7Т 8Т 9Т ЮТ ;/Г 12Т

ол

«РИЗ. 3

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Запоминающее устройство с автономным контролем | 1978 |

|

SU780049A1 |

| Походная разборная печь для варки пищи и печения хлеба | 1920 |

|

SU11A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Автосское свидетельство СССР по заявке № 2942873/18-24, кл.й 11 С 29/00, 1980 (прототип). | |||

Авторы

Даты

1984-01-30—Публикация

1982-10-27—Подача