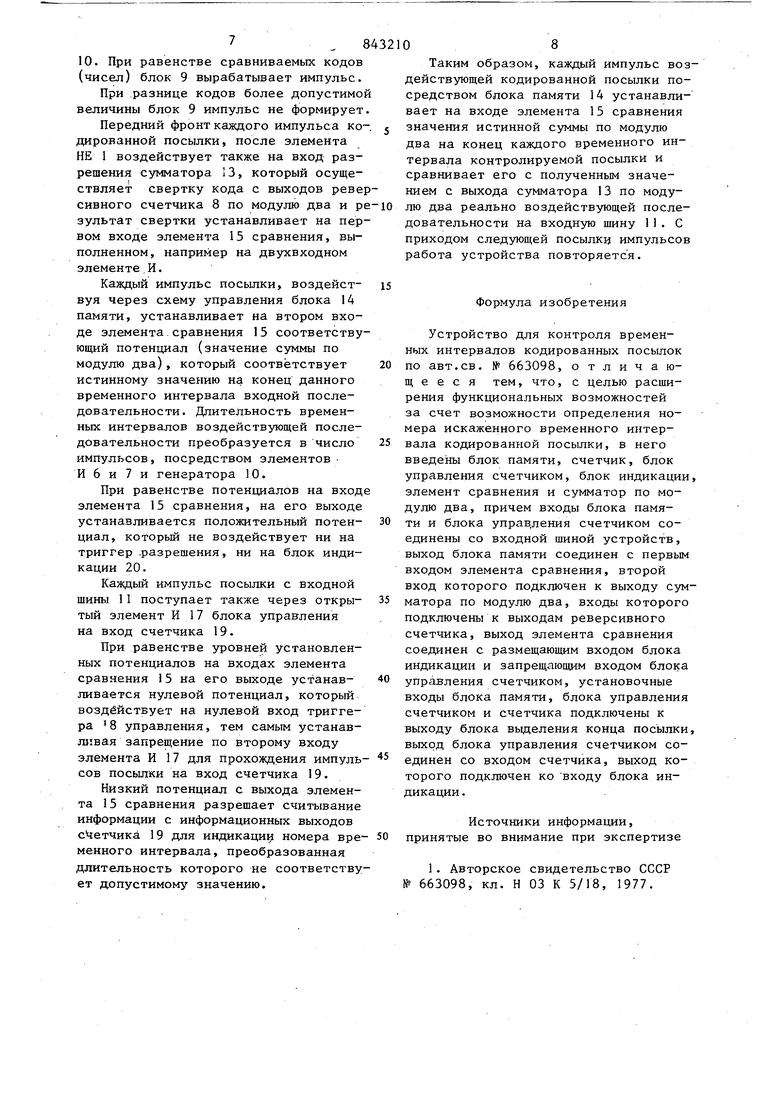

(54) УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ВРЕМЕННЬК ИНТЕРВАЛОВ КОДИРОВАННЫХ ПОСЬШОК 38 работоспособности и контроля трчности формирования интервалов каждым узлом формирователей временных интервалов кодирования посьшки. На это требуется длительный промежуток времани, что увеличивает время ремонта устройства. Цель изобретения - расширение функ циональных возможностей устройства эа счет возможности определения номера искгшенного временного интервала кодированной посылки. Поставленная цель достигается тем что в устройство для контроля временных интервалов кодирования посылок, содержащее реверсивный счетчик, блоки выделения начала и конца посылки, выходы каждого из которых соединены с соответствующими входами триггера, элементы И, -блок сравнения и счетный триггер, один выход которого подключен .к первому входу, триггера, а счетный вход счетного триггера через элемент IE соединен со входами блоков начала и конца посылки, другой вход счетного триггера соединен со. вторым входом элемента И, первый выход кото рого подключен к первым входам реверсивного счетчика и ко второму входу дополнительного элемента И, выход ко торого соединен со вторым входом реверсивного счетчика, третий вход которого подключен к выходу элемента И третийвход которого соединен с третьим входом дополнительного элемента И и с выходом генератора, выходы реверсивного счетчика через блок сравнения соединены со вторым выходом триггера, введены блок памяти, счетчик, . блок, управления счетчиком, блок индикации, элемент сравнения и сумматор по модулю два, причем входы блока памяти и блока управления счет чиком соединены со входной шиной уст .ройства, выход блока памяти соединен с первым входом элемента сравнения, второй вход которого подключен к выходу сумматора по модулю два, .входы которого подключены к выходам реверсивного счетчика, выход элемента сра нения соединен с разрешающим входом блoкia индикации и запрещающим входом блока управления счетчиком, установо ные входы блока памяти, блока управления счетчиком и счетчика подключены к выходу блока выделения конца посылки, выход блока управления счет чиком соединен со входом счетчика. 4 выход которого подключен ко входу блока индикации. На фиг.1 представлена блок-схема устройства; на фиг,2 - временные диаграммы работы устройства. Устройство для контроля временных интервалов кодированной посылки содержит элемент НЕ 1, блок 2 выделения начала посылки, блок 3 выделения конца посылки, счетньй триггер 4, триггер 5, элементы 6 и 7, реверсивный счетчик 8 импульсов, блок 9 сравнения (с узлом памяти), генератор 10 импульсовл входную шину I 1 и выходную шину. 12, сумматор 13 по модулю два, блок 14 памяти, элемент 15 сравнения, блок 16 управления счетчиком, содержащий элемент И 17 и триггер управления 18, счетчик 19 и блок 20 индикации. Входная шина 11 соединена со входом блоков выделения начала 2 и конца з посылки, входом блока 14 памяти ипервым входом элемента И 17, блок 16 управления, второй вход элемента И 17 соединены с единичным выходом триггера 18 управ.пения, а через элемент НЕ 1 со счетным входом триггера 4, Установочный вход блока 14 памяти соединен с выходом блока выделения конца, посылки, нулевым входом триггера 5 и установочными входами счетчика 19 и блока 16, Выход блока 2 выделения начала посылки соединен с единичньпм входом триггера 5 и установочным входом счетного триггера 4, Единичный выход счетного триггера 4 соединен с первым входом элемента И 6, а нулевой выход соединен с третьим входом элемента И 7, Единичный выход триггера 5 соединен с первым входом элемента И 7, вторым входом элемента И 6 и установочным входом реверсивного счетчика 8, Нулевой выход триггера 5 соединен с входом размещения блока 9 Сравнения, Третий вход элемента И 6 и второй вход элемента И 7 присоединены к выходу генератора 10. Выход элемента И 6 присоединен к входу суммирования, а выход элемента И 7 к входу вычитания реверсивного счетчика 8, информационные выходы которого присоединены к входам блока 9 сравнения и входам сумматора 13 по модулю два. Выход сумматора 13 присоединен к первому входу элемента 15 сравнения второй вход которого присоединен к выходу блока 14 памяти. Выход элемента 15 сравнения присоединен к нулевому входу триггера 18 блока 16 управления и входу разрешения блока 20 индикации. Выход элемента И 17 и блока 16 управления присоединен к счетному входу счетчика 19, информационные выходы которого присоединены к блоку 20 индикации. Выход блока 3 вьщеления конца посылки соединены с установочным входом.блока 14 памяти и счетчика 19 и единичным входом триггера 18 разрешения блока 16 упра лений и нулевь1М входом триггера 5. Устройство работает следующим образом. В исходное состояние устройство устанавливается импульсом с выхода блока 3 выделения конца посыпки, который устанавливает в исходное состоя-20 ние блок 14 памяти, выполненный, например, на регистре сдвига, который предназначен для хранения значения суммы по модулю два числа импульсов заполнения каждого неискаженного Временного интервала посылки, воздействующей в данный момент на входную шину 11, преобразованную в число импульсов. Импульс с выхода блока 3 устанавливает на выходе триггера 5 нулевой потенциал, который запрещает прохождение импульсов через элемен- ты И 7 и 6 и устанавливает в исходно положение реверсивный счетчик 8. Импульс с выхода блока 3 устанавливает в исходное состояние счетчик 19, а на выходе триггера разрешения 1-8 единичный потенциал, который является, разрешающим для элемента И 17. Состояние счетного триггера 4 во время отсутствия кодированной посылки не влияет на работу устройства, так как он устанавливается в необходимое состояние импульсом с выхода блока 2 в такое состояние, при котором на единичном выходе триггера 4 (фиг.2), т.е. на выходе элемента И 6 устанавливается запрещение, а на входе элемента И 7 - разрешение. Импульсы генератора 10 не проходят на вькод элементов И 7 и . 6, так как каждый имеет хотя бы по одному из входов на котором установлено запрещение от триггеров 4 и 5 (фиг.2). Первый импульс кодированной посылки положительной полярности через элемент НЕ 1 поступает на счетный вход триггера 4 и через открытый по

момента осуществляет сравнения числа (остатка) попеременного сложения, вычитания импульсов с .выхода генератора 06. обеим входам элемент И 17 схемы 16 управления на вход счетчика 19. В качестве счетного триггера 4, может быть использован D -триггер. Импульс с выхода блока 2 воздействует на вход триггера 5 с раздельными входами. Триггер 5 устанавливается передним.фронтом первого импульса в состояние 1, что является разрешением для прохождения импульсов через элементы 6 и 7 и,снимает запрещение с установочных входов реверсив.ного счетчика. 8. Триггер 4 устанавливается передним фронтом первого импульса с выхода блока 2 в такое состояние, при котором на его единичном выходе устанавливается нулевой потенциал, который запрещает по первому входу элемента И 6 прохождение импульсов заполнения на вход счетчика 8 до момента прихода заднего фронта первого импульса посылки с вы хода элемента НЕ 1 на счетный вход триггера 4. Импульсы с выхода генератора 10 через открытый элемент И 6 поступают на вход суммирования реверсивного счетчика 8. В момент поступления второго,импульса посылки на счетный вход триггера 4, на выходе которого устанавливается низкий потенциал, т.е. запрещение по соответствующему входу элемента 6, на другом выходе триггера 4 устанавливается высокий потенциал, т.е. разрешение по соответствующему вxoдv элемента 7, импульсы с выхода генератора.10 поступают на вход вычитания реверсивного счетчика. Таким образом, все импульсы определяющие нечетные временные интервалы кодированной посылки, разрешают прохождение импульсов с выхода генератора 10 на суммирующий вход, а четные разрешают прохождение на вычитающий вход реверсивного счетчика 8. Импульс с выхода блока 3 устанавивает триггер 5 в такое состояние, ри котором нулевой потенциал на его рямом выходе устанавливает запреще-. ие по входам элементов 6 и 7, едиичный потенциал на выходе устанавивает разрешение по дополнительному ходу блока 9, который после этого

7, 8

10. При равенстве сравниваемых кодов (чисел) блок 9 вырабатывает импульс.

При разнице кодов более допустимой величины блок 9 импульс не формирует

Передний фронт каждого импульса ко дированной посылки, после элемента НЕ 1 воздействует также на вход разрешения сумматора 13, который осуществляет свертку кода с выходов реверсивного счетчика 8 по модулю два и ре зультат свертки устанавливает на первом входе элемента 15 сравнения, выполненном, например на двухвходном элементе,И.

Каждый импульс посьшки, воздействуя через схему управления блока 14 памяти, устанавливает на втором входе элемента.сравнения 15 соответствующий потенциал (значение суммы по Модулю два), который соответствует истинному значению на конец данного временного интервала входной последовательности. Длительность временных интервалов воздействующей последовательности преобразуется в число импульсов, посредством элементов И 6 и 7 и генератора 10.

При равенстве потенциалов на вход элемента 15 сравнения, на его выходе устанавливается положительный потенциал, которьш не воздействует ни на триггер .разрешения, ни на блок индикации 20.

Каждый импульс посылки с входной шины 11 поступает также через открытый элемент И 17 блока управления на вход счетчика 19.

При равенстве уровней установленных потенциалов на входах элемента сравнения 15 на его выходе устанавливается нулевой потенциал, который воздействует на нулевой вход триггера 8 управления, тем самым устанавливая запрещение по второму входу элемента И 17 для прохождения импульсов посьшки на вход счетчика 19.

Низкий потенциал с выхода элемента 15 сравнения разрешает считывание информации с информационных выходов сметчика 19 для индикации номера временного интервала, преобразованная длительность которого не соответствует допустимому значению.

О8

Таким образом, каждый импульс воздействующей кодированной посылки посредством блока памяти 14 устанавливает на входе элемента 15 сравнения значения истинной суммы по модулю два на конец каждого временного интервала контролируемой посылки и сравнивает его с полученным значением с выхода сумматора 13 по модулю два реально воздействующей последовательности на входную шину 11. С приходом следующей посылки импульсов работа устройства повторяется.

Формула изобретения

Устройство для контроля временных интервалов кодированных посылок по авт.св. № 663098, отличающееся тем, что, с целью расширения функциональных возможностей за счет возможности определения номера искаженного временного интервала кодированной посылки, в него введены блок памяти, счетчик, блок управления счетчиком, блок индикации элемент сравнения и сумматор по модулю два, причем входы блока памяти и блока управления счетчиком соединены со входной шиной устройств, выход блока памяти соединен с первым входом элемента сравнения, второй вход которого подключен к выходу сумматора по модулю два, входы которого подключены к выходам реверсивного счетчика, выход элемента сравнения соединен с размещающим входом блока индикации и запрещающим входом блока управления счетчиком, установочные входы блока памяти, блока управления счетчиком и счетчика подключены к выходу блока выделения конца посылки выход блока управления счетчиком соединен со входом счетчика, выход которого подключен ко входу блока индикации .

Источники информации, принятые во внимание при экспертизе

1. Авторское свидетельство СССР № 663098, кл. Н 03 К 5/18, 1977.

0Ui,

Фиг.2.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля временных интервалов кодированных посылок | 1976 |

|

SU663095A1 |

| Устройство контроля временных интер-ВАлОВ КОдиРОВАННыХ пОСылОК | 1979 |

|

SU843211A2 |

| Устройство для контроля логических блоков | 1982 |

|

SU1105897A1 |

| Устройство для обучения операторов | 1991 |

|

SU1785026A1 |

| Устройство для контроля логических блоков | 1985 |

|

SU1269141A1 |

| Устройство для отображения однократных электрических сигналов | 1983 |

|

SU1141445A1 |

| Устройство для измерения периодов следования импульсов при контроле перемещения магнитного носителя | 1989 |

|

SU1647644A1 |

| Параллельный сигнатурный анализатор | 1984 |

|

SU1182523A1 |

| Устройство для сглаживания периодических случайных сигналов | 1981 |

|

SU982012A1 |

| Резервированный усилитель | 1987 |

|

SU1434568A1 |

Авторы

Даты

1981-06-30—Публикация

1979-05-03—Подача