1

Изобретение относится к импульсной технике, в частности к делителям частоты, и может быть использовано в автоматике, вычислительной технике и радиотехнике.

Известен делитель частоты с любым целочисленным коэффициентом деления, содержащий счетчик, триггер, дешифратор и схемы совпадения 1.

Однако это устройство относительно сложное и не обладает достаточными функциональными возможностями, так как длительность выходного сигнала равна 0,5 периода входной частоты, что недостаточно для синхронизации более низкочастотных схем.

Известно также устройство, содержащее двоичный счетчик, выходами соединенный со входами дешифратора, прямой и инверсный выходы которого соединены с входами дешифратора J К-триггера, и совпадения 2.

Однако функциональные возможности этого устройства также ограничены, так как выходной сигнал имеет длительность 0,5 периода входного сигнала, что недостаточно для синхронизации нескольких делителей частоты при требовании синфазной работы.

Цель изобретения - расширение функциональных возможностей.

Поставленная цель достигается тем, что в делитель частоты с любым целочисленным коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной щиной, а выходы разрядов, кроме первого и второго, подключены ко входам дешифратора, введены регистр сдвига и элементы И, первые входы которых и первый С-вход регистра сдвига объединены и подключены к входной шине, второй С-вход регистра сдвига подключен к выходу первого элемента И, второй вход которого соединен с выходом первого разряда счетчика импульсов,У-вход регистра сдвига соединен с выходом дешифратора, D-входы объединены и подключены к выходу второго разряда счетчика импульсов, а выход - ко второму входу второго элемента И, выход которого соединен с установочным входом счет,чика импульсов.

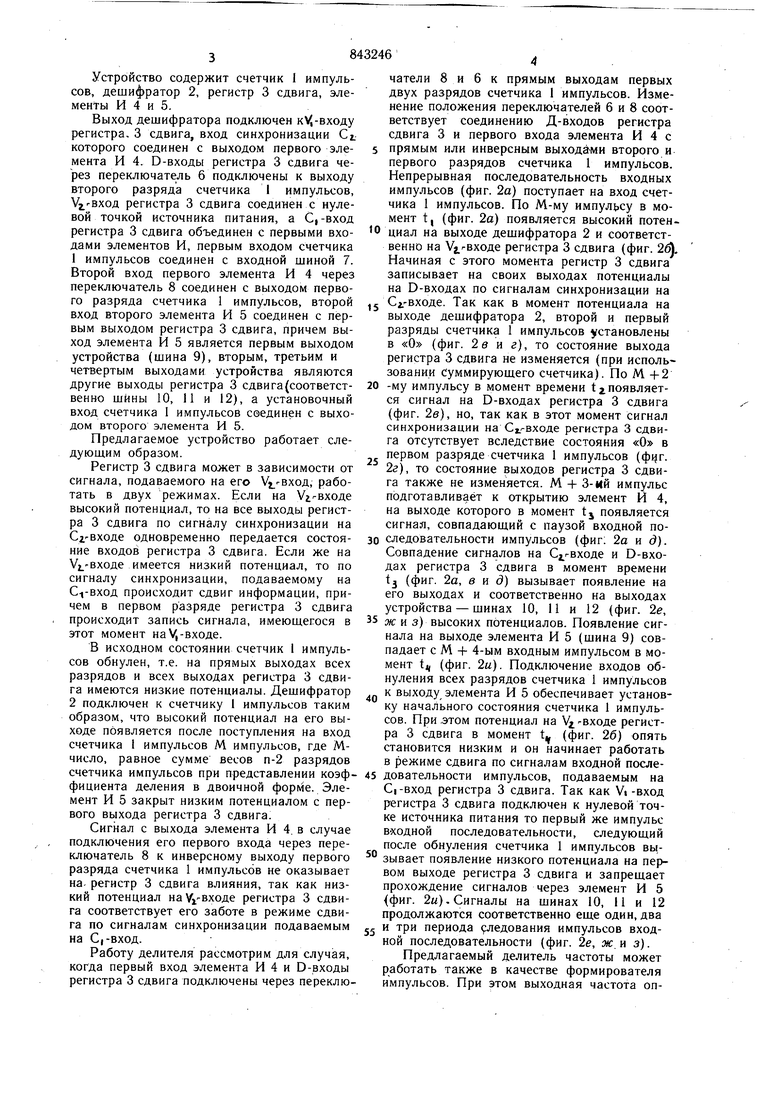

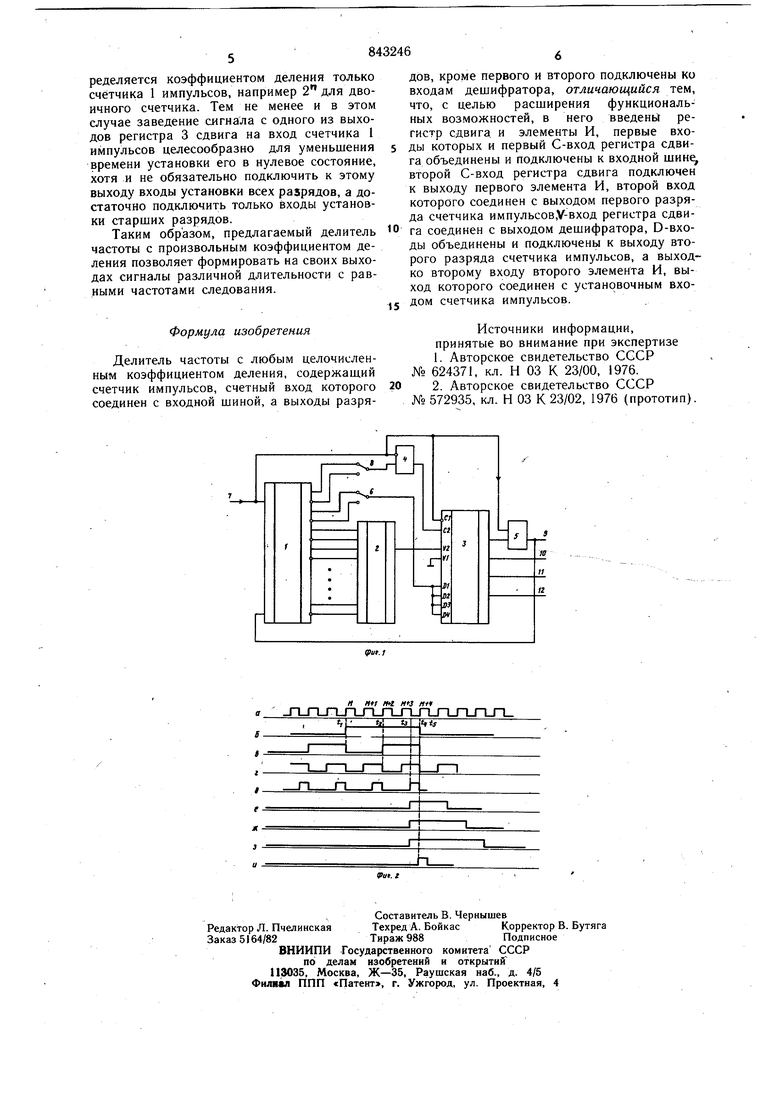

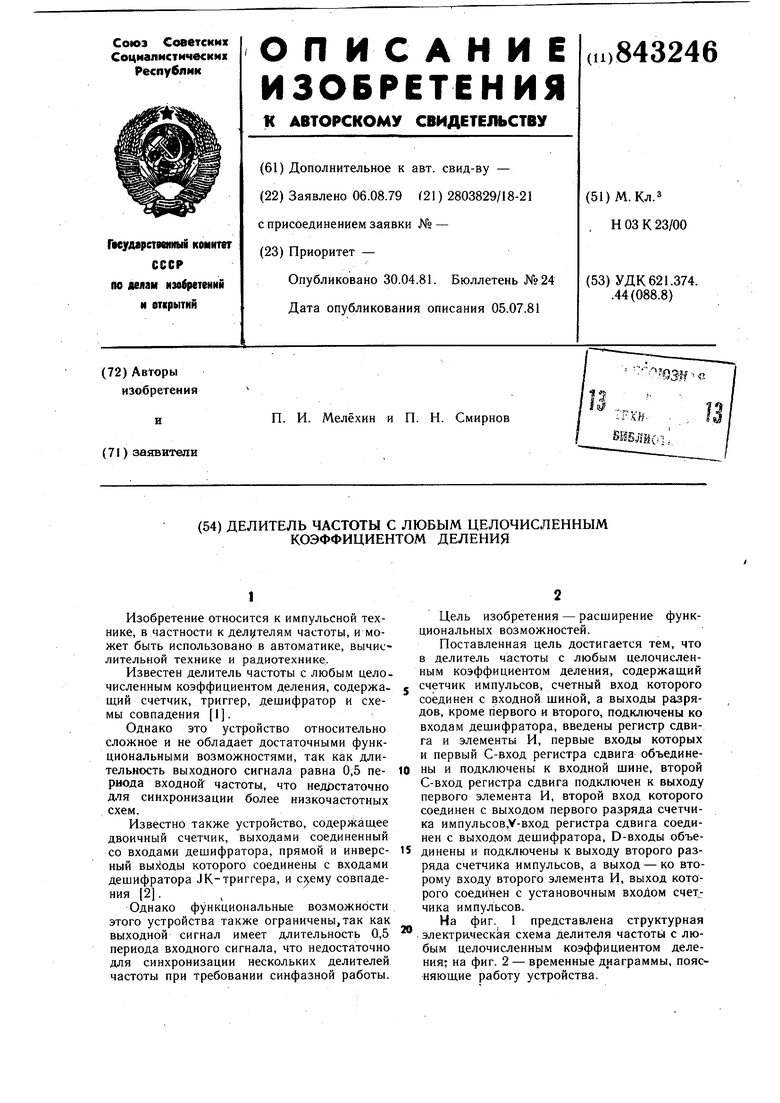

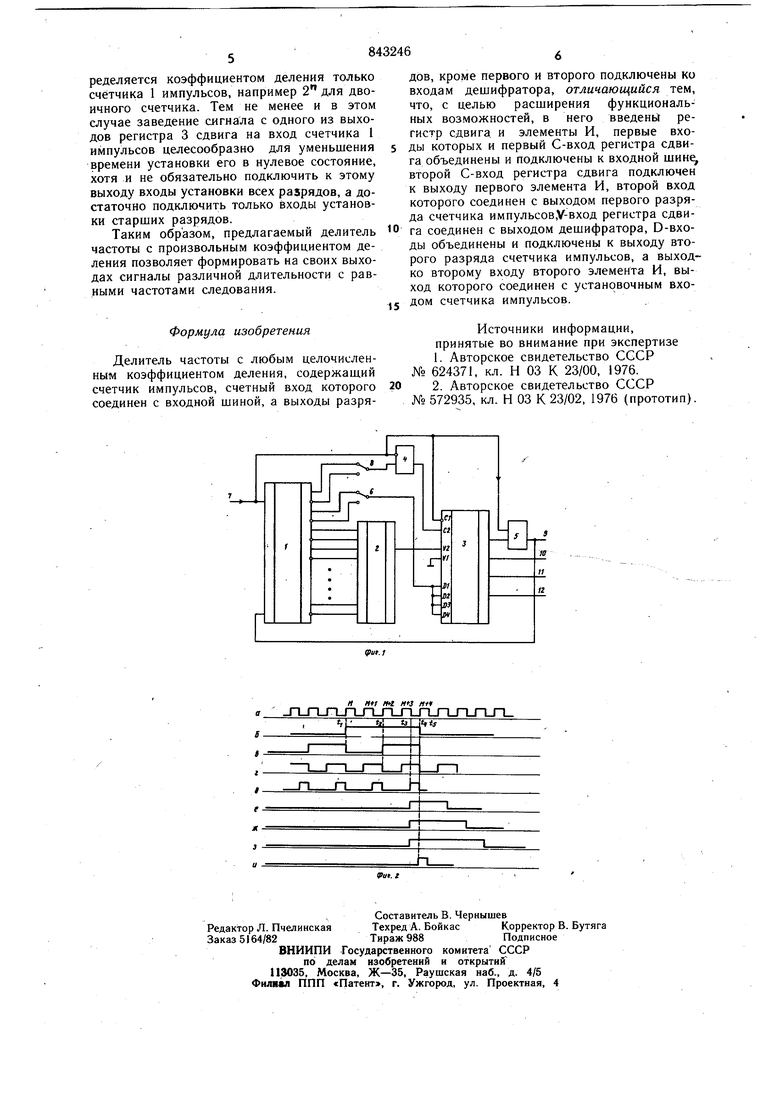

На фиг. 1 представлена структурная электрическая схема делителя частоты с любым целочисленным коэффициентом деления; на фиг. 2 - временные диаграммы, поясняющие работу устройства. Устройство содержит счетчик I импульсов, дешифратор 2, регистр 3 сдвига, элементы И 4 и 5. Выход дешифратора подключен кУ,-входу регистра, 3 сдвига, вход синхронизации Сг. которого соединен с выходом первого элемента И 4. D-входы регистра 3 сдвига через переключате;ль б подключены к выходу второго разряда счетчика I импульсов, У гвход регистра 3 сдвига соединен с нулевой точкой источника питания, а С|-вход регистра 3 сдвига объединен с первыми входами элементов И, первым входом счетчика 1импульсов соединен с входной шиной 7. Второй вход первого элемента И 4 через переключатель 8 соединен с выходом первого разряда счетчика 1 импульсов, второй вход второго элемента И 5 соединен с первым выходом регистра 3 сдвига, причем выход элемента И 5 является первым выходом устройства (шина 9), вторым, третьим и четвертым выходами устройства являются другие выходы регистра 3 сдвига(соответственно шины 10, 11 и 12), а установочный вход счетчика 1 импульсов соединен с выходом второго элемента И 5. Предлагаемое устройство работает следующим образом. Регистр 3 сдвига может в зависимости от сигнала, подаваемого на его У -вход, работать в двух режимах. Если на У входе высокий потенциал, то на все выходы регистра 3 сдвига по сигналу синхронизации на СгВходе одновременно передается состояние входов регистра 3 сдвига. Если же на У.входе имеется низкий потенциал, то по сигналу синхронизации, подаваемому на С.,-вход происходит сдвиг информации, причем в первом разряде регистра 3 сдвига происходит запись сигнала, имеющегося в этот момент на V,-входе. В исходном состоянии счетчик I импульсов обнулен, т.е. на прямых выходах всех разрядов и всех выходах регистра 3 сдвига имеются низкие потенциалы. Дешифратор 2подключен к счетчику I импульсов таким образом, что высокий потенциал на его выходе появляется после поступления на вход счетчика 1 импульсов М импульсов, где Мчисло, равное сумме весов п-2 разрядов счетчика импульсов при представлении коэффициента деления в двоичной . Элемент И 5 закрыт низким потенциалом с первого выхода регистра 3 сдвига. Сигнал с выхода элемента И 4. в случае подключения его первого входа через переключатель 8 к инверсному выходу первого разряда счетчика 1 импульсов не оказывает на- регистр 3 сдвига влияния, так как низкий потенциал HaVi-входе регистра 3 сдвига соответствует его заботе в режиме сдвига по сигналам синхронизации подаваемым на С|-вход. Работу делителя рассмотрим для случая, когда первый вход элемента И 4 и D-входы регистра 3 сдвига подключены через переключатели 8 и 6 к прямым выходам первых двух разрядов счетчика 1 импульсов. Изменение положения переключателей б и 8 соответствует соединению Д-входов регистра сдвига 3 и первого входа элемента И 4 с прямым или инверсным выходами второго и первого разрядов счетчика 1 импульсов. Непрерывная последовательность входных импульсов (фиг. 2а) поступает на вход счетчика 1 импульсов. По М-му импульсу в момент t, (фиг. 2а) появляется высокий потенциал на выходе дешифратора 2 и соответственно на У гвходе регистра 3 сдвига (фиг. 26), Начиная с этого момента регистр 3 сдвига записывает на своих выходах потенциалы на D-входах по сигналам синхронизации на Ci-входе. Так как в момент потенциала на выходе дешифратора 2, второй и первый разряды счетчика 1 импульсов установлены в «О (фиг. 2в и г), то состояние выхода регистра 3 сдвига не изменяется (при использовании суммирующего счетчика). По М +2 -му импульсу в момент времени 12. появляется сигнал на D-входах регистра 3 сдвига (фиг. 2в), но, так как в этот момент сигнал синхронизации на Сх входе регистра 3 сдвига отсутствует вследствие состояния «О в первом разряде счетчика 1 импульсов (фцг. 2г), то состояние выходов регистра 3 сдвига также не изменяется. М + 3-мй импульс подготавливает к открытию элемент И 4, на выходе которого в момент tj появляется сигнал, совпадающий с паузой входной последовательности импульсов (фиг; 2а и д). Совпадение сигналов на С гвходе и D-входах регистра 3 сдвига в момент времени tj (фиг. 2а, в к д) вызывает появление на его выходах и соответственно на выходах устройства - шинах 10, 11 и 12 (фиг. 2е, ж к з) высоких потенциалов. Появление сигнала на выходе элемента И 5 (шина 9) совпадает с М + 4-ым входным импульсом в момент t (фиг. 2ы). Подключение входов обнуления всех разрядов счетчика 1 импульсов к выходу элемента И 5 обеспечивает установку начального состояния счетчика 1 импульсов. При этом потенциал на У -входе регистра 3 сдвига в момент t (фиг. 26) опять становится низким и он начинает работать в режиме сдвига по сигналам входной последовательности импульсов, подаваемым на С|-вход регистра 3 сдвига. Так как У| -вход регистра 3 сдвига подключен к нулевой точке источника питания то первый же импульс входной последовательности, следующий после обнуления счетчика 1 импульсов вызывает появление низкого потенциала на первом выходе регистра 3 сдвига и запрещает прохождение сигналов через элемент И 5 фиг. 2ы). Сигналы на щинах 10, И и 12 продолжаются соответственно еще один, два и три периода следования импульсов входной последовательности (фиг. 2е, ж, и з). Предлагаемый делитель частоты может работать также в качестве формирователя импульсов. При этом выходная частота определяется коэффициентом деления только счётчика 1 импульсов, например 2 для двоичного счетчика. Тем не менее и в этом случае заведение сигнала с одного из выходов регистра 3 сдвига на вход счетчика I импульсов целесообразно для уменьшения времени установки его в нулевое состояние, хотя и не обязательно подключить к этому выходу входы установки всех разрядов, а достаточно подключить только входы установТакиГобрХоГпредлагаемый делитель ки старших разрядов. частотьГс коэффициентом деления позволяет формировать на своих выходах сигналы различной длительности с равными частотами следования.

Формула изобретения

Делитель частоты с любым целочисленным коэффициентом деления, содержаший счетчик импульсов, счетный вход которого соединен с входной шиной, а выходы разряИсточники информации, принятые во внимание при экспертизе

1Авторское свидетельство СССР 624371, кл. Н 03 К 23/00, 1976.

2Авторское свидетельство СССР

572935, кл. Н 03 К 23/02, 1976 (прототип). дов, кроме первого и второго подключены ко входам дешифратора, отличающийся тем, что, с целью расширения функциональных возможностей, в него введень1 регистр сдвига и элементы И, первые входы которых и первый С-вход регистра сдвига объединены и подключены к входной шине, второй С-вход регистра сдвига подключен к выходу первого элемента И, второй вход которого соединен с выходом первого разряда счетчика импульсовУ-вход регистра сдвига соединен с выходом дешифратора, D-BXO ды объединены и подключе нь, к выходу в™рого разряда счетчика импульсов, а выходко второму входу второго элемента И, выход которого соединен с установочным входом счетчика импульсов.

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с любым целочисленным коэффициентом деления | 1981 |

|

SU953736A2 |

| Делитель частоты с любым целочисленным коэффициентом деления | 1981 |

|

SU953735A2 |

| Делитель частоты | 1980 |

|

SU921095A1 |

| Делитель частоты следованияиМпульСОВ | 1979 |

|

SU839066A1 |

| Устройство для задержки импульсов | 1980 |

|

SU951677A1 |

| Устройство для измерения интервалов между центрами импульсов | 1980 |

|

SU938249A1 |

| Преобразователь частота-код | 1979 |

|

SU839047A1 |

| Делитель частоты следования импульсов с переменным коэффициентом деления | 1978 |

|

SU786010A1 |

| Умножитель частоты следования импульсов | 1981 |

|

SU1018219A1 |

| Устройство для задержки импульсов | 1980 |

|

SU921066A1 |

Htt IM тз ни

itf

tr t}

Авторы

Даты

1981-06-30—Публикация

1979-08-06—Подача