1

Изобретение отнсюится к импульсной тезснике, в частности к делителям частоты, и может бьггь использовано в автоматике, вычислительной технике и радиотехнике.

По основному авт. св. № 843246, известен делитель частоты с любым целочисленным коэффициентом деления, содержащий счетчик импульсов, счетный вход которого соединен с входной шиной ,д а выходы разрядов, кроме первого н второго, подключены к входам дешифратора, регистр и элементы И, первые входы которых и первый С-вход регистра сдвига объединены и подключены к вход ной шине, второй С-вход регистра сдвиге подключен к выходу первого элемента И, второй вход которого соединен с выходом первого разряда счетчика импульсов, V -вход регистра сдвига соединен 20 С выходом дешифратора, D-вхойы объединены и подключены к выходу второгчэ разряда счетчика импгтпьсов, а выход к второму входу второго элемента И,

выход которого соединен с vcTaHOB04Hbtt|i входом счетчика импульсов 1 .

Недостаток известного устройства значительное количество потребляемой мощности.

Цель изофетения - уменыпение потр бляемой мощности.

Поставленная цель достигается тем, что в делитель частоты с любым целочисленным коэффициентом деления введен дополшггельный элемент И, первый вход которого соединен с выходом, двшифратора, второй вход - с выходом последнего разряда регистра сдвига и дополнительным установочным входом c4eiN. чика импульсов, а выход - сV-входом регистра сдвига.

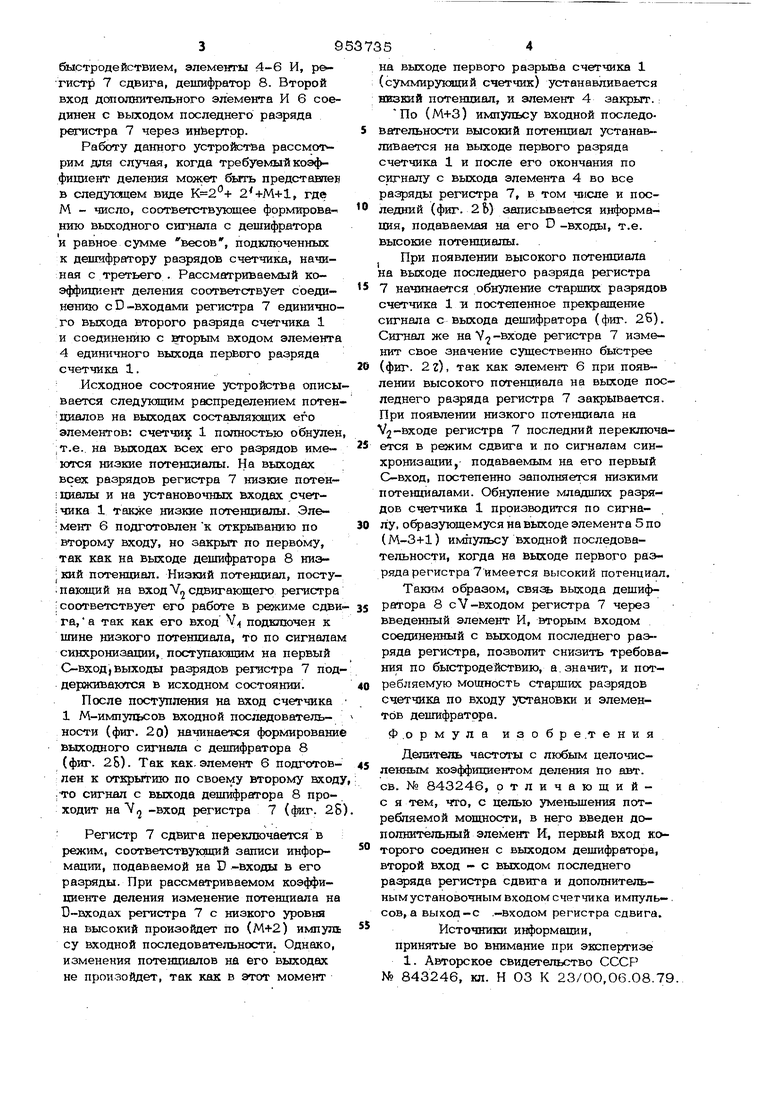

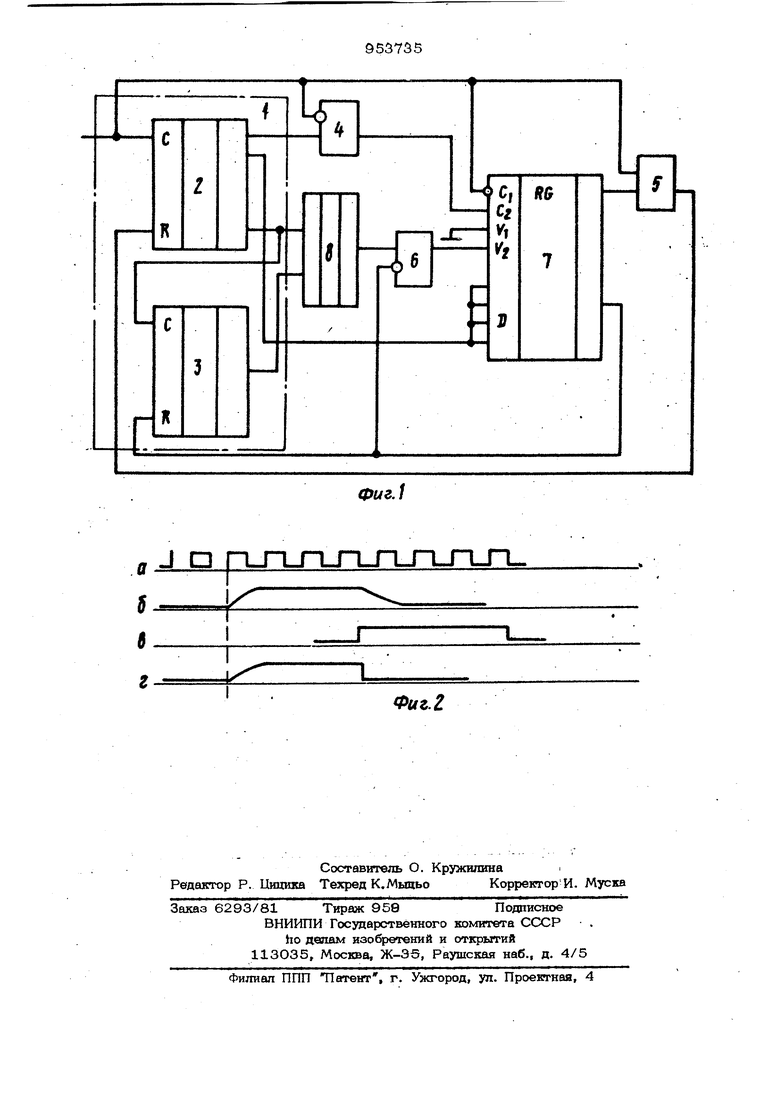

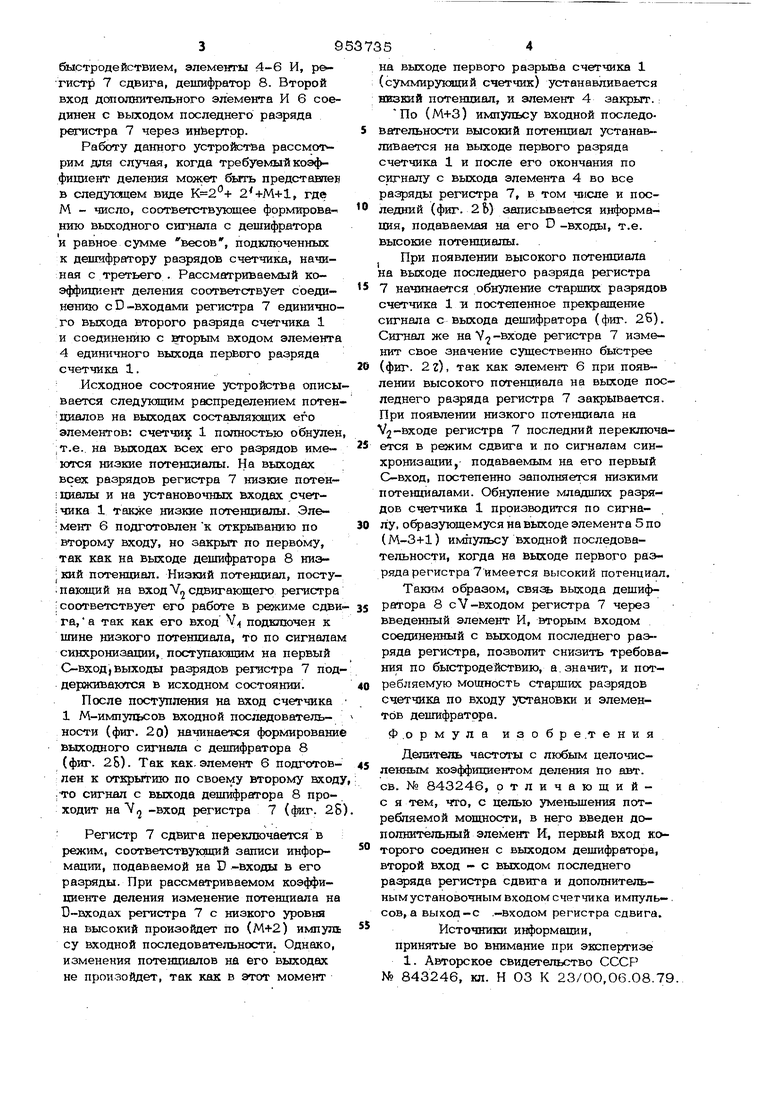

На фиг. 1 представлена структурная схема устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит Ъчетчик 1 импульсов, состоящий из последовательно i включенных 2 с высоким быстродействием н разрядов 3 с низким быстродействием, элементы 4-6 И, регистр 7 сдвига, дешифратор 8. Второй вход дополнительного элемента И 6 соединен с выходом последнего разряда регистра 7 через инвертор. Работу данного устройства рассмотрим для случая, когда требуемый коэффициент деления может быть представлен в следующем виде , где М - число, соответствующее формированию выходного сигнала с дешифратора и равное сумме весов, подключенных к дешифратору разрядов счетчика, начиная с третьего . Рассматриваемый коэффициент деления соответствует соединению с D-входами регистра 7 единично го выхода второго разряда счетчика 1 и соединению с вторым входом элемента 4 единичного выхода первого разряда счетчика 1. ; Исходное состояние устройства описы вается следующим распределением потен циалов на выходах составлязсщих его элементов: счетчик 1 полностью обнулен ;т.е.. на выходах всех его разрядов имеются низкие потенциалы. На выходах всех разрядов регистра 7 низкие потен- : циалы и на установочных входах счет;чика 1 также низкие потенциалы. Эле: мент 6 подготовлен к открыванию по второму входу, но закрыт по первому, так как на выходе дешифратора 8 низкий потенциал. Низкий потенциал, посту пакяций на вход V сдвигающего регистра I соответствует его работе в режиме сдви га, а так как его вход V подключен к шине низкого потенциала, то по сигнала синхронизашш, постутшюощм на первый С-вхоД) выходы разрядов регистра 7 под держиваются в исходном состоянии. После поступления на вход счетчика 1 М-импульсов входной посяедовательности (фиг. 2о) начинается формировани выходного сигнала с дешифратора 8 (фиг. 2S). Так как. элемент 6 подготовлен к открытию по своему второму вход ;то сигнал с выхода дешифратора 8 проходит на Л/,2 -вход регистра 7 (фиг. 28 Регистр 7 сдвига переключается в режим, соответствующий записи инфо{ мации, подаваемой на D -входы в его разряды. При рассматриваемом коэффициенте деления изменение потенциала на D-входах регистра 7 с низкого уровня на высокий произойдет по (М+2) импуль су входной последовательности. Однако, изменения потенциалов на его выходах не произойдет, так как в этот момент на выходе первого разрыва счетчика 1 (суммирующий счетчик) устанавливается низкий потенциал, и элемент 4 закрыт.: По (М+З) импульсу входной последовательности высокий потенциал устанавливается на выходе первого разряда счетчика 1 и после его окончания по сигналу с выхода элемента 4 во все разряды регистра 7, в том числе и последний (фиг. 2 Ь) записывается информация, подаваемая на его D -входы, т.е. высокие потенциалы. При появлении высокого потенциала на выходе последнего разряда регистра 7 начинается обнуление старших разрядов счетчика 1 и постепенное прекращение сигнала с выхода дешифратора (фиг. 2б). Сигнал же на V- -входе регистра 7 изменит свое значение существенно быстрее (фиг. 2г), так как элемент 6 при появлении высокого потенциала на выходе последнего разряда регистра 7 закрывается. При появлении низкого потенциала на V2-Входе регистра 7 последний переключается в режим сдвига и по сигналам синхронизации, подаваемым на его первый С-вход, постепенно заполняется низкими потенциалами. Обнуление младших разрядов счетчика 1 производится по сигнаjiy, образующемуся на выходе элемента 5 по (М-3+1) импульсу входной последовательности, когда на выходе первого разряда регистра 7ймеется высокий потенциал. Таким образом, связь выхода дешифратора 8 сV-входом регистра 7 через введенный элемент И, вгоръпл входом соединенный с выходом последнего разряда регистра, позволит снизить требования по быстродействию, а. значит, и потребляемую мошпность старших разрядов счетчика по входу установки и элементов дешифратора. ф.ормула из обре.тения Делитель частоты с любым целочисленным коэффициентом деления По авт. св. № 843246, отличающийс я тем, что, с целью уменьшения потребляемой мощности, в него введен дополнительный элемент И, первый вход которого соединен с выходом дешифратора, второй вход - с выходом последнего разряда регистра сдвига и дополнительным установочным входом счетчика импуль-. сов, а выход-с .-входом регистра сдвига. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 843246, кл. Н 03 К 23/00,06.08.79.

Фиг.1

| название | год | авторы | номер документа |

|---|---|---|---|

| Делитель частоты с любым целочисленным коэффициентом деления | 1981 |

|

SU953736A2 |

| Делитель частоты с любым целочисленнымКОэффициЕНТОМ дЕлЕНия | 1979 |

|

SU843246A1 |

| Делитель частоты | 1980 |

|

SU921095A1 |

| Устройство для задержки импульсов | 1980 |

|

SU951677A1 |

| Делитель частоты следованияиМпульСОВ | 1979 |

|

SU839066A1 |

| Генератор случайного потока чисел | 1982 |

|

SU1053106A1 |

| Адаптивный умножитель частоты | 1989 |

|

SU1793538A1 |

| Устройство для задержки импульсов | 1980 |

|

SU921066A1 |

| ТЕЛЕВИЗИОННЫЙ ИЗМЕРИТЕЛЬ КООРДИНАТ | 1985 |

|

SU1454225A1 |

| Устройство для формирования импульсных последовательностей | 1988 |

|

SU1596438A1 |

J а

а д В

г

Фиг2

Авторы

Даты

1982-08-23—Публикация

1981-01-14—Подача