С54) УСТРОЙСТВО для ПРЕОБРАЗОВАНИЯ КОДОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для программного счета штучных изделий | 1981 |

|

SU964678A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1987 |

|

SU1444958A1 |

| Устройство для логарифмирования чисел | 1984 |

|

SU1257846A1 |

| Устройство для сортировки двоичных чисел | 1982 |

|

SU1049900A1 |

| Преобразователь двоичного кода в двоично-десятичный | 1982 |

|

SU1042010A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1989 |

|

SU1662005A1 |

| УСТРОЙСТВО ДЛЯ КОНТРОЛЯ КАЧЕСТВА КАНАЛА СВЯЗИ | 2002 |

|

RU2216865C1 |

| Преобразователь кодов | 1987 |

|

SU1444957A1 |

| Устройство для сравнения двух частот | 1986 |

|

SU1330630A1 |

| Устройство для контроля настройки музыкальных инструментов | 1984 |

|

SU1170495A1 |

Изобретение относится к цифровой вычислительной технике и может быть использовано при построении преобразователей в автсматизированных системах управления и контроля.

Известно устройство для преобразования кодов, содержащее входной и выходной счетчики, генератор тактовых импульсов, подключенный через схему совпадения на оба счетчика, из которых входной счетчик работает в режиме вычитания, а выходной - в реки,ме сложения 1.

Недостатки данного устройства состоят в том, что оно преобразует лишь один код на входе в один код на выходе, обладает малым быстродействием.

Наиболее близким решением данной задачи по технической сущности и схемному построению является устройстйо для преобразования кодов, содержащее блок совпадения, первый вход которого соединен с выходом основного счетчика, первый вход последнего подключен к выходу генератора тактовых импульсов и блоку ввода информации, причем на второй вход счетчика и первый вход генератора тактовых импульсов подан сигнал обнуления, блок выделения признака кода и дополнительный счетчик, где выход выделения признака кода подключен к управляющим входаил основного и диполнительного счетчиков, выход блока ввода информации подключен к входу блока выделения признаков кода и второму входу блока совпадения, выход которого соединен с вторь входом генератора тактовых импульсов, выход ко10торого подключен к первому входу дополнительного счетчика, на второй вход которого подан сигнал обнуления.

В этом устройстве преобразование

15 производится в соответствии с количеством тактов, поступающих на основной и дополнительный счетчики, до совпадения кодовых комбинаций основного счетчика и преобразуемой

20 входной кодовой комбинации. При этом счетчики производят смену кодовых комбинаций только в сторону увеличения.

При последующем поступлении на

25 преобразование кодовой комбинации меньшей, чем предыдущая, необходимо производить сброс счетчиков, как основного, так и дополнительного, и опять производить перебор кодовых

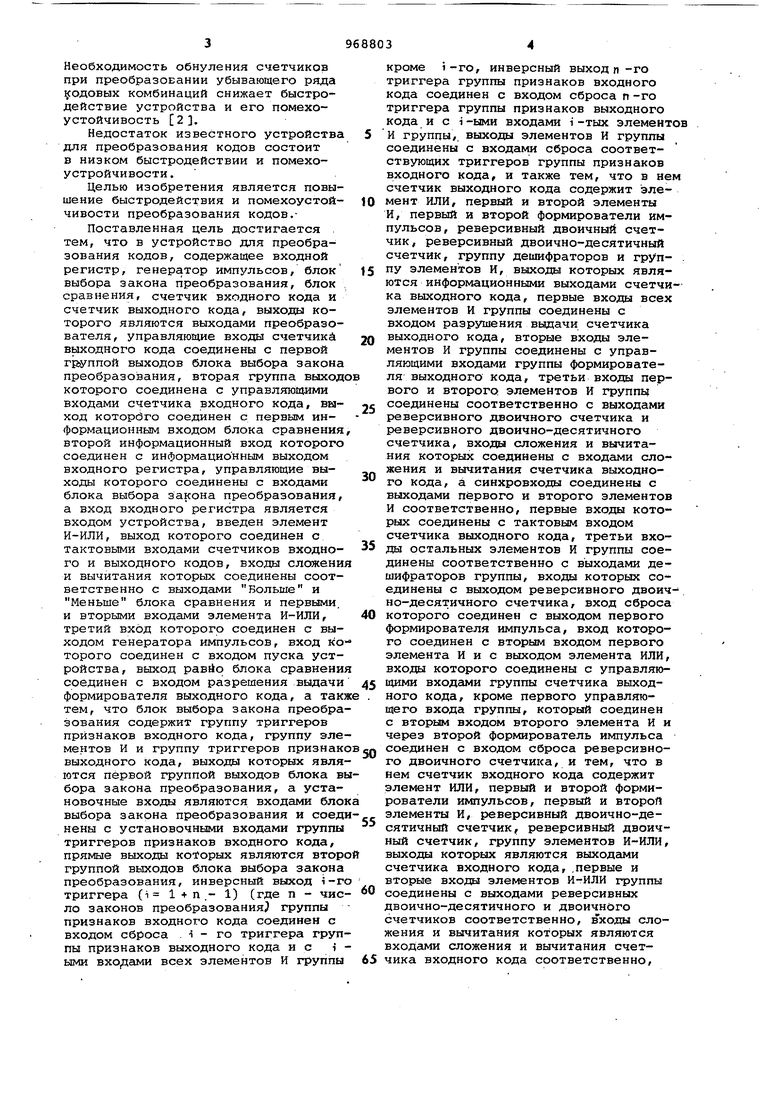

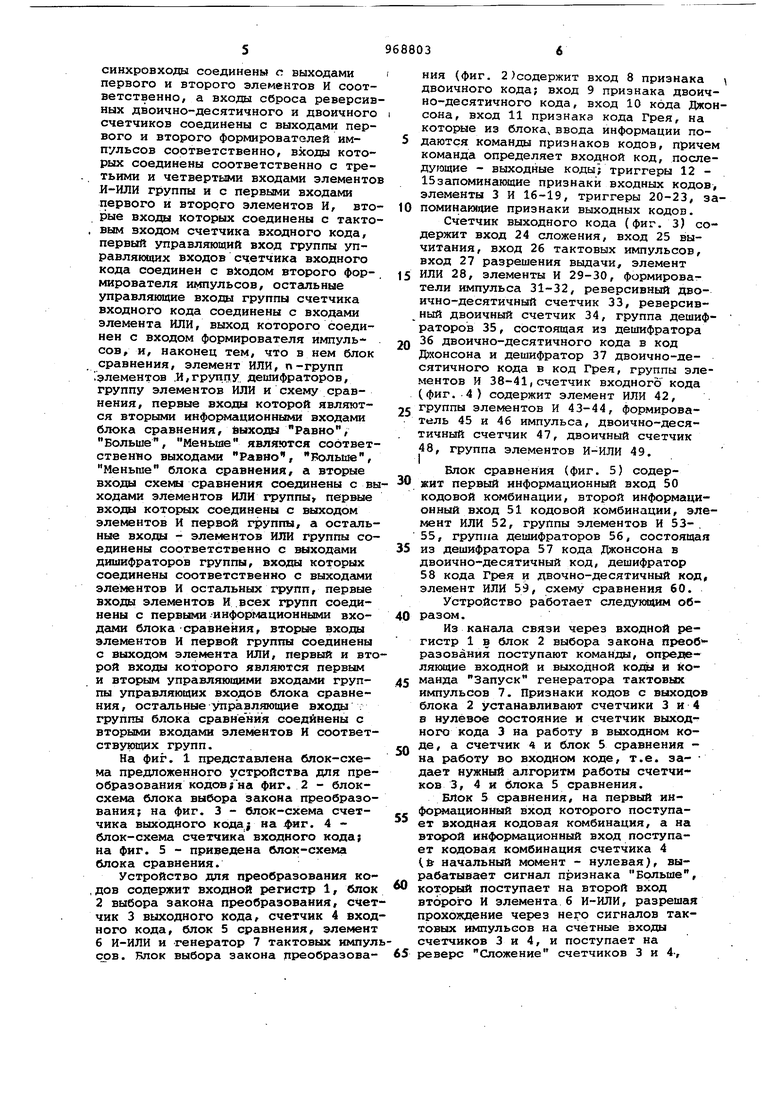

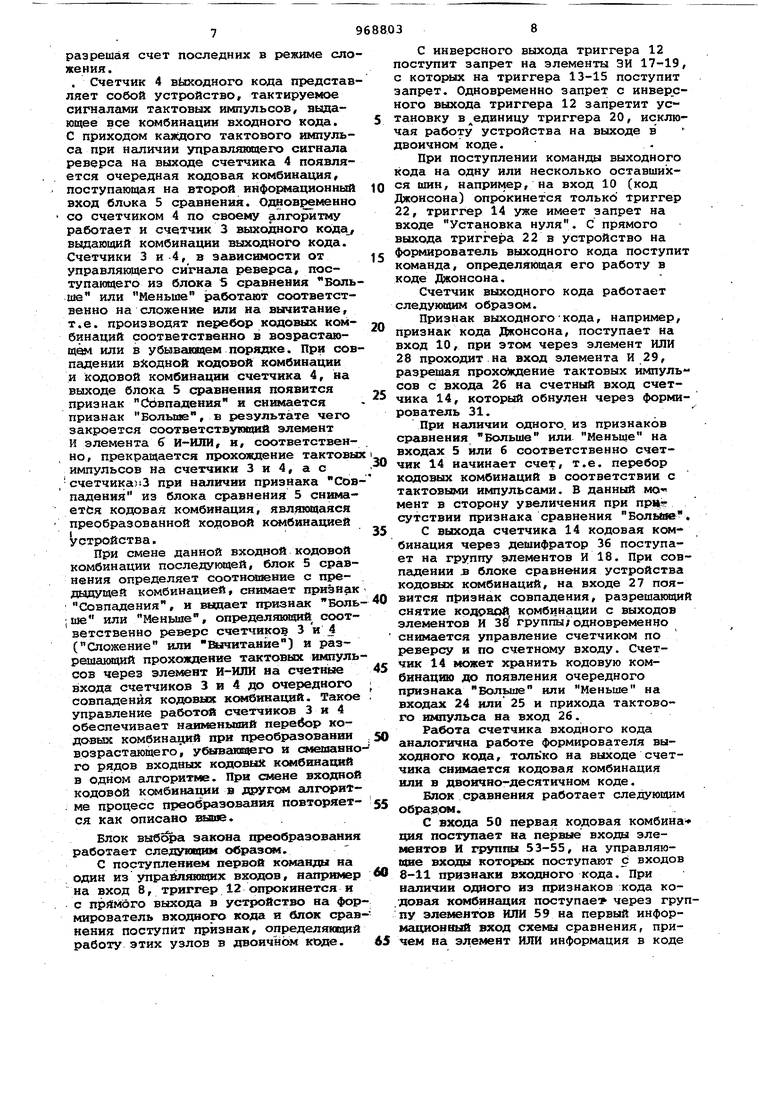

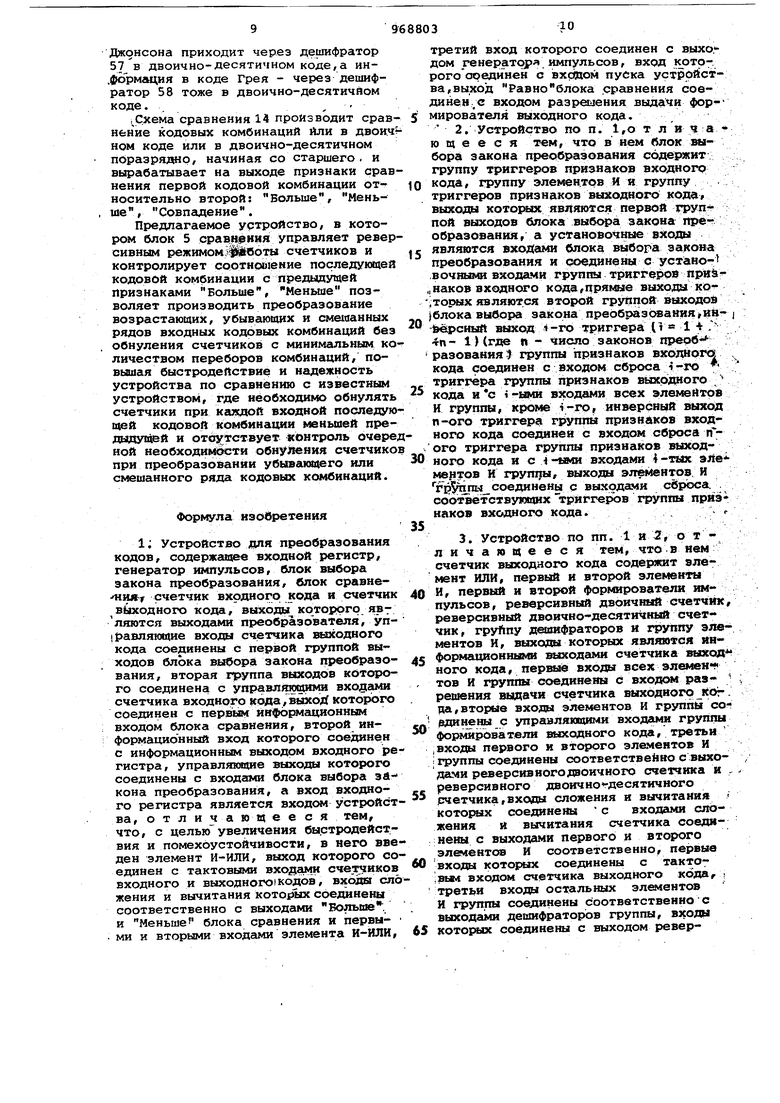

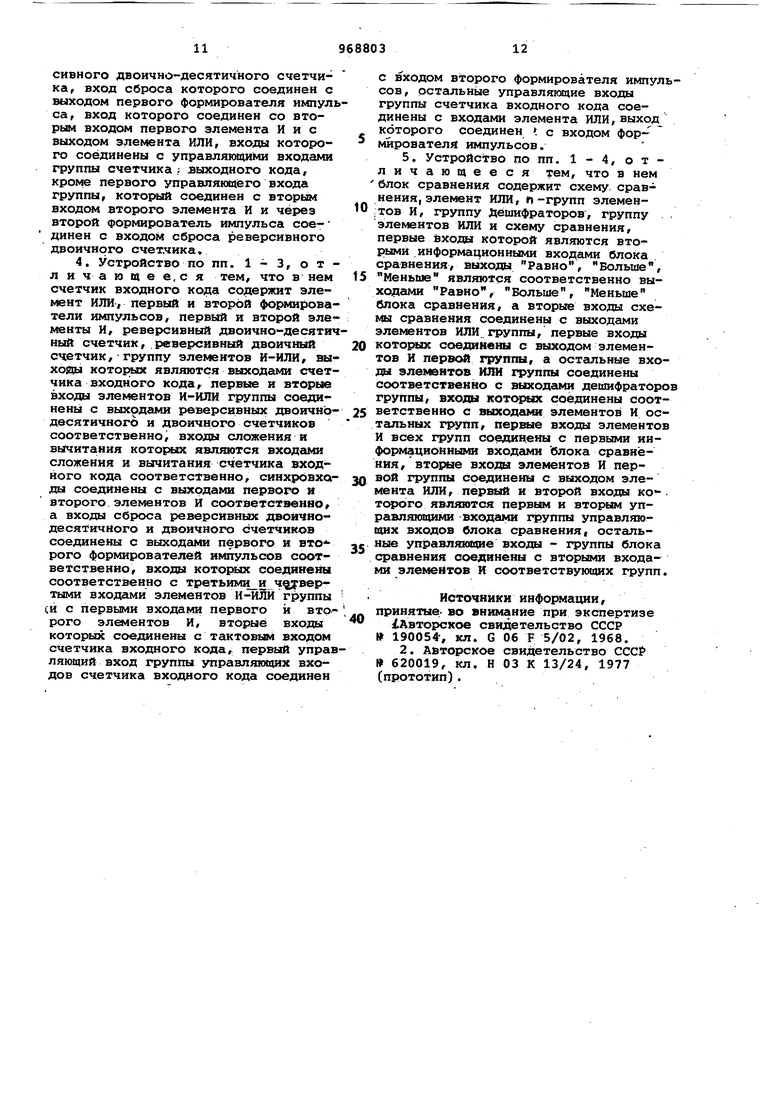

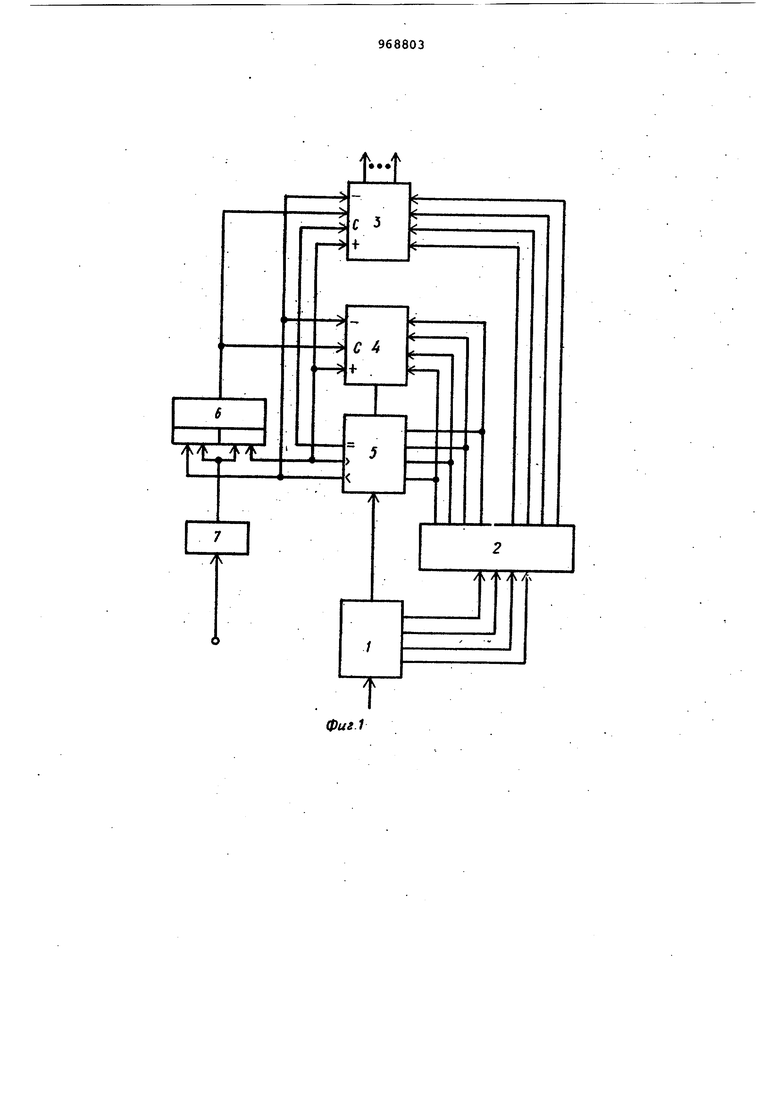

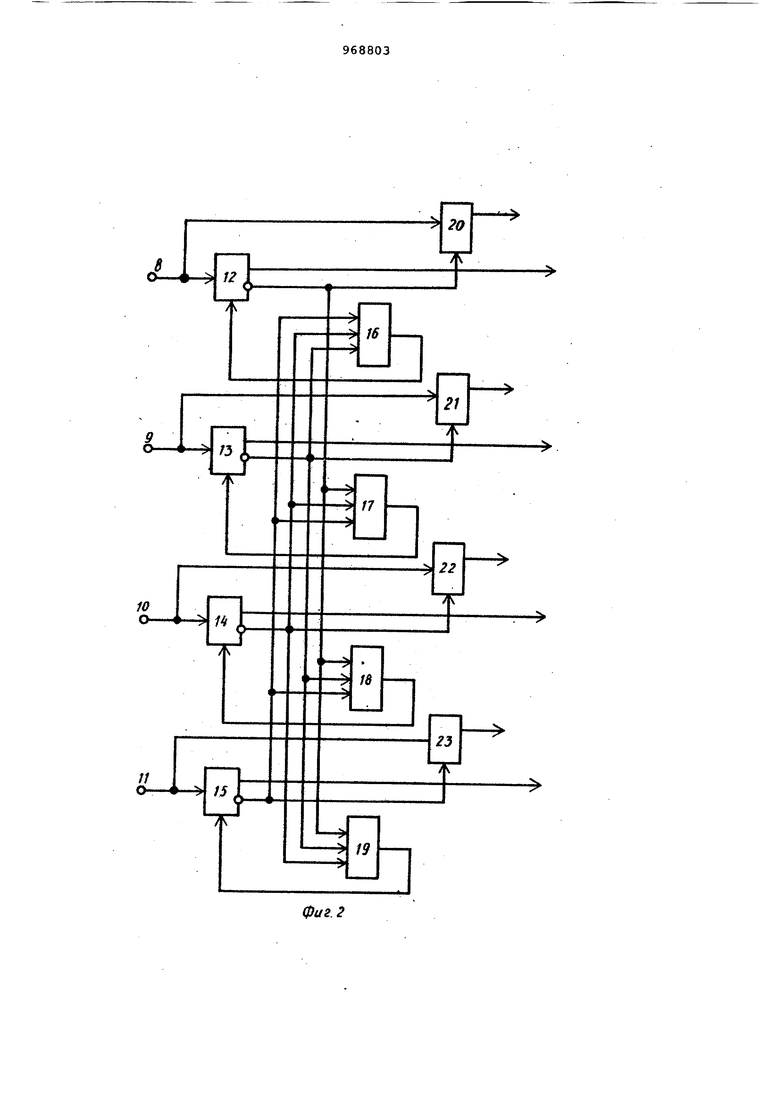

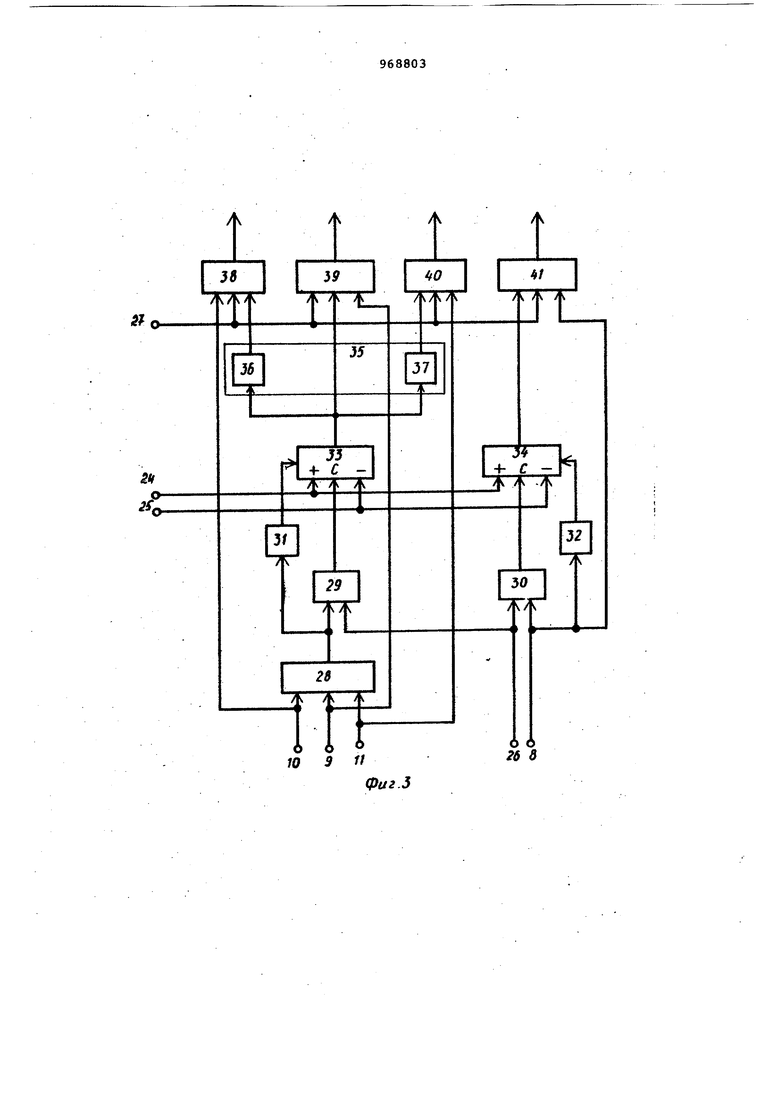

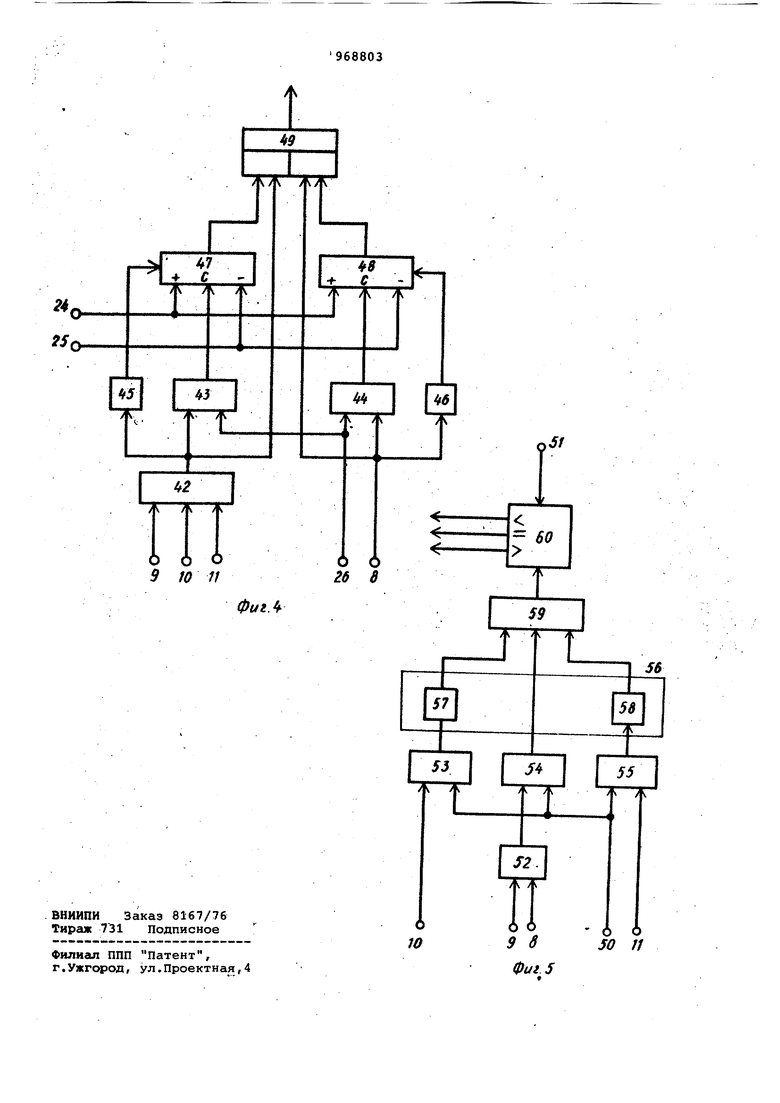

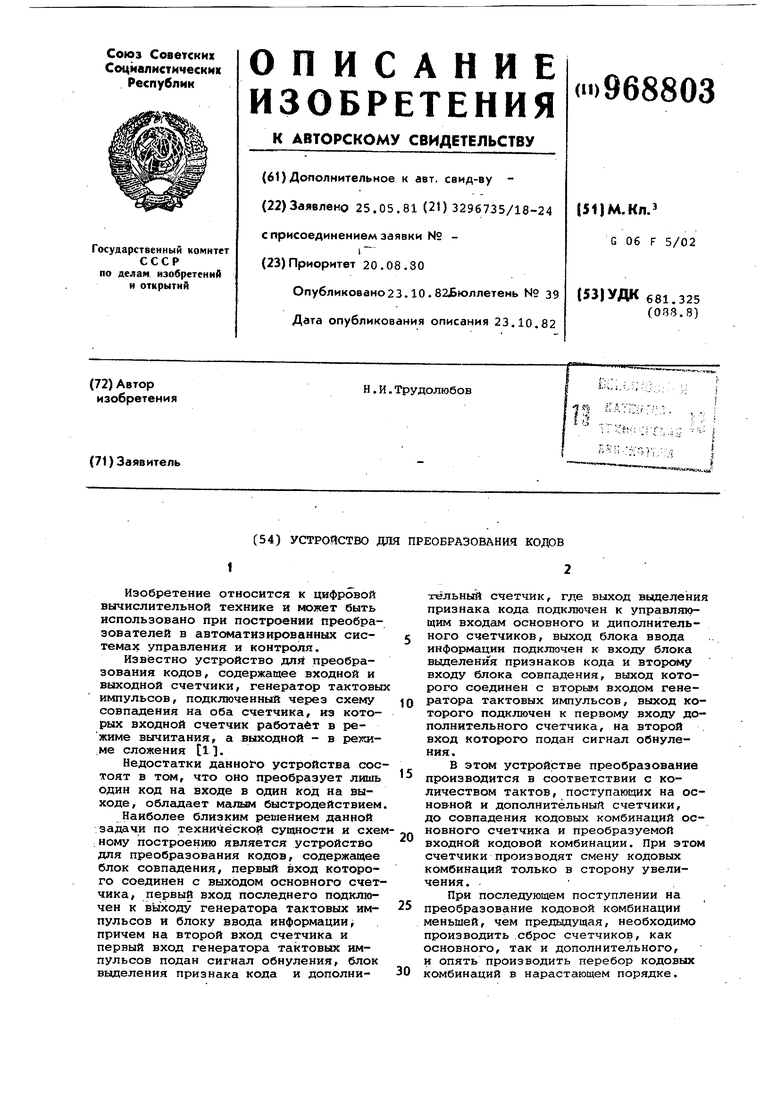

30 комбинаций в нарастающем порядке. Необходимость обнуления счетчиков при преобразовании убывающего ряда одовых комбинаций снижает быстродействие устройства и его помехоустойчивость 2. Недостаток известного устройства для преобразования кодов состоит в низком быстродействии и помехоустройчивости. Целью изобретения является повышение быстродействия и помехоустойчивости преобразования кодов.Поставленная цель достигается . тем, что в устройство для преобразования кодов, содержащее входной регистр, генератор импульсов, блок выбора закона преобразования, блок сравнения, счетчик входного кода и счетчик выходного кода, выходы которого являются выходами преобразователя, управляющие входы счетчики выходного кода соединены с первой группой выходов блока выбора закона преобразования, вторая группа выходо которого соединена с управляющими входами счетчика входного кода, выход KOTopdro соединен с первым информационным входом блока сравнения второй информационный вход которого соединен с информационным выходом входного регистра, управляющие выходы которого соединены с входами блока выбора закона преобразования, а вход входного регистра является входом устройства, введен элемент И-ИЛИ, выход которого соединен с тактовыми входами счетчиков входного и выходного кодов, входы сложения и вычитания которых соединены соответственно с выходами Больше и Меньше блока сравнения и первыми, и вторыми входами элемента И-ИЛИ, третий вход которого соединен с выходом генератора импульсов, вход ко торого соединен с входом пуска устройства, выход равйо блока сравнения соединен с входом разрешения выдачи формирователя выходного кода, а такж тем, что блок выбора закона преобра зования содержит группу триггеров признаков входного кода, группу эле ментов И и группу триггеров признако выходного кода, выходы которых явля ются первой группой выходов блока вы бора закона преобразования, а установочные входы являются входами бло выбора закона преобразования и соед иены с установочными входами группы триггеров признаков входного кода, прямые выходы являются втор группой выходов блока выбора закона преобразования, инверсный выход i-r триггера (i 1 п .- 1) (где п - чис ло законов преобразования группы признаков входного кода соединен с входом сброса .i-ro триггера груп пы признаков выходного кода и с i ымк вхо(ами всех элементов И группы кроме 1 -го, инверсный выход п -го триггера группы признаков входного кода соединен с входом сброса п-го триггера группы признаков выходного кода и с i-ыми входами i-тых элементов И группы,, выходы элементов И группы соединены с входалш сброса соответствующих триггеров группы признаков входного кода, и также тем, что в нем счетчик выходного кода содержит элемент ИЛИ, первый и второй элементы И, первый и второй формирователи импульсов, реверсивный двоичный счетчик, реверсивный двоично-десятичный счетчик, группу дешифраторов и груп- , пу элементов И, выходы которых являются информационными выходами счетчика выходного кода, первые входы всех элементов И группы соединены с входом разрушения выдачи счетчика выходного кода, вторые входы элементов И группы соединены с управляющими входами группы формирователя выходного кода, третьи входы первого и второго элементов И группьз соединены соответственно с выходами реверсивного двоичного счетчика и реверсивного двоично-десятичного счетчика, входы сложения и вычитания которых соединены с входами сложения и вычитания счетчика выходного кода, а синхровходы соединены с выходами первого и второго элементов И соответственно, первые входы которых соединены с тактовым входом счетчика выходного кода, третьи входы остальных элементов И группы соединены соответственно с выходами дешифраторов группы, входы которых соединены с выходом реверсивного двоично-десятичного счетчика, вход сброса которого соединен с выходом первого формирователя импульса, вход которого соединен с вторым входом первого элемента И и с выходом элемента ИЛИ, входы которого соединены с управляющими входами группы счетчика выходного кода, кроме первого управляющего входа группы, который соединен с вторым входом второго элемента И и через второй формирователь импульса соединен с входом сброса реверсивного двоичного счетчика, и тем, что в нем счетчик входного кода содержит элемент ИЛИ, первый и второй формирователи импульсов, первый и второй элементы И, реверсивный двоично-десятичный счетчик реверсивный двоичный счетчик, группу элементов И-ИЛИ, выходы которых являются выходами счетчика входного кода, .первые и вторые входа элементов И-ИЛИ группы соединены с выходами реверсивных двоично-десятичного и двоичного счетчиков соответственно, входы сложения и вычитания которых являются входами сложения и вычитания счетчика входного кода соответственно. синхровходы соединены с выходами первого и второго элементов И соответственно, а входы сброса реверсив ных двоично-десятичного и двоичного счетчиков соединены с выходами первого и второго формирователей импульсов соответственно, входы которых соединены соответственно с третьими и четвертыми входами элементо И-ИЛИ группы и с первыми входами первого и второго элементов И, вто рые входы которых соединены с такто вым входом счетчика входного кода, первый управляющий вход группы управляющих входов счетчика входного кода соединен с входом второго формирователя импульсов, остальные управляющие входы группы счетчика входного кода соединены с входами элемента ИЛИ, выход которого соединен с входом формирователя импульсов, и, наконец тем, что в нем блок сравнения, элемент ИЛИ, п-групп .элементов .И,группу дешифраторов, группу элементов ИЛИ и схему сравнения, первые входы которой являются вторыми информационными входами блока сравнения, йыхо.2б:1 Равно, Больше, Меньше являются соответ ственно выходами Равно, Больше, Меньше блока сравнения, а вторые входы схемы сравнения соединены с вы ходами элементов ИЛИ группыу первые входы которых соединены с выходом элементов И первой группы, а остальные входы - элементов ИЛИ группы соединены соответственно с выходами дишифраторов группы, входал которых соединены соответственно с выходами элементов И остальных , первые входы элементов И всех групп соединены с первыми информационными входами блока сравнения, вторые входы элементов И первой группы соединены с выходом элемента ИЛИ, первый и вто рой входы которого являются первым и вторым управляинцими входами группы управляющих входов блока сравнения, остальные управляющие входы группы блока сравнения соединены с вторыми входами элементов И соответствующих групп. На фиг. 1 представлена блок-схема предложенного устройства для преобразования кодов; на фиг. 2 - блоксхема блока выбора закона преобразования; на фиг. 3 - блок-схема счетчика выходного кода; на фиг. 4 блок-схема счетчика входного кода; на фиг. 5 - приведена блок-схема блока сравнения. Устройство для преобразования ко,дов содержит входной регистр 1, блок 2 выбора закона преобразования, счет чик 3 выходного кода, счетчик 4 вход ного кода, блок 5 сравнения, элемент 6 И-ИЛИ и генератор 7 тактовых импул сов. Блок выбора закона преобразования (фиг. 2 )содержит вход 8 признака двоичного кода; вход 9 признака двоично-десятичного кода, вход 10 кода Джонсона, вход 11 признака кода Грея, на которые из блока ввода информации подаются команды признаков кодов, причем команда определяет входной код, последующие - выходные коды; триггеры 12 15запоминающие признаки входных кодов, элементы 3 И 16-19, триггеры 20-23, запоминаюйше признаки выходных кодов. Счетчик выходного кода (фиг. 3) содержит вход 24 сложения, вход 25 вычитания, вход 26 тактовых импульсов, вход 27 разрешения выдачи, элемент ИЛИ 28, элементы И 29-30, формирователи импульса 31-32, реверсивный двоично-десятичный счетчик 33, реверсивный двоичный счетчик 34, группа дешифраторов 35, состоящая из дешифратора 36 двоично-десятичного кода в код Джонсона и дешифратор 37 двоично-десятичного кода в код Грея, группы элементов И 38-41,счетчик входного кода (фиг..4) содержит элемент ИЛИ 42, группы элементов И 43-44, формирователь 45 и 46 импульса, двоично-десятичный счетчик 47, двоичный счетчик 48, группа элементов И-ИЛИ 49. Блок сравнения (фиг. 5) содержит первый информационный вход 50 кодовой комбинации, второй информационный вход 51 кодовой комбинации, элемент ИЛИ 52, группы элементов И 53-, 55, группа дешифраторов 56, состоящая из дешифратора 57 кода Джонсона в двоично-десятичный код, дешифратор 58 кода Грея и двочно-десятичный код, элемент ИЛИ 59, схему сравнения 60. Устройство работает следукжщм образом. Из канала связи через входной регистр 1 в блок 2 выбора закона преобразования поступают команды, определяющие входной и выходной коды и команда Запуск генератора тактовых импульсов 7. Признаки кодов с выходов блока 2 устанавливают счетчики 3 и 4 в нулевое состояние и счетчик выходного кода 3 на работу в выходном коде, а счетчик 4 и блок 5 сравнения на работу во входном коде, т.е. за- дает нужный алгоритм работы счетчиков 3, 4 я блока 5 сравнения. БЛОК 5 сравнения, на первый информационный вход которого поступает входная кодовая комбинация, а на втснюй информационный вход поступает кодовая комбинация счетчика 4 (fr начальный момент - нулевая), вырабатывает сигнал признака Больше, который поступает на второй вход второго И элемента 6 И-ИЛИ, разрешая прохождение через него сигналов тактовых импульсов на счетные входы счетчиков 3 и 4, и поступает на реверс Сложение счетчиков 3 и 4-, разрешая счет последних в режиме сло жения. , Счетчик 4 BtJXOflHoro кода представ ляет собой устройство, тактируемое сигналами тактовьзх импульсов, выдающее все комбинации входного кода. С приходом каждого тактового импульса при наличии улравляяяцего сигнгша реверса на выходе счетчика 4 появляется очередная кодовая комбинация поступающая на второй ннфо1 1ационный вход блика 5 сравнения. Одновременно со счетчиком 4 по своему алгоритму работает и счетчик 3 выходного кода, выдающий комбинации выходного кода. Счетчики 3 к 4, в зависимости от управлякадего сигнала реверса, поступающего из блока 5 сравнения Боль ше или Меньше работают соответственно на сложение или на вычитание, т.е. производят перебор кодовых комбинаций соответственно в воэрастающом или в убываюцем порядке. При сов падении входной кодовой комбинации и кодовой комбинации счетчика 4, на выходе блока 5 сравнения появится признак СЬвпадения и снимается признак Больше, в результате чего закроется соответствувхций элемент И элемента 6 И-ИЛИ, и, соответственно , прекращается прохождение тактовы импульсов на счетчики 3 и 4, а с счетчикаяЗ при наличии признака Сов падения из блока сравнения 5 снимаетйя кодовая комбинация, являющаяся преобразованной кодовой ксялбинацией устройства. При смене данной входной кодовой комбинации последукядей, блок 5 сравнения определяет соотнсянение с предыдущей комбинацией, снимает призн цс Совпадения, и выдает признак Боль ;ше или Меньше, определяишщй, соответственно реверс счетчико 3 и 4 (Сложение или &лчитанйе) и разрешающий прохождение тактовых импуль сов через элемент И-ИЛИ на счетные входа счетчиков 3 и 4 до очередного совпадения кодовых комбинаций. Такое управление работой счетчиков 3 и 4 обеспечивает наименьший перебор кодовых комбинаций при преобразовании врзрастаннцего, убывгиощего и смешанно го рядов входных кодовых кстбинаций в одном алгоритме. При входной КОДОВОЙ комбинации в друге алгоритме процесс преобразования повторяется как описано 1шлше. БЛОК выбора закона преобразования работает следующим х$разси14. С поступлением первой команды на один из упрайлянадих входов, нгшример на вход 8, триггер 12 опрокинется и с прямого выхода в устройство на фор мирователь входного кода и блок срав нения поступит признак, определяющий работу этих узлов в двоичном коде. С инверсного выхода триггера 12 поступит запрет на элементы ЭЙ 17-19, с которых на триггера 13-15 поступит запрет. Одновременно запрет с инверсного выхода триггера 12 запретит установку в единицу триггера 20, исключая работу устройства на выходе в двоичном коде. При поступлении команды выходного кода на одну или несколько оставшихся шин, нaпpи 4ep, на вход 10 (код Джонсона) опрокинется только триггер 22, триггер 14 уже имеет запрет на входе Установка нуля. С прямого выхода триггера 22 в устройство на формирователь выходного кода поступит команда, определяющая его работу в коде Джонсона. Счетчик выходного кода работает следующим образом. Признак выходногокода, например, признак кода Джонсона, поступает на вход 10, при этом через элемент ИЛИ 28 проходит на вход элемента И 29, разрешая прохо)кдеииё тактовых импуль сов с входа 26 на счетный вход счетчика 14, который обнулен через формирователь 31. При наличии одного, из признаков сравнения Больше или Меньше на входах 5 или 6 соответственно счетчик 14 иачинает счет, т.е. перебор кодовых комбинаций в соответствии с тактовыми импульсами. В данный мо мент в сторону увеличения при прщг сутствии признака сравнения Больше, С выхода счетчика 14 кодовая комбинация через дешифратор 36 поступает на группу элементов И 18. При совпадении J3 блоке сравнения устройства кодовых ксшбинаций, на входе 27 появится признак совпадения, разрешающий снятие кодовой комбинации с выходов элементов И 38i групгщ/ одновременно снимается управление счетчиком по реверсу и по счетному входу. Счетчик 14 южет хранить кодовую комбинацию до появления очередного признака Больше или Меньше на входах 24 или 25 и прихода тактового Ш4пульса на вход 26. Работа счетчика входного кода ангшогична работе формирователя выходного кода, только на выходе счетчика снимается кодовая комбинация шш в двоично-десятичном коде. Блок сравнения работает следующим обра.г,. С входа 50 первая кордовая комбина- ция поступает на первые входы элементов И группы 53-55, на управляющие входы которых поступают с входов 8-11 признаки входного кода. При наличии одного из признаков кода кодовая комбинация поступаем через группу элементов ИЛИ 59 на первый информационный вход схекод сравнения, причем на элемент ИЛИ информация в коде Джонсона приходит через дешифратор 57 в двоично-десятичном коде,а ин.формгщия в коде Грея - через дешифратор 58 тоже в двоично-десятичном коде.. ,,С,хема сравнения 14 производит срав нение кодовых комбинаций или в двоич ном коде или в двоично-десятичном поразрядно, начиная со старшего . и вырабатывает на выходе признаки срав нения первой кодовой комбинации относительно второй: Больше, Меньше, Совпадение. Предлагаемое устройство, в котором блок 5 сраэи эння управляет ревер сивным режимом Шюоты счетчиков и контролирует соотношение последующей КОДОВОЙ комбинации с предыдущей Признакг1ми Больше, Меныие позволяет производить преобразование возрастающих, убывающих и смешанных рядов входных кодовых комбинаций без обнуления счетчиков с минимальным ко личеством переборов комбинаций, повышая быстродействие и надежность устройства по сравнению с известным устройством, где необходимо обнулять счетчики при каждой входной последую щей кодовой комбинации меньшей предыдущей и ота | тствует кЪнтроль очере ной необходим1а сти счетчико при преобразовании убывакедего или смешанного ряда кодовых комбинаций. Формула изобретения 1; Устройство для преобразования кодов, содержащее входной регистр, генератор импульсов, блок выбора закона преобразования, блок сравнетият счетчик входного кода и счетчик вЬисодного кода, выходы которого яв7 ляются выходгихи преобразователя, уп{равляющие входы счетчика клходного кода соединены с первой группой выходов блока выбора закона преобразования, вторая группа выходов которого соединена с управляющими счетчика входного к()аа,гыхоЛ которого соединен с первым йнформгщионным входом бълока сравнения, второй информационный вход которого соедине н с информационным выходом входного ре гистра, управлякяцие выходы которого соединены с входами блока выбора зй кона преобразования, а вход входного регистра является входом Устройст ва, отличающееся тем, что, с цельюГувеличения быстродействия и помехоустойчивости, в него вве ден элемент И-ИЛИ, выход которого со единен с тактовыми входами счетчиков входного и ВЫХОДНОГО кодов, входа сло жения и вычитания KOTOpla соедшнены соответственно с выходами Больше, и Меньше блока сравнения и первыми и вторыми входами элемента И-ИЛИ, третий вход которого соединен с выхо дом генераторя.импульсов, вход которого соединен с iexpinoM пуска устройства, выход Равно блока .сравнения соединен.с входом разр яения выдачи формирователя выходного кода. 2.Устройство по п. 1,о т л и 9 а ю щ е е с я тем, что в нем блок выбора закона преобразования содержит группу триггеров признаков входного кода., группу элементов И и группу триггеров признаков выходного кода ВЫХОЛМ КОТОрКОС являются первой ГРУПгпой выходов блока выбора закона преобразования, а установочные входы являются входами блока выбора закона преобразования и соединены с устано.вочньаки входами группы трнгХероВ прн наков входного к ода, прямые выходы ко являются второй группой выходов )блока выбора закона преобразования ин-j .рсный выход i-го триггера (i « 14 f4n- 1) (где n - число законов прврб- ; разования) группы признаков вхо даога , кода соединен с входом сброса i-го ; триггера группы признаков wxbnaoro кода и с i-ыми входами всех Э1лемейтов И группы, кроме f-го, инвер жый выход п-ого триггеру группы признаков входного кода соединен с входом сброса rfого триггера группы признаков выходного кода и с 4 -VKK входами 4 -тых э/ieментов И , выходы элементов. И гр$щ1Ш соединены с выходами сброса. . соответствующих трйггерюв группы приз наков входного кода. . 3.Устройство по пп. I и 2, о т личающееся тем, что в ием счетчик выходного кода содержит элемент ИЛИ, первый и второй элементы И, первый и второй форгдарователи импульсов, реверсивный двоичный счетчик, реверсивный двончно-десятнчньй) счет чик, rpyftny дешифраторов я группу элементов И, выходы которых являются йнформационшфо выходг1ми счетчика выход ного кода, первые входы всех элемвя тов И группы соединены с входом раз- ; решения выдачи счетчика выходного кОгTia,вторые входы элементов И грушш со« эдинепы с управляющими входами группы формирователи выходного кода, третьи ,входы первого и второго элементов И группы соединены соответствейно с выходами реверсивного двоичного счетчика и . . реверсивного двоично-десятичного рчвтчика,входы сложения и вычитания которых соединены с входами сложения и вычитания счетчика соединены с выходами первся-о и второго элементов И соответственно, первые входы которых соединены с такто 8ым входом счетчика выходйого кбда, ; третьи входы остальных элементов И группы соединены соответственно с выходами дешифраторов группы, входы котоцжк соединены с выходом реверсивного двоично-десятичного счетчика, вход сброса которого соединен с выходом первого формирователя импульса, вход которого соединен со вторым входом первого элемента И и с выходом элемента ИЛИ, входы которого соединены с управляющими входами группы счетчика ; выходного кода, кроме первого управлякяц е го входа группы, котораЛ соединен с вторым входом второго элемента И и чёреэ второй формирователь импульса сое- динен с входом сброса реверсивного двоичного счетчика,

с входом второго формирователя импульсов, остальные управляющие входы группы счетчика входного кода соединены с входами элемента ИЛИ, выход которого соединен с входом формирователя импульсов.

блок сравнения содержит схему, сравнения, элемент ИЛИ, П-групп элемен:тов И, группу Дешифраторов, группу

элементов ИЛИ и схему сравнения, первые входы которой являются втор али информационными входами блока сравнения, выходы Равно, Больше,

5 Меньше являются соответственно выходами Равно, Больше, Меньше блока сравнения, а вторые входы схемы сравнения соединены с выходами элекюнтов ИЛИ группы, первые входы

0 которых соединены с выходом элементов И первой группы, а остальные входы злемвйтов: ИЛИ группы соединены соответственно с выходби«1 дешифраторов группы, входы соединены соответственно с выходами элементов И остальных групп, первые входы элементов И всех групп соединены с первыми информационными входами блока сравнения, входы элементов И перQ вой группы соединены с выходом элемента ИЛИ, первый и второй входы ко торбго являются первым и вторым управляющими входгши группы управляющих входов блока сравнения, остальные управляющие входы - группы блока сравнения соединены с вторыми входами элементов И соответствующих групп

Источники информации, принятые- во внимание при экспертизе

Авторское свидетельство СССР 190054-, кл. G Об F 5/02, 1968.

. I . . , Ф Ф.

/

м

/ V / k у ГТч

фиг. 2

10 Э ft

26 8

фиг.5

f /).

rC.

«7 С

I

/V Л

J

V /

«

«5

т:

V / V

J/

/V / I

6 о о

6 6

Z6 6

7/

фигЛ

55

4

55

I

Авторы

Даты

1982-10-23—Публикация

1981-05-25—Подача