(54) УСТРОЙСТВО ТАКТОВОЙ СИНХРОНИЗАЦИИ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство тактовой синхронизации | 1978 |

|

SU784016A1 |

| Двухступенчатый параллельно-последовательный регенератор | 1985 |

|

SU1246394A1 |

| Устройство циклового фазирования аппаратуры передачи дискретной информации | 1989 |

|

SU1626432A1 |

| Адаптивный корректор межсимвольной интерференции | 1987 |

|

SU1540009A1 |

| Устройство выделения опорного сигнала | 1977 |

|

SU653758A1 |

| Устройство для тактовой синхронизации | 1989 |

|

SU1642591A1 |

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЦВМ С КАНАЛОМ СВЯЗИ | 1991 |

|

RU2011217C1 |

| Формирователь сигналов с заданным законом изменения фазы | 1986 |

|

SU1385239A1 |

| Устройство для сбора и первичной обработки информации датчиков | 1976 |

|

SU643894A1 |

| Устройство выбора каналов для разнесенного приема | 1988 |

|

SU1525925A1 |

I

Изобретение относится к электросвязи и может использоваться для выделения колебаний тактовой частоты в системах передачи данных с амплитудно-фазовой модуляцией.

Известно устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, блок добавления-вычитания и первый делитель частоты 1.

Однако известное устройство характеризуется недостаточной помехоустойчивостью.

Цель изобретения - повыщение помехоустойчивости.

Поставленная цель достигается тем, что ,в устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, блок добавления-вычитания и первый делитель частоты, введены анализатор межсимвольных искажений (МСИ) преобразователь, два коммутатора сигналов, второй делитель частоты, блок формирования импульсов установки и считывания, блок памяти и блок формирования отстающих и опережающих стробимпульсов, при этом выход анализатора МСИ через .преобразователь

подключен к одному из входов первого коммутатора сигналов, два выхода которого подключены к соответствующим входам реверсивного счетчика, установочный вход которого соединен с одним из входов блока формирования импульсов установки и считывания, другой выход которого подсоединен к одному извходов блока памяти, второй вход которого соединен с выходом реверсивного счетчика, а выход блока памяти соединен с одним из входов блока добавления - вычитания, к управляющему входу которого и к управляющим входам первого и второго коммутаторов сигналов и блока формирования импульсов установки и считывания подключен выход второго делителя частоты, к входу которого подключены вход блока формирования отстающих и опережающих стробимпульсов и выход первого делителя частоты, который одновременно является выходом устройства, при этом выходы блока формирования отстающих и опережающих стробимпульсов подключены к соответствующим входам второго коммутатора сигналов, выход которого подключен к второму входу анализатора МСИ.

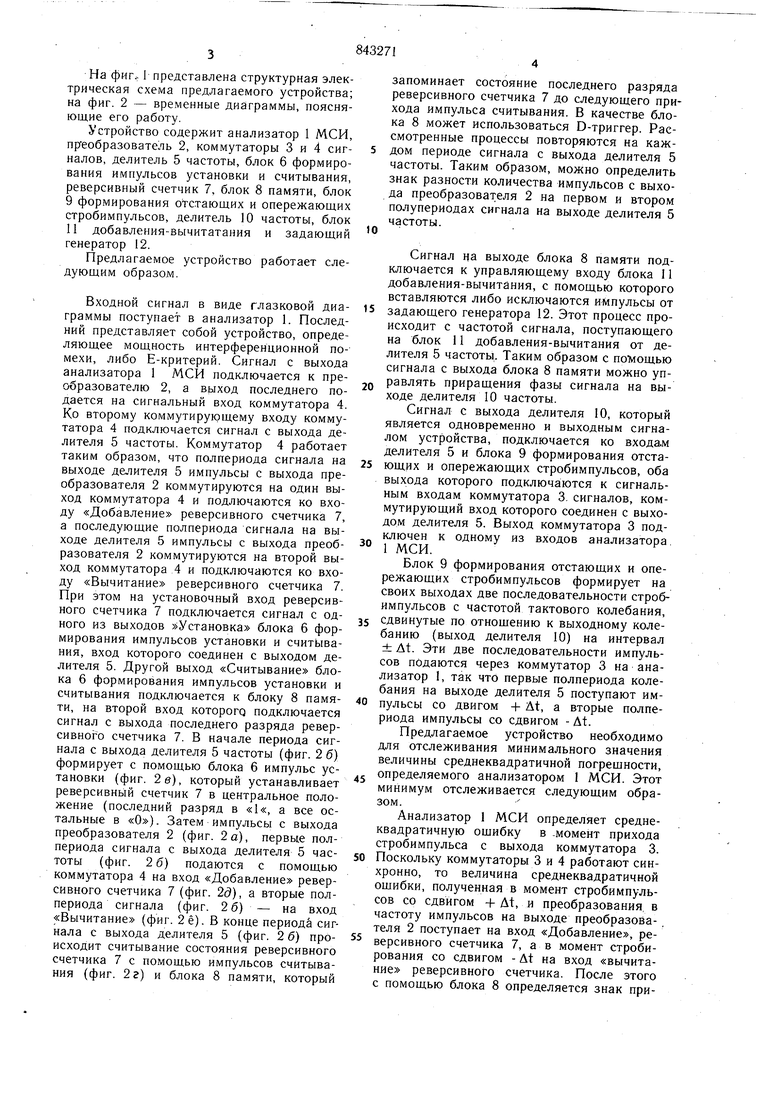

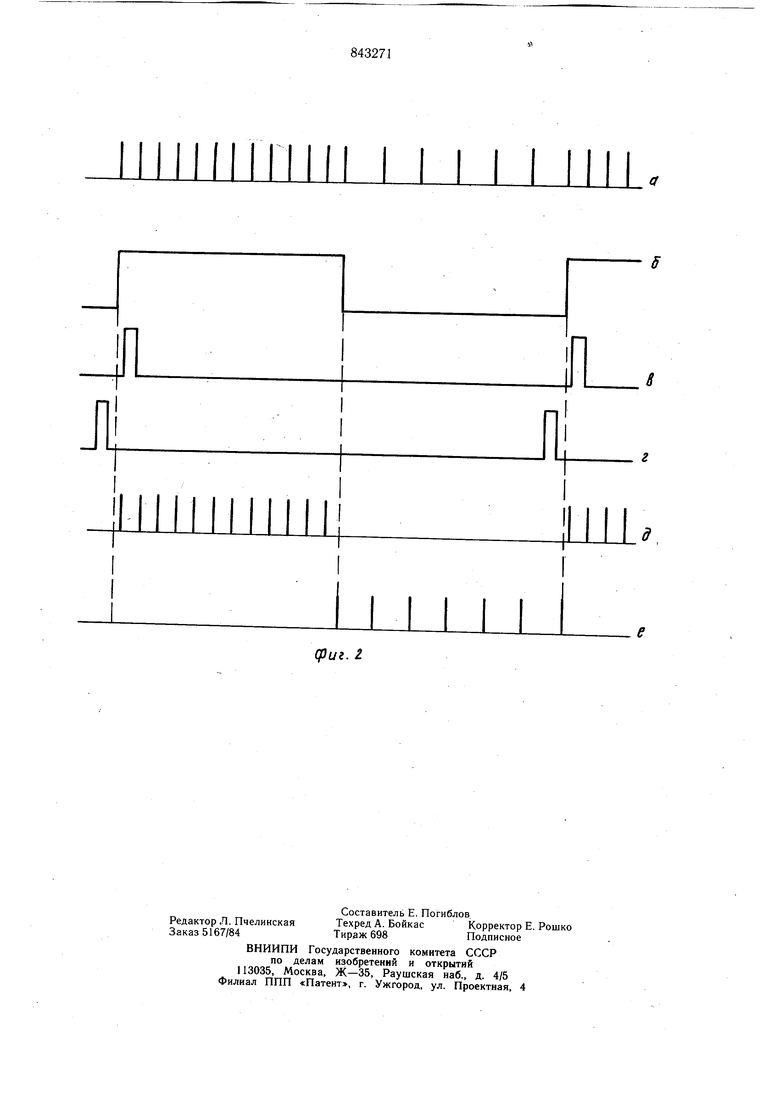

На фиг.. 1 представлена структурная электрическая схема предлагаемого устройства; на фиг. 2 - временные диаграммы, поясняющие его работу.

Устройство содержит анализатор 1 МСИ, преобразователь 2, коммутаторы 3 и 4 сигналов, делитель 5 частоты, блок 6 формирования импульсов установки и считывания, реверсивный счетчик 7, блок 8 памяти, блок 9 формирования отстающих и опережающих стробимпульсов, делитель 10 частоты, блок 11 добавления-вычитатания и задающий генератор 12.

Предлагаемое устройство работает следующим образом.

Входной сигнал в виде глазковой диаграммы поступает в анализатор 1. Последний представляет собой устройство, определяющее мощность интерференционной помехи, либо Е-критерий. Сигнал с выхода анализатора 1 МСИ подключается к преобразователю 2, а выход последнего подается на сигнальный вход коммутатора 4. Ко второму коммутирующему входу коммутатора 4 подключается сигнал с выхода делителя 5 частоты. Коммутатор 4 работает таким образом, что полпериода сигнала на выходе делителя 5 импульсы с выхода преобразователя 2 коммутируются на один выход коммутатора 4 и подлючаются ко входу «Добавление реверсивного счетчика 7, а последующие полпериода сигнала на выходе делителя 5 импульсы с выхода преобразователя 2 коммутируются на второй выход коммутатора 4 и подключаются ко входу «Вычитание реверсивного счетчика 7. При этом на установочный вход реверсивного счетчика 7 подключается сигнал с одного из выходов «Установка блока 6 формирования импульсов установки и считывания, вход которого соединен с выходом делителя 5. Другой выход «Считывание блока 6 формирования импульсов установки и считывания подключается к блоку 8 памяти, на второй вход которого подключается сигнал с выхода последнего разряда реверсивного счетчика 7. В начале периода сигнала с выхода делителя 5 частоты (фиг. 2 б) формирует с помощью блока 6 импульс установки (фиг. 2 в), который устанавливает реверсивный счетчик 7 в центральное положение (последний разряд в «1«, а все остальные в «О). Затем импульсы с выхода преобразователя 2 (фиг. 2 а), первые полпериода сигнала с выхода делителя 5 частоты (фиг. 2 б) подаются с помощью коммутатора 4 на вход «Добавление реверсивного счетчика 7 (фиг. 2д), а вторые полпериода сигнала (фиг. 26) - на вход «Вычитание (фиг. 2ё). В конце периода сигнала с выхода делителя 5 (фиг. 2 б) происходит считывание состояния реверсивного счетчика 7 с помощью импульсов считывания (фиг. 2 г) и блока 8 памяти, который

запоминает состояние последнего разряда реверсивного счетчика 7 до следующего прихода импульса считывания. В качестве блока 8 может использоваться D-триггер. Рассмотренные процессы повторяются на каждом периоде сигнала с выхода делителя 5 частоты. Таким образом, можно определить знак разности количества импульсов с выхода преобразователя 2 на первом и втором полупериодах сигнала на выходе делителя 5

частоты.

Сигнал на выходе блока 8 памяти подключается к управляющему входу блока 11 добавления-вычитания, с помощью которого вставляются либо исключаются импульсы от

задающего генератора 12. Этот процесс происходит с частотой сигнала, поступающего на блок 11 добавления-вычитания от делителя 5 частоты. Таким образом с потиощью сигнала с выхода блока 8 памяти можно управлять приращения фазы сигнала на выходе делителя 10 частоты.

Сигнал с выхода делителя 10, который является одновременно и выходным сигналом устройства, подключается ко входам делителя 5 и блока 9 формирования отстающих и опережающих стробимпульсов, оба выхода которого подключаются к сигнальным входам коммутатора 3. сигналов, коммутирующий вход которого соединен с выходом делителя 5. Выход коммутатора 3 подключен к одному из входов анализатора.

1 МСИ.

Блок 9 формирования отстающих и опережающих стробимпульсов формирует на своих выходах две последовательности стробимпульсов с частотой тактового колебания,

сдвинутые по отнощению к выходному колебанию (выход делителя 10) на интервал ± At. Эти две последовательности импульсов подаются через коммутатор 3 на анализатор 1, так что первые полпериода колебания на выходе делителя 5 поступают импульсы со двигом + At, а вторые полпериода импульсы со сдвигом - At.

Предлагаемое устройство необходимо для отслеживания минимального значения величины среднеквадратичной погрешности,

определяемого анализатором 1 МСИ. Этот минимум отслеживается следующим образом.

Анализатор 1 МСИ определяет среднеквадратичную ощибку в -момент прихода стробимпульса с выхода коммутатора 3.

Поскольку коммутаторы 3 и 4 работают синхронно, то величина среднеквадратичной ощибки, полученная в момент стробимпульсов со сдвигом -f At, и преобразования, в частоту импульсов на выходе преобразователя 2 поступает на вход «Добавление, реверсивного счетчика 7, а в момент стробирования со сдвигом - At на вход «вычитание реверсивного счетчика. После этого с помощью блока 8 определяется знак приращения величины среднеквадратичной ошибки. С помощью знака приращения фаза местного генератора (блоки 10-12) изменяется таким образом, что фаза выходного сигнала стремится к точке минимального значения величины среднеквадратичной ошибки.

Таким образом, поскольку устройство тактовой синхронизации отслеживает минимальное значение величины среднеквадратичной погрешности, то оно является более помехоустойчивым к линейным искажениям, существующим в канале, причем этот минимум отслеживается всегда и независимо от характера линейных искажений.

Формула изобретения

Устройство тактовой синхронизации, содержащее реверсивный счетчик и последовательно соединенные задающий генератор, блок добавления-вычитания и первый делитель частоты, отличающееся тем, что, с целью повыщения помехоустойчивости, введены анализатор межсимвольных искажений, преобразователь, два коммутатора сигналов, второй делитель частоты, блок фориирования импульсов установки и считывания, блок памяти и блок формирования отстающих и опережающих стробимпульсов, при этом выход анализатора МСИ через

Входной сигнал

преобразователь подключен к одному из входов первого коммутатора сигналов, два выхода которого подключены к соответствующим входам реверсивного счетчика, установочный вход которого соединен с одним из выходов блока формирования импульсов установки и считывания, другой выход которого подсоединен к одному из входов блока памяти, второй вход которого соединен с выходом реверсивного счетчика, а выход блока памяти соединен с одним из

входов блока добавления-вычитания, к управляющему входу которого и к управляющим входам первого и второго коммутаторов сигналов и блока формирования импуль сов установки и считывания подключен вы, ход второго делителя частоты, к входу которого подсоединены вход блока формирования отстающих и опережающих стробимпульсов и выход первого делителя частоты, который одновременно является выходом устройства, при этом выходы блока формиро0 вания отстаю1цих и опережающих стробимпульсов подключены к соответствующим входам второго коммутатора сигналов, выход которого подключен к второму входу анализатора МСИ.

Источники информации, пр-инятые во внимание при экспертизе 1. Тамм Ю. А. Адаптивная коррекция сигнала ПД. М., «Связь, 1978, с. 70, рис. 3.2 (прототип).

(риг. 2

Авторы

Даты

1981-06-30—Публикация

1979-09-11—Подача