(54) УСТРОЙСТВО ДЛЯ СРАВНЕНИЯ ДВОИЧНЫХ ЧИСЕЛ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения -разрядных чисел | 1976 |

|

SU641443A1 |

| Устройство для сравнения чисел | 1981 |

|

SU1013944A1 |

| Цифровой измеритель несимметричности сигналов | 1990 |

|

SU1725179A1 |

| Ассоциативное оперативное запоминающее устройство | 1986 |

|

SU1324071A1 |

| Цифровой измеритель центра тяжести видеосигналов | 1990 |

|

SU1723559A1 |

| Устройство для сравнения чисел | 1977 |

|

SU726527A1 |

| Устройство для сравнения двоичных чисел | 1974 |

|

SU631914A1 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| АКУСТООПТИЧЕСКИЙ АНАЛИЗАТОР СПЕКТРА | 1992 |

|

RU2024026C1 |

| СУММАТОР КОМБИНАЦИОННО-НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262736C1 |

Изобретение относится к автоматике и вычислительной технике и может быть использовано при реализации технических средств приема информации от ЭВМ. Известно устройства для сравнения двух чисел в цифровом коде, состоящее из п каскадов, содержащих логические элементы И, ИЛИ и НЕ Cl . Недостатки этогб устройства.заклю чаются в его сложности и низкой надежности работы. Наиболее близким к изобретению является устройство для сравнения двоичных чисел, содержащее h последовательно соединенных ячеек, каждая из которыхсостоит из элементов И-НЕ причем в каждой ячейке устройства выход первого элемента И-НЕ соединен с первыми -входами второго и третьего элементов И-НЕ, выход четвертого элемента И-НЕ подключен к первым вхо дам пятого и шестого элементов И-НЕ, 1зыхода второго и пятого элементов И-НЕ соединены с вторыми входами шее того и третьего элементов И-НЕ,соответственно, первые входы первого.и четвертого элементов И-НЕ подключены к шинам соответствующего разряда первого и второго сравниваемых чисел, соответственно, выходы третьего и шестого элементов И-НЕ i-й ячейки (,...,n) устройства соединены- с вторыми входами второго и пятого элементов И-НЕ (+1)-й ячейки устройства -соответственноf J. Недостатком известного устройства является его сложность, так как оно содержит большое количество элементов И-НЕ и связей. Цель изобретения - упрощение устройства. Поставленная цель достигается тем, что в устройстве, содержащем п последовательно соединенных ячеек , каяфая из которых состоит из элементов И-НЕ, причем в каждой ячейке устройства выход первого элемента И-НЕ соединен с первыми входами.второго и третьего элементов И-НЕ, выход четвертого элемента И-НЕ подк.пючен к первым входам пятого и шестого элементов И-НЕ, выходы второго и пятого элементов И-НЕ соединены, с вторыми входами шестого и третьего элементов И-НЕ, соответственно,первые входы -первого и четвертого элементов И-НЕ подк.пючены к шинам соответствующего разряда первого и второго сравниваемых чисел, соответственно, выходы третьего и шестого элементов И-НЕ i-й ячейки (i 1,...,п) устройст- I ва соединены с вторыми входами пятого и второго элементов И-НЕ .(+1)-й ячейки устройства соответственно, выходы третьего и шестого элементов 1-й ячейки устройства соедине- : ны с вторыми входами первого и четвертого элементов И-НЕ (+1)-й ячейки соответственно.

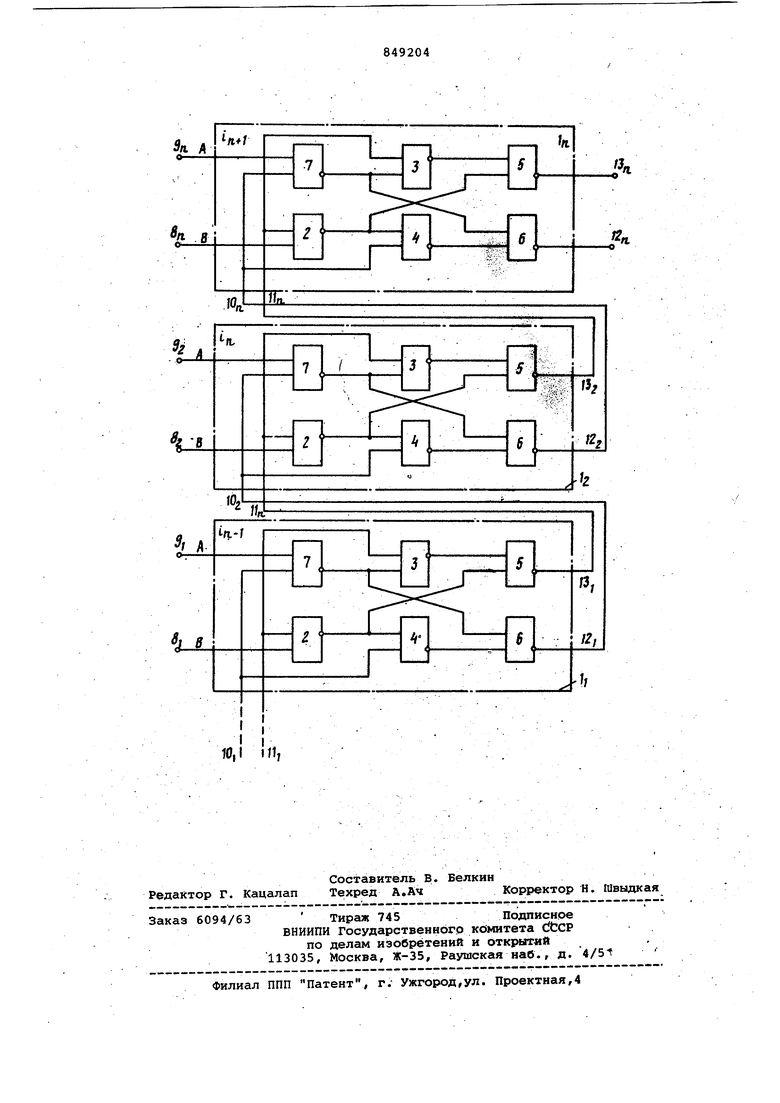

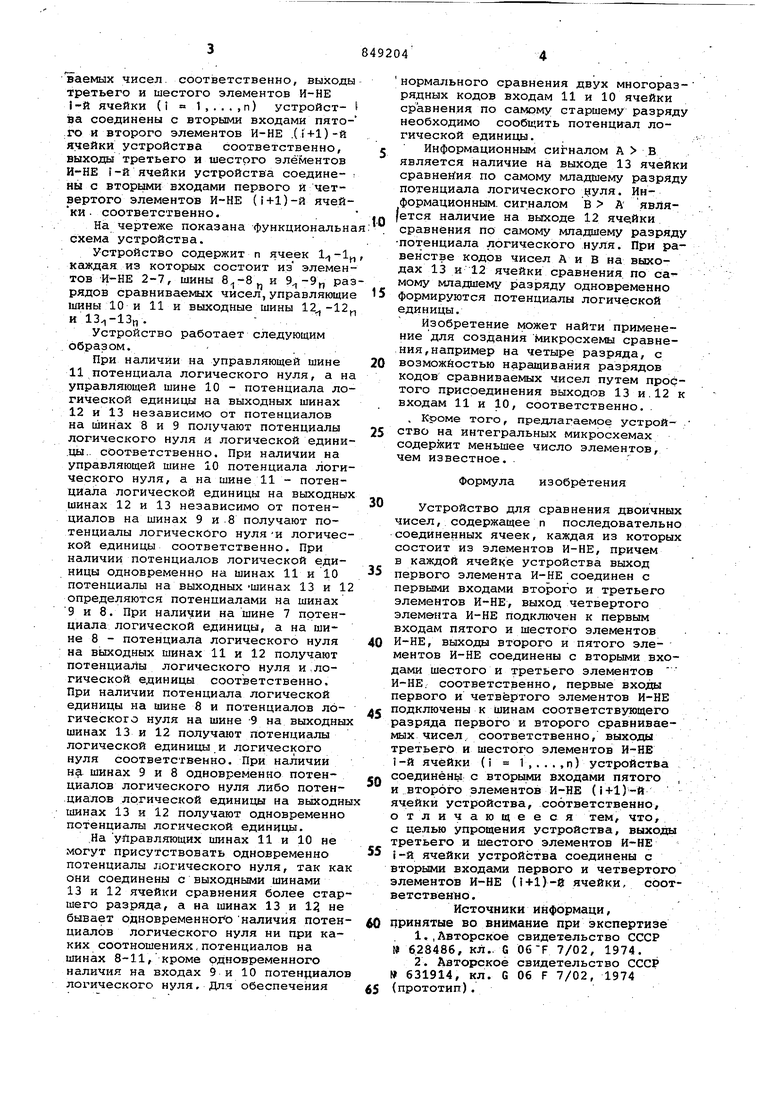

На чертеже показана функциональна схема устройства.

Устройство содержит п ячеек кашдая из которых состоит из элементов И-НЕ 2-7, шины и разрядов сравниваемых чисел,управляющие шины 10 и 11 и выходные шины и , .

Устройство работает следующим образом.

При наличии на управляющей шине

11потенциала логического нуля, а на управляющей шине 10 - потенциала логической единицы на выходных шинах

12и 13 независимо от потенциалов на шинах 8 и 9 получают потенциалы логического нуля и логической едини.цы.. соответственно. При наличии на управляющей шине 10 потенциала логического нуля, а на шине 11 - потенциала логической единицы на выходных шинах 12 и 13 независимо от потенциалов на шинах 9 и .8 получают потенциалы логического нуля и логической единицы соответственно. При наличии потенциалов логической единицы одновременно на шинах 11 и 10 потенциалы на выходных-шинах 13 и 12 определяются потенциалами на шинах

9 и 8. При наличии на шине 7 потенциала логической единицы, а на шине 8 - потенциала логического нуля на выходных шинах 11 и 12 получают потенциалы логического нуля и логической единицы соответственно. При наличии потенциала логической единицы на шине 8 и потенциалов логического нуля на шине -9 на выходных шинах 13 и 12 получают потенциалы логической единицы.и логического нуля соответственно. При наличии н шинах 9 и 8 одновременно потенциалов логического нуля либо потенциалов логической единицы на выходны шинах 13 и 12 получают одновременно потенциалы логической единицы.

.На уйравляющих шинах 11 и 10 не могут присутствовать одновременно потенциалы логического нуля, так как они соединены с выходными шинами

13и 12 ячейки сравнения более старшего разряда, а на шинах 13 и 1 не бывает одновременног о наличия потенциалов логического нуля ни при каких соотношениях,потенциалов на шинах 8-11,кроме одновременного наличия на входах 9 и 10 потенциалов логического нуля, Для обеспечения

нормального сравнения двух многоразрядных кодов входам 11 и 10 ячейки сравнения по самому старшему разряду необходимо сообщить потенциал логической единицы.

Информационным сигналом А В является наличие на выходе 13 ячейки сравнения по самому младшему разряду потенциала логического нуля. Информационным, сигналом В А явля|ется наличие на выходе 12 ячейки сравнения по самому младшему разряду потенциала логического нуля. При равенстве кодов чисел А и В на выходах 13 и 12 ячейки сравнения по са мому младшему разряду одновременно формируются потенциалы логической единицы.

Изобретение может найти применение для создания микросхемы сравнения, например на четыре разряда, с возможйостью наращивания разрядов кодов сравниваемых чисел путем простого присоединения выходов 13 и.12 к входам 11 и 10, соответственно. .

, Кроме того, предлагаемое устройство на интегральных микросхемах содержит меньшее число элементов, чем известное. .

Формула изобретения

Устройство для сравнения двоичных чисел, содержащее п последовательно соединенных ячеек, каждая из которых состоит из элементов И-НЕ, причем в каждой ячейке устройства выход первого элемента И-НЕ соединен с первыми входами второго и третьего элементов И-НЕ, выход четвертого элемента И-НЕ подключен к первым входам пятого и шестого элементов И-НЕ, выходы второго и пятого элементов И-НЕ соединены с вторыми входами шестого и третьего элементов И-НЕ; соответственно, первые входа первого и четвёртого элементов И-НЕ подключены к шинам соответствующего разряда первого и второго сравниваемых чисел, соответственно, выходы третьего и шестого элементов И-НБ i-и ячейки (i 1 , . , . , п) устройства соединены с вторыми входами пятого и второго элементов И-НЕ (+1)-й ячейки устройства, соответственно, отличающееся тем, что, с целью упрощения устройства, выходы третьего и шестого элементов И-НЕ i-и ячейки устройства соединены с вторыми входами первого и четвертого элементов И-НЕ (1+1)-и ячейки, соответственно.

Источники информаци, принятые во внимание при экспертизе

Авторы

Даты

1981-07-23—Публикация

1979-07-30—Подача