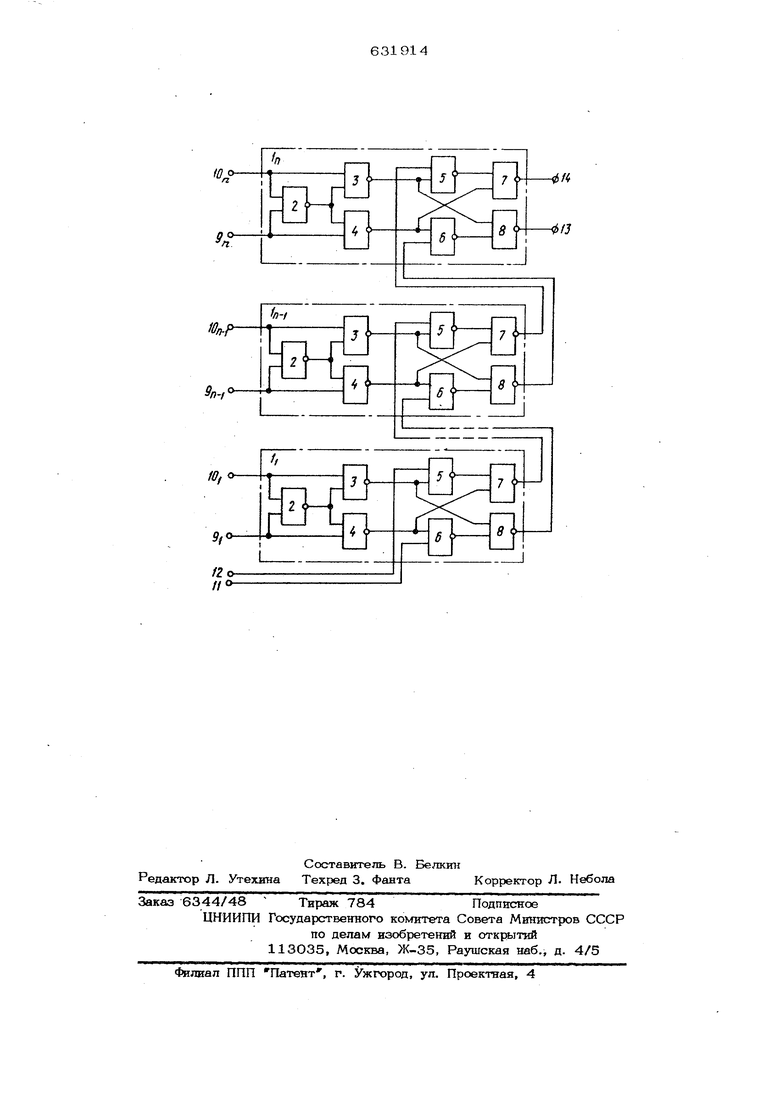

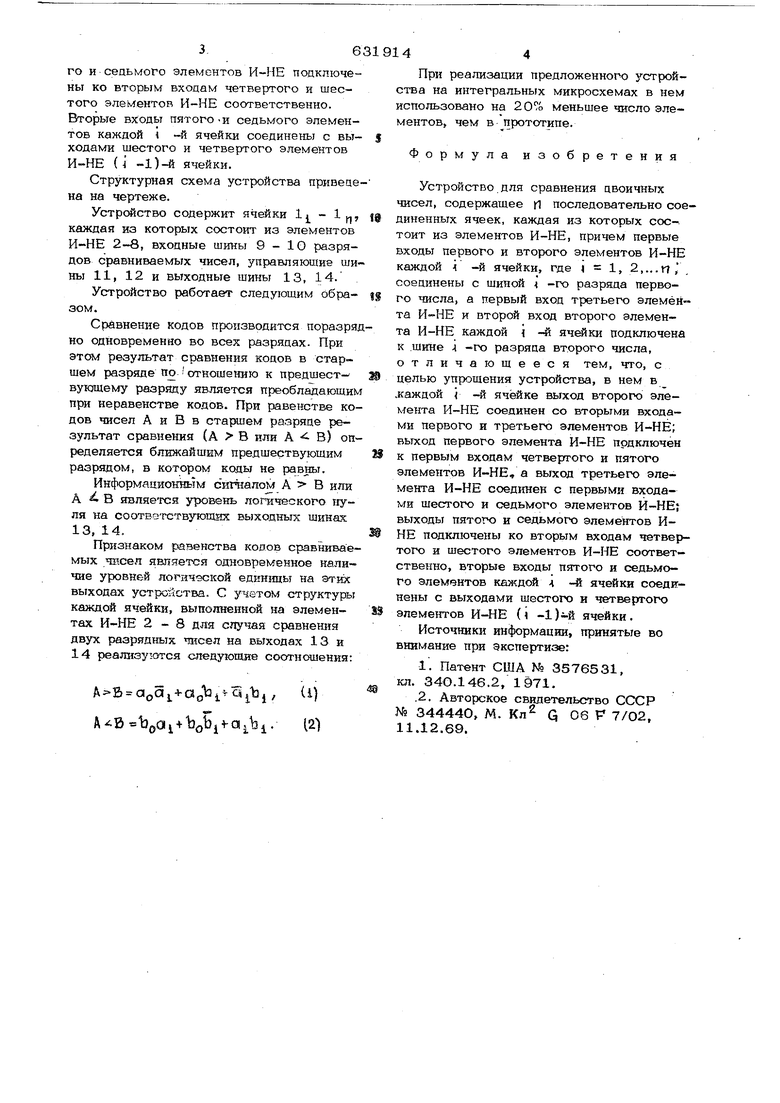

го и-седьмого элементов И-НЕ подключены ко вторым входам четвертого и шестого элементов И-НЕ соответственно. Вторые входы пятого И седьмого эпементов каладой -и ячейки соединены с выходами шестого и четвертого элементов И-НЕ (I -1)-й ячейки. Структурная схема устройства привеае на на чертеже. Устройство содержит ячейки Ij - Ij, каждая из которых состоит из элементов 2-8, входные шины 9 - Ю разрядов сравниваемых чисел, управлягошие шины 11, 12 и выходные шины 13, 14. Устройство работает следуюшим обраСравнение кодов производится поразря но одновременно во всех разрядах. При этом результат сравнения кодов в старшем разряде по отношению к предшест-вующему разряду является преобладающим при неравенстве кодов. При равенстве кодов чисел А и В в старшем разряде результат сравнения (А В или А В) определяется ближайшим предшествующим разрядом, в котором коды не равны. Информациокньш сигаалом А В или А В является уровень логического нуля на соотватствуюпшх выходных шинах 13, 14. Признаком равенства кодов срав1ниваемых чзюел является одновременное наличие уровней логической единицы на этих выходах устройства. С учетом структуры каждой ячейки, выполненной на элементах 2-8 для случая сравнения двух разрядных чисел на выходах 13 и 14 реализузотся следующие соотношения: ac,, (i) ,oii- bobjfa| l3i. (2) 6 44 При реализации предложенного устройства на интегральных микросхемах в нем использовано на 20% меньшее число элементов, чем в прототипе. Формула изобретения Устройство.для сравнения двоичных чисел, содержашее Ц последовательно соединенных ячеек, каждая из которых состоит из элементов И-НЕ, причем первые входы первого и второго элементов И-НЕ каждой k -и ячейки, где 1, 2,...г, соединены с шиной -го разряда перворо тасла, а первый вход третьего элемёнта и второй вход второго элемента И-НЕ каждой { -4 ячейки подключена к шине д -го разряда второго числа, отличающееся тем, что, с целью упрощения устройства, в нем в .каждой -и ячейке выход второго элемента И-НЕ соединен со вторыми входами первого и третьего элементов И-НЁ; выход первого элемента И-НЕ подключен к первым входам четвертого и пятого элементов И-НЕ, а выход третьего элемента И-НЕ соединен с первыми входами шестого и седьмого элементов И-НЕ} выходы пятого и седьмого элементов ИНЕ подключены ко вторым входам четвертого и шестого элементов И-НЕ соответственно, вторые входы пятого и седьмого элементов каждой ч -И ячейки соединены с выходами шестого и четвертого элементов И-НЕ ({ -1)-й ячейки. Источники информации, принятые во внимание при экспертизе: 1. Патент США № 3576531, кл. 34О.146.2, 1971. .2. Авторское свидетельство СССР № 344440, М. Кл Q 06 Р 7/О2, 11.12.69.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сравнения двоичных чисел | 1978 |

|

SU798809A1 |

| Устройство для сравнения двоичных чисел | 1981 |

|

SU1001081A2 |

| Логическая ячейка для ассоциативного запоминающего устройства | 1981 |

|

SU980162A1 |

| Устройство для логарифмирования | 1982 |

|

SU1030800A1 |

| Логическое запоминающее устройство | 1983 |

|

SU1124384A1 |

| Преобразователь двоичного кода в двоично-десятичный код | 1972 |

|

SU532857A1 |

| АССОЦИАТИВНЫЙ ПРОЦЕССОР | 1988 |

|

SU1521118A1 |

| Устройство для сравнения двоичныхчиСЕл | 1979 |

|

SU849204A1 |

| Устройство для сравнения чисел | 1979 |

|

SU920701A1 |

| Устройство для сравнения двух @ -разрядных двоичных чисел | 1989 |

|

SU1640684A1 |

Авторы

Даты

1978-11-05—Публикация

1974-08-23—Подача