Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорных устройствах ЭВМ и в устройствах цифровой автоматики.

Известны сумматоры комбинационно-накапливающего типа, выполненные на основе логических элементов И, ИЛИ, НЕ, содержащие в каждом разряде три RS-триггера, девять элементов И, четыре элемента ИЛИ, один элемент НЕ и три шины управления (см. А.с. №1264165). Недостатком этого сумматора является наличие трех RS-триггеров в каждом разряде, что определяет время выполнения операций сложения, объем оборудования и стоимость устройства в целом. Кроме того, общим недостатком накапливающих и комбинационно-накапливающих сумматоров является сложность схемной реализации совмещения во времени выполнения операций сложения и сдвига кода вправо, что требуется для выполнения операции умножение.

Наиболее близким, принятым за прототип, является сумматор (далее - объект) по а.с. №1291968. Он устраняет некоторые недостатки объекта по А.с. №1264165, т.к. содержит в каждом разряде только один RS-триггер, но не позволяет совмещать операции сложения и сдвига, и выполняет только две операции (сложение и сложение по модулю 2). Целью изобретения является повышение быстродействия работы объекта и расширение перечня выполняемых арифметических и логических операций при минимальных затратах оборудования. Для чего предложен объект, выполненный на основе элементов И, ИЛИ, НЕ, содержащий в каждом разряде один RS-триггер, первую, вторую, третью шины управления и шину поступления информации в данный разряд, причем первый вход первого элемента И подключен к первой шине управления, а второй его вход соединен с шиной поступления информации, выход этого элемента соединен с первым входом первого элемента ИЛИ и с вторым входом третьего элемента ИЛИ, первый вход второго элемента И подключен к второй шине управления, второй его вход связан с шиной переноса из младшего разряда, выход этого элементами соединен с третьим входом первого элемента ИЛИ, выход которого подключен к первым входам третьего и четвертого элементов И, третий вход третьего элемента И соединен с выходом пятого элемента И, первым входом третьего элемента ИЛИ и с входом первого элемента НЕ, выход которого подключен к второму входу четвертого элемента И; выход третьего элемента И подключен к R-входу триггера, к первому входу второго элемента ИЛИ и к второму входу четвертого элемента ИЛИ; выход четвертого элемента И подключен к S-входу триггера и к входу второго элемента НЕ, выход которого соединен с первым входом пятого элемента И; единичный выход триггера соединен с вторым входом второго элемента ИЛИ, выход которого связан с вторым входом пятого элемента И; первый вход четвертого элемента ИЛИ соединен с шиной переноса из младшего разряда, третьи входы третьего и четвертого элементов ИЛИ связаны с выходом шестого элемента И данного разряда, выходы упомянутых элементов ИЛИ подключены первому и третьему входам шестого элемента И, к второму входу этого элемента подключена третья шина управления, а выход шестого элемента И является шиной переноса в старший разряд, ОТЛИЧАЮЩИЙСЯ тем, что в каждый разряд сумматора введены седьмой и восьмой элементы И, пятый и шестой элемент ИЛИ, третий и четвертый элементы НЕ, пятая, шестая и седьмая шины управления, при этом выход шестого элемента И соединен с первым входом восьмого элемента И и с входом третьего элемента НЕ, выход которого связан первым входом седьмого элемента И, вторые входы упомянутых элементов И соединены с входом и выходом первого элемента НЕ старшего разряда соответственно, выходы седьмого и восьмого элементов И подключены к первому и третьему входам пятого элемента ИЛИ, к его второму входу подключена шестая шина управления, а выход этого элемента ИЛИ соединен с первым входом четвертого элемента И и с входом четвертого элемента НЕ, выход которого подключен к первому входу шестого элемента ИЛИ, второй вход упомянутого элемента соединен с седьмой шиной управления, выход шестого элемента ИЛИ подключен к третьему входу третьего элемента И, кроме того, пятая шина управления соединена с третьим входом первого элемента ИЛИ, а выход третьего элемента И соединен с первым входом девятого элемента И, второй вход которого связан с вторым входом третьего элемента ИЛИ; кроме того, введена восьмая шина управления, которая подключена к третьему входу второго элемента ИЛИ каждого разряда, а в каждый разряд введен пятый элемент НЕ, вход которого подключен к выходу третьего элемента И, а выход связан с R-входом первого триггера, при этом выход второго элемента НЕ соединен с S-входом триггера. Предлагаемый объект позволяет повысить быстродействие выполнения операции умножения за счет совмещения во времени операций сложения и сдвига кода, обеспечивает широкий перечень выполняемых арифметических и логический операций (сложение, сложение со сдвигом вправо, инвертирование, сдвиг кода вправо, сложение по модулю 2, сдвиг кода влево, логическое сложение, а также логическое умножение, обеспечивает повышение надежности работы и снижение потребления электроэнергии).

Отметим основные отличительные признаки объекта и покажем, что позволяет получить каждый из них.

1. Введение в состав оборудования каждого разряда третьего элемента НЕ, седьмого и восьмого элементов И, пятого и шестого элементов ИЛИ и связей этих элементов с шиной переноса из данного разряда позволяет реализовать логическое соотношение:

1/2Si=Pi* i-1+

i-1+ i*Ai-1.

i*Ai-1.

2. Четвертый логический элемент НЕ и связи выхода пятого элемента ИЛИ со вторым входом четвертого элемента И, а также связь выхода упомянутого элемента НЕ через шестой элемент ИЛИ с вторым входом третьего элемента ИЛИ позволяют принять в триггер i-го разряда парафазным кодом значение результата суммирования двух чисел с сдвигом его на один разряд вправо. Эти же элементы обеспечивают сдвиг кода, хранящегося в триггерах 1, на один разряд вправо при гашении сигнала переноса (шина 3) и поступлении на пятую управляющую шину исполнительного импульса.

3. Пятая, шестая и седьмая шины управления и шестой логический элемент ИЛИ обеспечивают выполнение операций инвертирования, сдвига кода влево, сложения по модулю два и логического сложения (п.1 формулы изобретения).

4. Восьмая шина управления обеспечивает выполнение операции логического умножения (п.2 формулы изобретения).

5. Пятый элемент НЕ и связь с выхода второго элемента НЕ с R-входом триггера и первым входом пятого элемента И обеспечивают исключение возможных «гонок» сигналов в цепи «пятый элемент И, вход первого элемента НЕ», т.е. повышает надежность работы объекта (п.3 формулы изобретения).

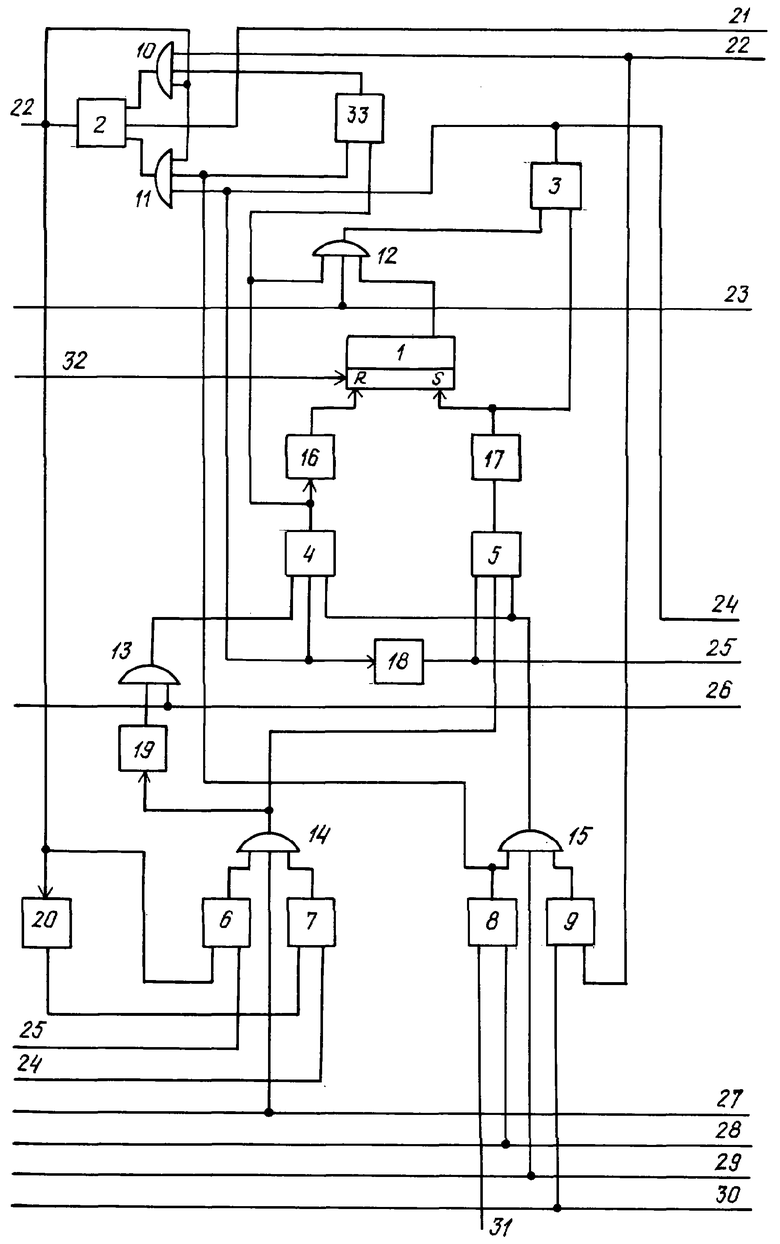

Для пояснения принципа работы описываемого объекта на фиг.1 приведена функциональная схема одного двоичного разряда предлагаемого объекта.

Каждый двоичный разряд объекта содержит RS-триггер 1, элементы И 2-9,33, элементы ИЛИ 10-15, элементы НЕ 16-20, шины управления 21, 23, 26-30, шину поступления информации 31, шину переноса 22, шину установки нуля RS-триггера 32.

Рассмотрим работу объекта при выполнении арифметических и логических операций. Будем считать, что до начала выполнения операций на шинах управления (ШУ) 21, 23, 26-32 отсутствуют управляющие потенциалы (импульсы).

1. Операция сложения. Полагаем, что в триггерах 1 хранится первое слагаемое как результат выполнения предыдущей операции. На время выполнения операции на ШУ 21, 26 и 27 подаются управляющие потенциалы, которые сохраняются на время выполнения всей операции (t1, t2, и t3 - временные такты выполнения операции).

По первому временному такту (t1) на ШУ 28 подается импульс приема второго слагаемого и выполнение первого сложения по модулю два. Если на шине 31 присутствует высокий потенциал, соответствующий коду «единица», то исполнительный импульс по цепи И 8, ИЛИ 15 поступит на первые входы И 4, 5. Если до прихода импульса в триггере 1 хранился код «0», то сигнал через И 5, НЕ 17 поступит на S-вход триггера и установит его в «единицу». Если до прихода импульса в триггере хранился код «1», то сигнал по цепи И 4, НЕ 16 поступит на R-вход триггера и установит его в «0». При переключении триггера из «0» в «1» низкий потенциал с выхода НЕ 17 запретит прохождение сигнала через И 3, т.е. обеспечит «задержку» появления сигнала на входе НЕ 18, что соответствует задержке во времени переключению триггера 1. При переключении триггера из «1» в «0» сигнал с выхода И 4 поступает на вход ИЛИ 12, И 3 и будет поддерживать высокий потенциал с выхода И 3, что соответствует «задержке» переключения триггера из «1» в «0». Одновременно сигнал с выхода И 4 поступит на первый вход И 33, второй вход этого элемента соединен со вторым входом ИЛИ 11, а выход И 33 соединен со вторым входом ИЛИ 10 и совместно с сигналом, поступившим с выхода И 8 на второй вход ИЛИ 11, выработают потенциал переноса с выхода И 2 в старший разряд. При этом выработанный потенциал будет храниться в течении t1, 2, 3, на элементах ИЛИ 10, 11, И 2, за счет обратной связи с выхода И 2 на третьи входы упомянутых элементов ИЛИ. Таким образом, выполняется первое сложение по модулю два и формирование переноса в рассматриваемом разряде.

По t2 производится распространение сквозного переноса через все разряды объекта. Если на шину 22 поступил потенциал переноса из младшего разряда, а в рассматриваемом разряде хранится код «1», то на выходе И 2 будет сформирован потенциал переноса в старший разряд.

По t3 выполняется второе сложение по модулю два. После завершения распространения максимального сквозного переноса на ШУ 30 подается исполнительный импульс. Если из младшего разряда по шине 22 поступил высокий потенциал, то импульс по цепи И 9, ИЛИ 15 поступит на первые входы И 4, 5 и выполнит инвертирование триггера 1, т.е. сформирует в триггерах объекта результат сложения двух двоичных чисел. На этом собственно операция сложения закончена, но для подготовки объекта к выполнению последующих арифметических и логических операций необходимо погасить хранящиеся в цепях переносов потенциалы.

По t4 производится элементарная операция (ЭО) гашения сигналов переноса. Для этого с ШУ 21 снимается высокий потенциал, за счет чего потенциалы переносов будут погашены во всех разрядах объекта. Одновременно с ШУ 26 и 27 снимаются высокие потенциалы.

2. Операция сложения с одновременным сдвигом результата вправо. Операция выполняется за четыре временных такта, включая гашение потенциалов переноса.

По t1 выполняется ЭО первого сложения по модулю два (детально рассмотрена при описании предыдущей операции).

По t2 продолжается формирование и распространение потенциала переноса. Одновременно снимаются высокие потенциалы с ШУ 26, 27. К моменту завершения максимального сквозного переноса, равного 2n τ (n - число разрядов, τ - временная задержка сигнала на одном ЛЭ И (ИЛИ)), на выходе ИЛИ 14 будет сформирован результат суммирования первого (Ai-1) и второго слагаемых (Bi-1) с одновременным сдвигом на один разряд вправо.

По t3 для занесения результата суммы в триггеры 1 на ШУ 29 подается исполнительный импульс, который по цепи ИЛИ 15, И 4,5 поступит на один из установочных входов триггера 1.

По t4 производится гашение потенциалов переносов и подготовка объекта к выполнению следующей операции сложения с одновременным сдвигом, т.е. на ПТУ 26, 27 подаются высокие управляющие потенциалы.

3. Операция сдвига кода вправо. Для выполнения этой операции с ШУ 21 снимается высокий потенциал, который сохраняется на время всей операции. В i-том разряде высокий потенциал с НЕ 20 поступает на первый вход И 7. На второй вход этого элемента поступает высокий потенциал с выхода И З i+1-го разряда, что соответствует значению кода «единицы», хранящемуся в старшем разряде. Высокий потенциал с выхода И 7 через ИЛИ 14 поступает на третий вход И 5. Этот же потенциал по цепи НЕ 19, ИЛИ 13 запрещает работу И 4. Для осуществления сдвига кода на ШУ 29 подается исполнительный импульс, который через ИЛИ 15, И 5, НЕ 17 поступит на S-вход триггера. Если в триггере старшего разряда до поступления импульса сдвига хранился код «нуля», то триггер i - того разряда будет установлен «нуль». Таким образом, код, хранящийся в триггерах 1, будет сдвигаться вправо на один разряд после поступления на ШУ 29 импульса сдвига.

4. Операция сдвига кода влево. Для выполнения требуется четыре временных такта для сдвига на каждый двоичный разряд. Для выполнения сдвига кода влево (нормализация, умножение на 2, 4, 8 т.д.) на ШУ 21, 26 и 27 подаются управляющие потенциалы, которые сохраняются в течении длительности всей операции (t1, 2, 3).

По t1 на ШУ 29 поступает исполнительный импульс, который по цепи ИЛИ 15, И 4, НЕ 16 проходит на R-вход триггеров 1 в тех разрядах объекта, в которых хранится код «единицы». Одновременно этот же импульс с выхода И 4, через И 33, ИЛИ 10 поступит на первый вход И 2. Потенциал с «единичного» выхода триггера 1 по цепи ИЛИ 12, И 3, ИЛИ 11 поступает на третий вход И 2. Потенциал с выхода И 2 является сигналом переноса в старший разряд и за счет обратной связи с входами элементов ИЛИ 10, 11 будет «хранить» этот сигнал до момента снятия высокого потенциала с ШУ 21 (t4).

По t2 триггеры во всех разрядах объекта, за счет подачи импульса на ШУ 32, устанавливаются в «нуль».

По t3 на ШУ 30 подается исполнительный импульс, который, в случае прихода потенциала переноса по шине 22, проходит по цепи И 9, ИЛИ 15, И 5 на S-вход триггера 1.

По t4 выполняется элементарная операция гашения переносов во всех разрядах объекта за счет снятия высокого потенциала с шины 21. Таким образом, выполняется сдвиг кода на один разряд влево. Заметим, что для выполнения этой операции не требуется дополнительного оборудования.

5. Операция инвертирования кода. Эта операция выполняется за один временной такт. Для ее выполнения на ШУ 26, 27 подаются высокие потенциалы, а на ШУ 29 - исполнительный импульс, который по цепи ИЛИ 15, И 5, 6 поступит на один из входов триггера 1 и произведет инвертирование кодов во всех разрядах.

6. Операция логического сложения. Операция выполняется за один временной такт. Для ее выполнения на ШУ 27 подается высокий потенциал, который разрешает прохождение исполнительного импульса через И 5, поступающего по цепи ШУ 28, ИЛИ 15, если в данном разряде на шине 31 присутствует высокий потенциал, соответствующий «единице» второго слагаемого.

7. Операция логического умножения. Операция выполняется за один временной такт. Первый сомножитель хранится в триггерах 1, второй - принимается с шины 31 в инверсном коде. Для выполнения операции на ШУ 23, 26 подается высокий потенциал, за счет чего на третьем и втором входах И 4 во всех разрядах будет присутствовать потенциал, разрешающий прохождение исполнительного импульса через И8, ИЛИ 15, И 4, НЕ 16 на R-вход триггера 1. Операция закончена.

Основные технические характеристики предлагаемого объекта по сравнению с прототипом и канонической схемой построения комбинационных сумматоров приведены в таблице 1.

Из таблицы видно, что предложенный объект выполняет в 2,5 раза операций больше, чем прототип, и в 2 раза больше, чем сумматор комбинационного типа. По быстродействию выполнения базовых операций объект в 1,5 раза превосходит прототип и имеет одинаковое быстродействие с сумматором комбинационного типа при оптимальном соотношении временных параметров сравниваемых устройств. Оптимальными временными параметрами в данном случае являются: tи=tn; tи=t1=t2=t3=t4;

Т пер.max.=2n τ=2 tи;

здесь: tи - длительность тактового (исполнительного) импульса; tn - длительность паузы; Т пер.max - максимальная задержка сигнала в цепи переносов; n - число разрядов; τ - временная задержка сигнала на одном элементе И (ИЛИ).

Таким образом, предлагаемый объект позволяет повысить быстродействие выполнения операций по сравнению с прототипом, расширить перечень выполняемых операций и снизить аппаратурные затраты по сравнению с известными сумматорами. Кроме того, имеет место снижение электропотребления приблизительно в 1,5-2 раза за счет сокращения RS-триггеров в каждом разряде.

| название | год | авторы | номер документа |

|---|---|---|---|

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2262735C1 |

| СУММИРУЮЩЕЕ УСТРОЙСТВО | 2004 |

|

RU2264646C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2269153C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2003 |

|

RU2261469C1 |

| КОМБИНАЦИОННО-НАКАПЛИВАЮЩИЙ СУММАТОР | 2006 |

|

RU2306596C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2006 |

|

RU2308801C1 |

| СЧЕТЧИК ИМПУЛЬСОВ | 2005 |

|

RU2284654C2 |

| СУММАТОР НАКАПЛИВАЮЩЕГО ТИПА | 2004 |

|

RU2278411C1 |

| РЕВЕРСИВНЫЙ РЕГИСТР СДВИГА ВЛАСОВА | 2006 |

|

RU2309536C1 |

| Арифметическое устройство | 1979 |

|

SU842794A1 |

Изобретение относится к области цифровой вычислительной техники и может быть использовано в процессорах ЭВМ и в устройствах цифровой автоматики. Техническим результатом является повышение быстродействия, расширение перечня выполняемых операций, повышение надежности работы и снижение потребления электроэнергии при минимальных аппаратурных затратах. Сумматор содержит в каждом разряде один RS-триггер, девять логических элементов И, шесть элементов ИЛИ, пять элементов НЕ и восемь шин управления. 1 з.п. ф-лы, 1 ил., 1 табл.

| Накапливающий сумматор | 1985 |

|

SU1291968A1 |

| ЦИФРОВОЙ СУММАТОР | 1994 |

|

RU2099776C1 |

| НАКАПЛИВАЮЩИЙ СУММАТОР | 1993 |

|

RU2043650C1 |

| Накапливающий сумматор | 1985 |

|

SU1264165A1 |

| US 5691931 A, 25.11.1995 | |||

| 1972 |

|

SU416869A1 | |

Авторы

Даты

2005-10-20—Публикация

2004-03-29—Подача