(54) УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИ1

-----«m J

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для сопряжения ЭВМ с внешним устройством | 1985 |

|

SU1315988A1 |

| Устройство для сопряжения ЭВМ с внешними устройствами | 1985 |

|

SU1288709A1 |

| Устройство для сопряжения электронно-вычислительной машины с группой внешних устройств | 1985 |

|

SU1278866A1 |

| Устройство для сопряжения двух электронных вычислительных машин | 1983 |

|

SU1141418A1 |

| Устройство для обмена информацией между ЭВМ и внешней памятью | 1989 |

|

SU1714613A1 |

| Устройство для сопряжения ЭВМ с магистралью локальной сети | 1990 |

|

SU1839258A1 |

| Устройство для сопряжения ЭВМ с абонентом | 1986 |

|

SU1334154A1 |

| АДАПТЕР КАНАЛ - КАНАЛ | 1991 |

|

RU2024050C1 |

| Автоматизированная система контроля радиоэлектронных устройств | 1989 |

|

SU1683038A1 |

| Устройство для сопряжения однородной вычислительной системы | 1979 |

|

SU903848A2 |

Изобретение относится к вычислительной технике и может быть использовано для сопряжения управляющей микро-ЭВМ с системой приводов и датчиков манипулятора, а также с технологическим оборудованием, обслуживаемым роботом. Известны устройства для сопряжения внешнего оборудования с шиноймикро-ЭВМ ClJ. Недостатком таких устройств является низкая производительность обору дования, обусловленная жесткой после довательностью обмена для одних устройств, а для-других наличием дополнительного оборудования, необходимого для обеспечения последовательности обмена. Наиболее близким по технической сущности к предлагаемому является устройство параллельного обмена, содержащее блок канальных приемопередатчиков, дешифратор адреса, выходной буферный регистр, мультиплексор данных, регистр состояния, дешифрато управляквдих сигналов, логику прерыва ния и блок адреса вектора. Причем вы ход блока приемопередатчиков соедине с внутренней шиной данньгх, информаци с которой поступает на. входы дешифратора адреса, выходного буферного регистра, дешифратора управляквдих сигналов и регистра состояния, входы блока канальных приемопередатчиков соединены с выходом мультиплексора данных, выходом.дешифратора управляющих сигналов и выходом логики прерывания, входы-выходы канальных приемопередатчиков соединены со входо-выходной шиной микро-ЭВМ, выход выходного буферного регистра соединен с выходной шиной данных внешних устройств и входом мультиплексора данных, а второй его вход соединен с выходом дешифратора управляющих сигнешов, входы мультиплексора данных соединены с блоком адреса вектора и выходом регистра состояния, вход дешифратора управляющих сигналов соединен с выходом дешифратора гццреса, выход его соединен с мультиплексором данных, вход-выход его соединение управляющими линиями входной-выходной шины микро-ЭВМ, логика прерывания соединена входом с регистром состояния, выходом - с блоком канальных приемопередатчиков и мультиплексором данных, а входы-выходы с управляющими линиями входной-выходной шиной микро-ЭВМ и.

Недостаток такого устройства заключается в низкой производительности оборудования, обусловленной тем, что данное устройство обеспечивает обслуживание только одного источника и одного приемника информации. Кроме того, затруднено обслуживание источника информации, требующего значительного времени на подготовку информации по запросу от ЭВМ.

Цель изобретения - повьпиение производительности устройства для сопряжения микро-ЭВМ с манипулятором и т.вхнологическим оборудованием.

Поставленная цель достигается тем что в устройство для обмена информацией, содержащее первый и второй блоки ,сопряжения, дешифратор адреса, мультиплексор данных, регистр адреса вектора, выходной буферный регистр, первый дешифратор управляющих сигналов, регистр состояний, причем первы вход-выход устройства соединен с первым входом-выходом первого блока сопряжения, второй вход-выход устройства соединен с первыми .входами-.дыходами дешифратора адреса и первого дешифратора управляющих сигналов, третий вход-выход устройства соединен с первым входом-выходом второго блока сопряжения, второй вход которого подключен к первому выходу регистра состояний, а второй выход - к первому входу мультиплексора данных и ко второму входу первого блока сопряжения, второй выход которого соединен с первым входом выходного буферного регистра, с первым входом регистра состояний и со вторым входом пер- вого дешифратора управляющих сигналов и дешифратора адреса, третий вход подключен ко второму выходу первого дешифратора управляющих сигналов , а четвертый вход - к выходу мультиплексора данных., второй, тре тий и четвертый входы которого подключены соответственно к выходу регистра адреса вектора, ко второму выходу регистра состояний и к третьему выходу первого дешифратора управляющих сигналов, третий вход которого подключен к выходу дешифратора адреса, четвертый и пятый выходы соединены соответственно с четвертым выходом устройства и со вторым входом выходного буферного регистра, выход которого подключен к пятому выходу устройства и к пятому входу мультиплексора данных, дополнительно введены входной буферный регистр, регистр прерываний, дешифратор направления ввода, второй дешифратор управляквдих сигналов и регистр команды ввода, первые вход и выход которого соединены с первым выходом и входом второго дешифратора управляющих сигналов соответственно, второй и трети входы подключены соответственно ко второму выходу первого блока сопряженин и к шестому выходу первого дешифратора управляющих сигналов, втор выход регистра команды ввода соедине с первым входом дешифратора направления ввода, выход которого является шестым выходом устройства, а второй вход подключен ко второму выходу второго дешифратора управляющих сигналов, второй и третий входы которого подключены соответственно к -седьмому выходу первого дешифратора управляющ сигналов и к первому выходу регистра прерываний, а третий, четвертый и пятый выходы соединены соответственно третьим входом второго блока сопряжения и со вторым входом регистра состояний, со входом регистра адреса вектора, с первым входом входного буферного регистра, выход которого соединен с шестым входом мультиплексора данных, второй, третий входы входного буферного регистра подключены соответственно ко второму выходу регистра прерываний и седьмому входу устройства, восьмой вход устройства подключен ко входу регистра прерываний и к четвертому входу второго дешифратора управляющих сигналов.

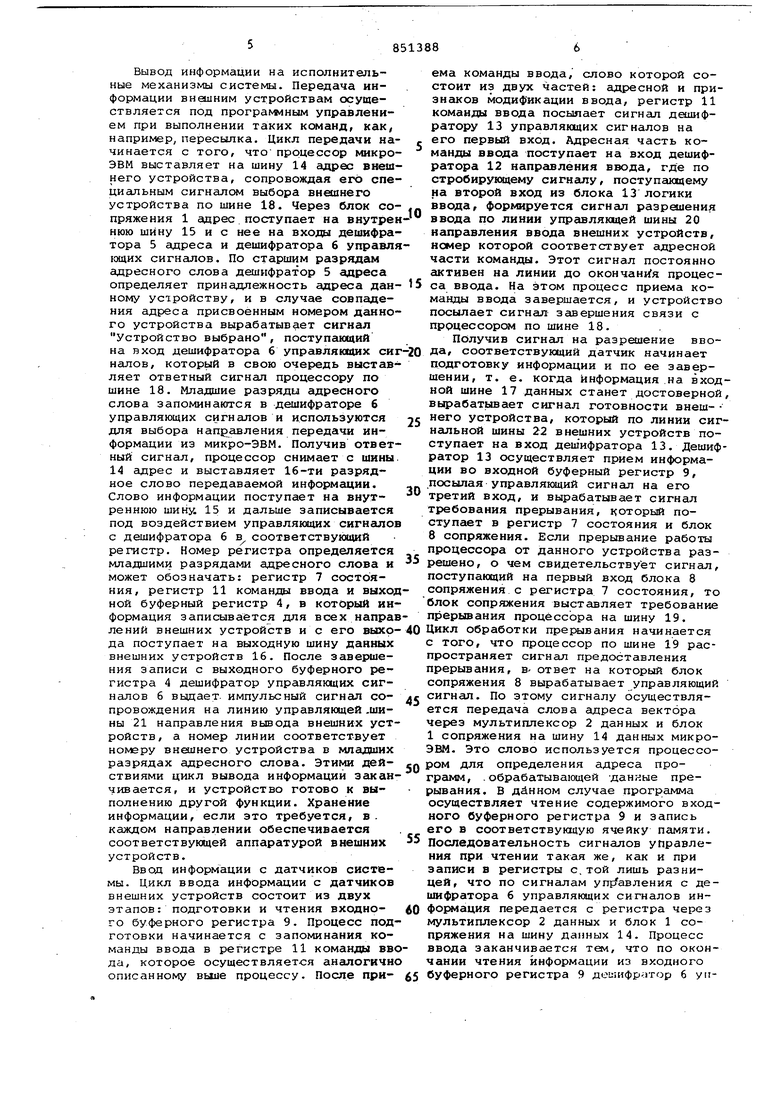

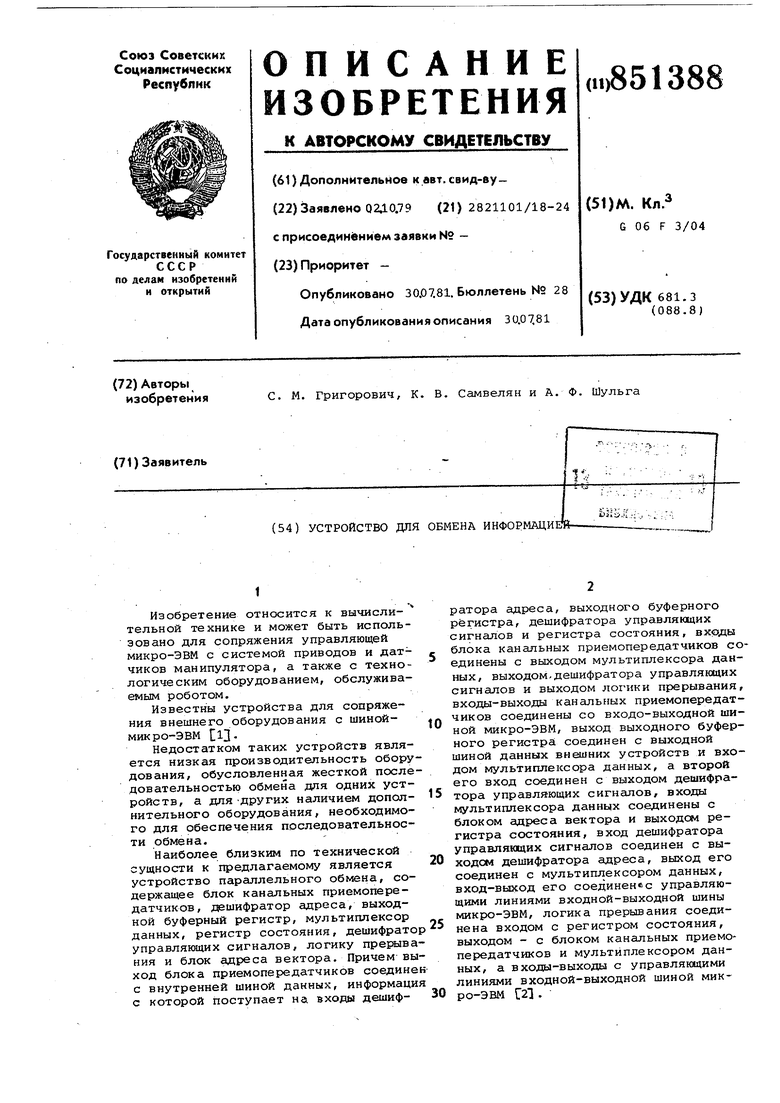

На чертеже приведена структурная схема устройства для обмена информацией .

Устройство содержит первый блок 1 сопряжения, мультиплексор 2 данных, регистр 3 адреса вектора, выходной буферный регистр 4, дешифратор 5 адреса, первый дешифратор 6 управляющих сигналов, регистр 7 состояния, второй блок 8 сопряжения,входной буферный регистр 9, регистр 10 прерываний, регистр 11 команды ввода, дешифратор 12 направления ввода, второй дешифратор 13 управляющих сигналов .

На чертеже обозначены также шины устройства: шина 14 - линии данных входной-выходной шины микро-ЭВМ; шина 15 - внутренняя шина данных шина 16 - выходная шина данных внешних устройств-, шина 17 - входная шина данных внешних устройств; шина 18 управляющие линии входной-выходной шины микро-ЭВМ; шина 19 - управляющие линии прерываний входно-выходной шины микро-ЭВМ; шина 20 - управляющая шина направления ввода внешних устройств; шина 21 - управляклцая шина направления вывода внешних устройствшина 22 - сигнальная шина внешних устройств.

В системе управления манипулятором и технологическим оборудованием устройство выполняет следующие функции: вывод информации на исполнительные механизмы системы ввод информации с датчиков системы; обработка прерываний внешних устройств.

Рассмотрим последовательно выполнение отдельных функции системы. Вывод информации на исполнительные механизмы системы. Передача информации внешним устройствам осуществляется под программным управлением при выполнении таких ко1анд, как, например, пересылка. Цикл передачи начинается с того, чтопроцессор микроЭВМ выставляет на шину 14 адрес внешнего устройства, сопровождая его специальным сигналом выбора вноинего устройства по шине 18. Через блок сопряжения 1 адрес поступает на внутрен нюю шину 15 и с нее на входы дешифратора 5 адреса и дешифратора б управля ющих сигнсшов. По старшим разрядам адресного слова дешифратор 5 адреса определяет принадлежность адреса данному устройству, и в случае совпадения адреса присвоенным номером данного устройства вырабатывает сигнал Устройство выбрано, поступгиоций на вход дешифратора 6 управляющих сиг налов, который в свою очередь выставляет ответный сигнал процессору по шине 18. Младшие разряди адресного слова запоминаются в дешифраторе 6 управляющих сигналов и используются для выбора направления передачи информации из микро-ЭВМ. Получив ответный сигнал, процессор снимает с шины 14 адрес и выставляет 16-ти разрядное слово передаваемой информации. Слово информации поступает на внутреннюю шину. 15 и дальше записывается под воздействием управляющих сигналов с дешифратора 6 в соответствующий регистр. Номер регистра определяется младшими разрядами адресного слова и может обозначать: регистр 7 состояния, регистр 11 команды ввода и выход ной буферный регистр 4, в который информация записывается для всех направ лений внешних устройств и с его выхода поступает на выходную шину данных внешних устройств 16. После завершения записи с выходного буферного регистра 4 дешифратор управляющих сигналов 6 вьщает. импульсный сигнгш сопровождения на линию управляющей.шины 21 направления вывода внешних устройств, а номер линии соответствует HONepy вноинего устройства в мпсшших разрядах адресного слова. Этими действиями цикл вывода информации закан чивается, и устройство готово к выполнению другой функции. Хранение информации, если это требуется, в. каждом направлении обеспечивается соответствующей аппаратурой внешних устройств. Ввод информации с датчиков системы. Цикл ввода информации с датчиков внешних устройств состоит из двух этапов: подготовки и чтения входного буферного регистра 9. Процесс под готовки начинается с запоминания команды ввода в регистре 11 команды вв ла, которое осуществляется аналогичн описанному выие процессу. После приема команды ввода, слово которой состоит из двух частей: адресной и признаков модификации ввода, регистр 11 команды ввода посылает сигнал дешифратору 13 управляющих сигналов на его первый вход. Адресная часть команды ввода поступает на вход дешифратора 12 направления ввода, где по стробирующему сигналу, поступакадему на второй вход из блока 13 логики ввода, формируется сигнал разрешения ввода по линии управлягацей шины 20 направления ввода внешних устройств, номер которой соответствует адресной части команды. Этот сигнал постоянно активен на линии до окончания процесса ввода. На этом процесс приема команды ввода завершается, и устройство посылает сигнал завершения связи с процессором по шине 18. Получив сигнсш на разрешение ввода, соответствующий датчик начинает подготовку информации и по ее завершении, т. е. когда информация на входной шине 17 данных станет достоверной, вырабатывает сигнал готовности внеш- него устройства, который по линии сигнальной шины 22 внешних устройств поступает на вход дешифратора 13. Дешифратор 13 осуществляет прием информации во входной буферный регистр 9, .посылая управлякщий сигнал на его третий вход, и вырабатывает сигнал требования прерывания, который поступает в регистр 7 состояния и блок 8 сопряжения. Если прерывание работы процессора от данного устройства разрешено, о чем свидетельствует сигнал, поступающий на первый вход блока 8 сопряжения с регистра 7 состояния, то блок сопряжения выставляет требование прерывания процессора на шину 19. Цикл обработки прерывания начинается с того, что процессор по шине 19 распространяет сигнал предоставления прерывания, в- ответ на который блок сопряжения 8 вырабатывает управляющий сигнал. По этому сигналу осуществляется передача слова адреса вектора через мультиплексор 2 данных и блок 1 сопряжения на шину 14 данных микроЭВМ. Это слово используется процессором для определения адреса программ, .обрабатывающей -данные прерывания. Б данном случае программа осуществляет чтение содержимого входного буферного регистра 9 и запись его в соответствукщую ячейку памяти, Последовательность сигналов управления при чтении такая же, как и при записи в регистры с,той лишь разницей, что по сигналам упрГавления с дешифратора 6 управляклцих сигналов информация передается с регистра через мультиплексор 2 данных и блок 1 сопряжения на шину данных 14. Процесс ввода заканчивается тем, что по окончании чтения информации из входного буферного регистра 9 дешифр ггор 6 уиравляющих сигналов вырабатывает сигнал, поступанщий на четвертый вход дешифратора 13, по этому сигналу дешифратор 13 переходит в исходное состояние и сбрасывает регистр 11 команды ввода. Обработка прерываний от внешних устройств. Сигналы прерывания от каж дого Исшравления поступают по отдель ной линии сигнальной шины 22 внешних устройств в устройство и записываютс в регистр 10 прерывания, каждый в свой бит регистра. Если возбужден хо тя бы один бит, регистр 10 прерывани вырабатывает сигнал, поступаняций на второй вход дешифратора 13. Доиифратор 13 анализирует состояние регистр 11 команды ввода и если он обнулен, т. е. завершено выполнение предыдуще команды ввода, вырабатывает сигналы модификации вектора прерываний, поступающий на вход регистра 3 адреса вектора, переписи .информации из регистра 10 прерываний во входной буферный регистр 9 и требования пре рывания, который как и в случае программного ввода поступает на входы регистра 7 состояния и блока 8 сопря жения. Дальше процесс идет описанным вьше способом, но программа обработки прерывания будет другой. В её фун ции должно входить чтение информации из входного буферного регистра 9, распознавание номера направления, вызвавшего прерывание, а затем переход к той части обработки, которая полностью зависит от выполняемой задачи управления. система управления, построенная с применением предлагаемого устройст ва, предназначена для управления про1 ышленными роботами и свггзанным с ними технологическим оборудованием, характеризукнцимзя наличием большого количества приемников и датчиков ин формации относительно простого устройства, таких как контакты реле, отдельные резисторы и т. п.; нерегулярностью потока сообщений в процессе управления-, малым требуемым временем реакции системы на из fiняю цyюся информацию; сопоставимыми временами передачи и обработки информации Применение предлагаемого устройст ва позволяет пввысить производительность системы за счет улучшения соотнсяиения времени использования процессора для, обработки и передачи информации, улучшения коэффициента использования оборудования. Кроме того оно позволяет сократить время реакци и увеличить гибкость системы. Формула изобретения Устройство для обмена информацией содержащее первый и второй блоки сопряжения, дешифратор адреса, мультиплексор данных, регистр адреса вектора, выходной буферный регистр, первый дешифратор управляющих сигналов, регистр состояний, причем первый входвыход устройства соединен с первым входом-выходом первого блока сопряжения, второй вход-выход устройства соединен с первыми входами-выходами дешифратора адреса и первого дешифратора управляющих сигналов, третий вход-выход устройства соединен с рервым входом-выходом второго блока сопряжения, второй вход которого подключен к первому выходу регистра состояний, а второй выход - к первому входу мультиплексора данных и ко второму входу первого блока сопряжения, второй йыход которого соединен с первым входом выходного буферного регистра, с первым входом регистра состояний и со вторым входом первого дешифратора управляющих сигналов и дешифратора адреса, третий вход первого блока сопряжения подключен ко второму выходу первого дешифратора,управлякщих сигналов, а четвертый входк выходу мультиплексора данных, второй, третий и четвертый входы которого подключены соответственно к выходу регистра адреса вектора, ко второму выходу регистра состояний н к третьему выходу первого дешифратора управляюидах сигналов, третий вход которого подключен к выходу дешифратора адреса, а четвертый и пятый выходы соединены соответственно с четвертым выходом устройства и со вторым входом выходного буферного регистра , выход которого подключен к пятому выходу устройства и к пятому входу мультиплексора данных, о т л и ч а ю щ е е с я тон, что, с целью повышения производительности устройства, в него введены входной буферный регистр, регистр прерываний, дешифратор направления ввода, второй дешифратор управляющих сигналов и регистр команды ввода, первые вход и .выход которого соединены с первыми выходом и входом второго дешифратора управляющих сигналов соответственно, а второй .и третий входы регистра команды ввода подключены соответственно ко второму выходу первого блока сопряжения и к шестому выходу первого дешифратора управляющих сигналов/ второй выход регистра команды ввода соединен -с первым входом дешифратора направления ввода, выход которого является шестым выходом устройства, а второй вход подключен ко второму выходу второго дешифратора управляющих сигналов, второй и третий входы которого подключены соответственно к седьмому выходу первого дешифратора управляющих сигналов и к первому выходу регистра прерываний, а третий, четвертый и пятый выходы дешифратора управляющих сигналов cociinneHH соот- г

ветственно с третьим входом второго блока сопряжения и со ьторым входом регистра состояний, со входом р.егист.ра адреса вектора, с первым входом входного буферного регистра, выход которого соединен с шестым входом мультиплексора данных, а второй и третий входы входного буферного регистра подключены соответственно ко второму выходу регистра прерываний и к седьмому входу, устройства, восьмой вход устройства подключен ко входу

регистра прерываний и к четвертому входу второго даиифратора управляющих сигналов. Источники информации, с принятые во внимание при экспертизе

(прототип).

Авторы

Даты

1981-07-30—Публикация

1979-10-02—Подача