5

Изобретение относится к управляющим системам с программным управлением и может быть использовано для логического управления технологи- ческим оборудованием.

Цель изобретения - расширение функциональных возможностей и области применения программируемого контроллера.IQ

Введение в программируемый конт- ;роллер второго мультиплексора, блока вычисления временных булевых Фзшкций, блока задания кодов адреса, коммутатора, компаратора и дисплея позволя- js ет осуществлять визуальный контроль текущего значения логических переменных в любой точке исполняемой программы, выполнять любые типы булевых функций, включая времязависимые и, 20 тем самым достичь значительного расширения функциональных возможностей программируемого контроллера.

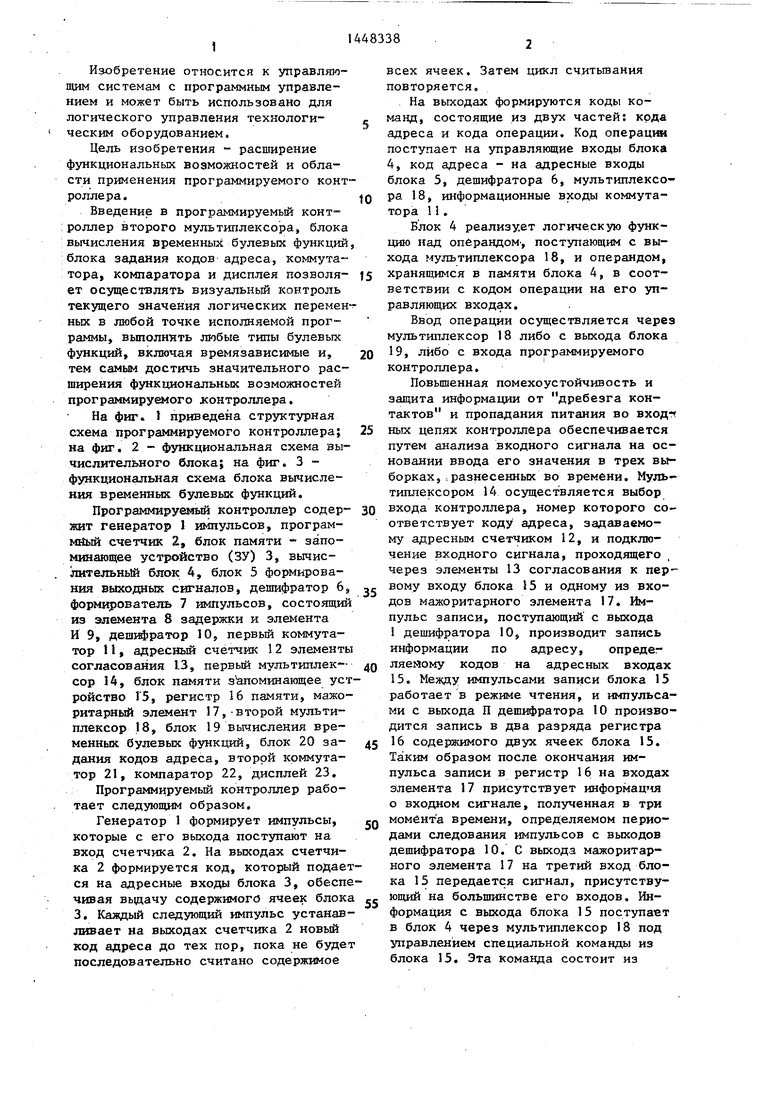

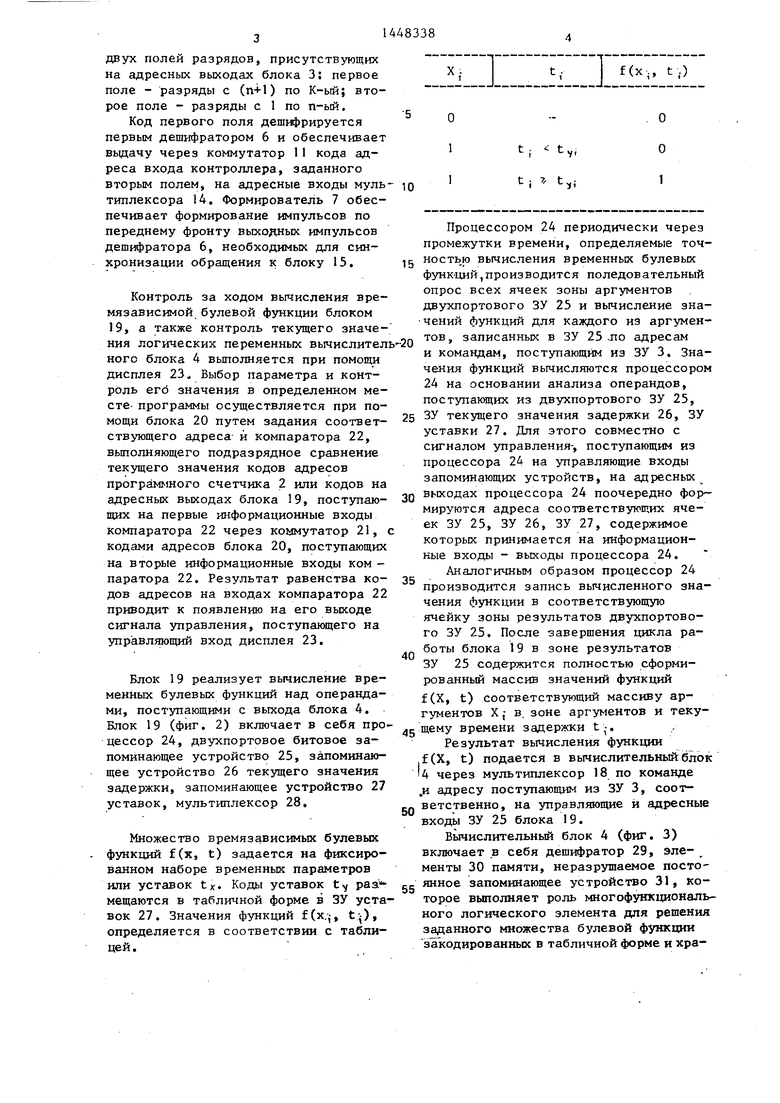

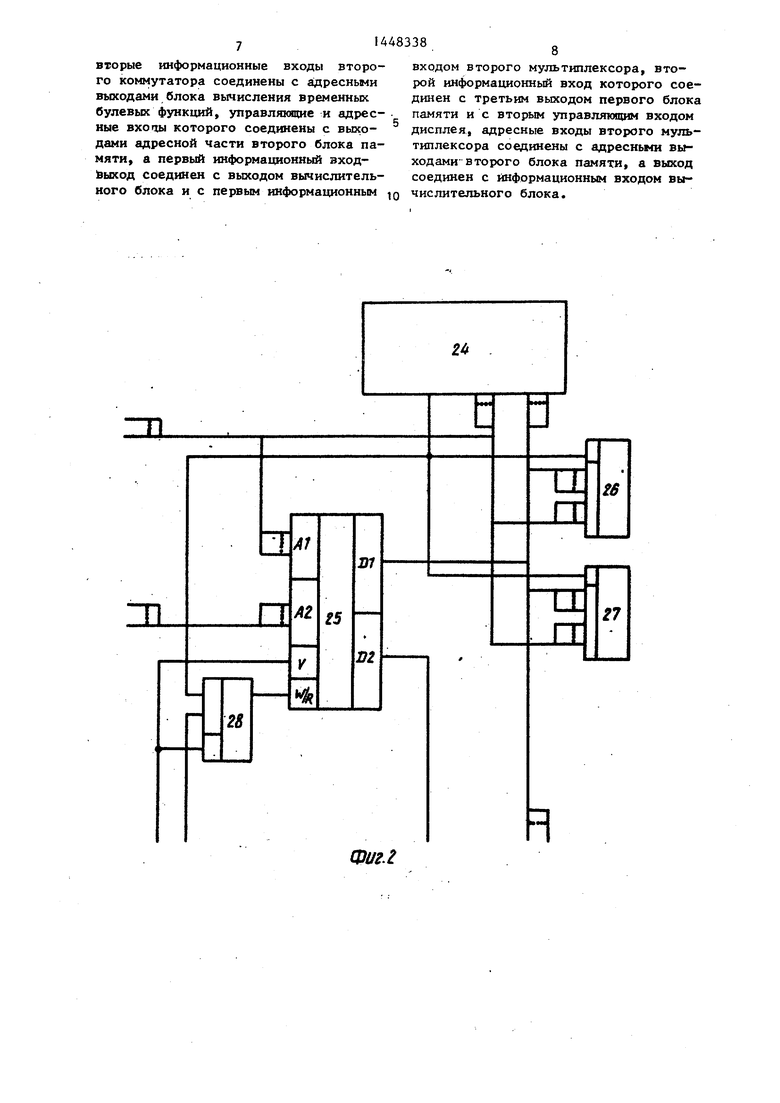

На фиг. 1 приведена структурная схема программируемого контроллера; 25 на фиг. 2 - функциональная схема вычислительного блока; на фиг. 3 - функциональная схема блока вычисления временных булевых функций.

Программируемый контроллер содер- 30 жит генератор 1 импульсов, программный счетчик 2, блок памяти запоминающее устройство (ЗУ) 3, вычис- лительньШ блок 4, блок 5 формирования выходных сигналов, дешифратор 6, д форшфователь 7 импульсов, состоящий из элемента 8 задержки и элемента И 9, дешифратор 10, первый коммутатор 1I, адресный счетчик 12 элементы согласования 13, первый мультиплек- дО сор 14, блок памяти э апоминающее устройство Г5, регистр 16 памяти, мажоритарный элемент 17,-второй мультиплексор 18, блок 19 вьгаисления временных булевых функций, блок 20 за- 5 Дания кодов адреса, второй коммутатор 21, компаратор 22, дисплей 23.

Программируемый контроллер работает следующим образом.

Генератор 1 формирует импульсы, CQ которые с его выхода поступают на вход счетчика 2. На выходах счетчика 2 формируется код, который подается на адресные входы блока 3, обеспечивая вьщачу содержимого ячеек блока « 3. Каждый следующий импульс устанавливает на выходах счетчика 2 новый код адреса до тех пор, пока не будет последовательно считано содержимое

s 0

5

0 О 5

Q

всех ячеек. Затем цикл считьшания повторяется.

На выходах формируются коды команд, состоящие из двух частей: кода адреса и кода операции. Код операщда поступает на управляющие входы блока 4, код адреса - на адресные входы блока 5, дешифратора 6, мультиплексора 18, информационные входы коммутатора 11.

Блок 4 реализует логическую функцию над операндом-, поступающим с выхода мультиплексора 18, и операндом, хранящимся в памяти блока 4, в соответствии с кодом операции на его управляющих входах.

Ввод операции осуществляется через мультиплексор 18 либо с выхода блока 19, либо с входа программируемого контроллера.

Повышенная помехоустойчивость и защита информации от дребезга контактов и пропадания питания во вход-г ных цепях контроллера обеспечивается путем анализа входного сигнала на основании ввода его значения в трех выборках, разнесенных во времени. Мультиплексором 14 осуществляется выбор входа контроллера, номер которого соответствует коду адреса, задаваемому адресным счетчиком 12, и подключение входного сигнала, проходящего через элементы 13 согласования к пер вому входу блока 15 и одному из входов мажоритарного элемента 17. Импульс записи, поступающий с выхода 1 дешифратора 10, производит запись информации по адресу, опредег ляеному кодов на адресных входах 15. Между импульсами записи блока 15 работает в режиме чтения, и импульсами с выхода И дешифратора 10 производится запись в два разряда регистра 16 содержимого двух ячеек блока 15. Таким образом после окончания импульса записи в регистр 16 на входах элемента 17 присутствует информац м о входном сигнале, полученная в три момента времени, определяемом периодами следования импульсов с выходов дешифратора 10. С выхода мажоритарного элемента 17 на третий вход блока 15 передается сигнал, присутствующий на большинстве его входов. Информация с выхода блока 15 поступает в блок 4 через мультиплексор 18 под управлением специашьной команды из блока 15. Эта команда состоит из

двух полей разрядов, присутствующих на адресных выходах блока 3; первое поле - разряды с (п+1) по К-ый; второе поле - разряды с 1 по п-ый.

Код первого поля дешифрируется первым дешифратором 6 и обеспечивает выдачу через коммутатор 11 кода адреса входа контроллера, заданного вторым полем, на адресные входы мультиплексора 14. Формирователь 7 обеспечивает формирование импульсов по переднему фронту выходных импульсов дешифратора 6, необходимых для синхронизации обращения к блоку 15,

Контроль за ходом вычисления вре- мязависимой булевой функции блоком 19, а также контроль текущего значения логических переменньсс вычислителного блока 4 вьшолняется при помощи дисплея 23. Выбор параметра и контроль его значения в определенном месте- программы осуществляется при помощи блока 20 путем задания соответствующего адреса и компаратора 22, выполняющего подразрядное сравнение текущего значения кодов адресов программного счетчика 2 или кодов на адресных выходах блока 19, поступающих на первые информационные входы компаратора 22 через коммутатор 21, кодами адресов блока 20, поступающих на вторые информационные входы ком - паратора 22. Результат равенства кодов адресов на входах компаратора 22 приводит к появлению на его выходе сигнала управления, поступающего на управляющий вход дисплея 23.

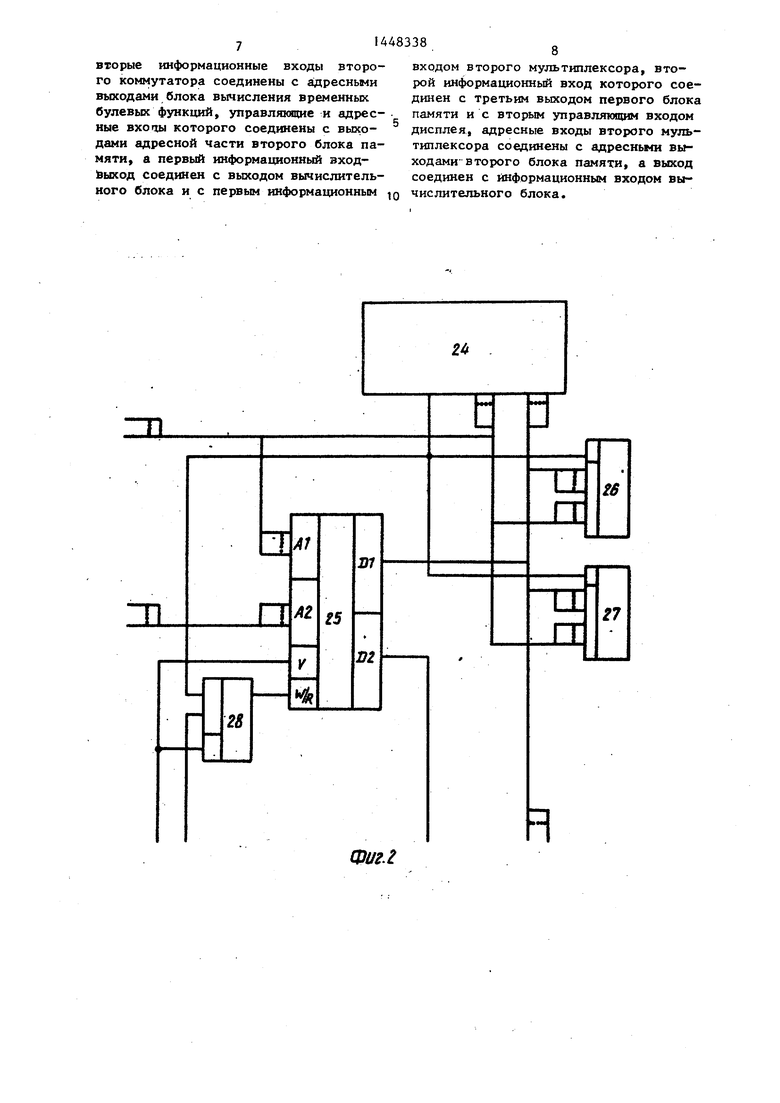

Блок 19 реализует вычисление временных булевых функций над операндами, поступающими с выхода блока 4. Блок 19 (фиг. 2) включает в себя процессор 24, двухпортовое битовое запоминающее устройство 25, запоминающее устройство 26 текущего значения задержки, запоминающее устройство 27 уставок, мультиплексор 28.

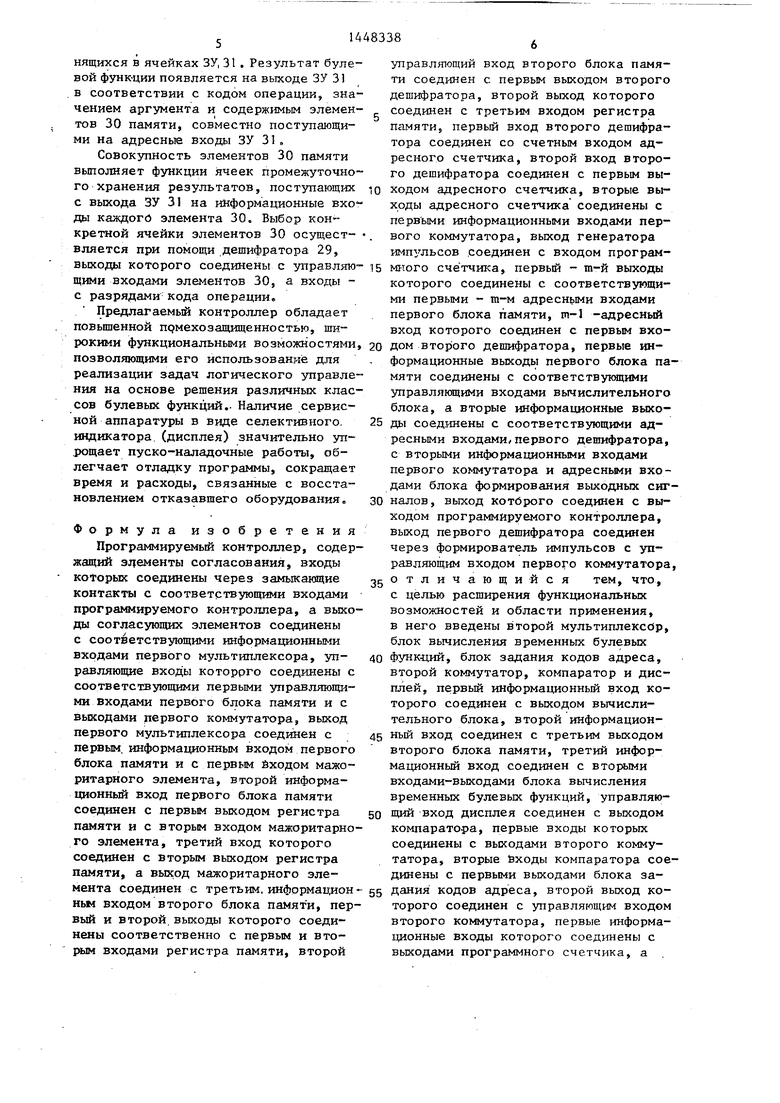

Множество времязависимых булевых функций f(x, t) задается на фиксированном набора временных параметров или уставок tx. Коды уставок ty мещаются в табличной форме в ЗУ уставок 27. Значения функций f(x.-, t;), определяется в соответствии с таблицей .

:j..JjiZE LE

о 1

t,. t,

t. 7. t,,;

. 0 0

1

5

0

Процессором 24 периодически через промежутки времени, определяемые точg ность ю вычисления временных булевых функ-ций, производится по ледов а тельный опрос всех ячеек зоны аргументов двухпортового ЗУ 25 и вычисление значений функций для каждого из аргументов, записанных в ЗУ 25 ло адресам и командам, поступающим из ЗУ 3. Значения функций вычисляются процессором 24 на основании анализа операндов, поступающих из двухпортового ЗУ 25,

5 ЗУ текущего значения задержки 26, ЗУ уставки 27. Для этого совместно с сигналом управления-, поступающим из процессора 24 на управляющие входы запоминающих устройств, на адресных

Q вь1ходах процессора 24 поочередно формируются адреса соответствующих ячеек ЗУ 25, ЗУ 26, ЗУ 27, содержимое которых принимается на информационные входы - выходы процессора 24.

Аналогичным образом процессор 24 производится запись вычисленного значения функции в соответствзтощую ячейку зоны результатов двухпортового ЗУ 25. После завершения цикла работы блока 19 в зоне результатов ЗУ 25 содержится полностью сформированный массив значений функций f(X, t) соответствующий массиву аргументов X { в, зоне aprybjeHTOB и теку5 щему времени задержки t-.

Результат вычисления функции ,f(X, t) подается в вычислительный блок 14 через мультиплексор 18 по команде .и адресу поступающим из ЗУ 3, соот- ветственно, на управляющие и адресные входы ЗУ 25 блока 19.

Вь1числительный блок 4 (фиг. 3) включает в себя дешифратор 29, эле- менты 30 памяти, неразрушаемое постоянное запоминающее устройство 31, которое выполняет роль многофункционального логического элемента для решения заданного множества булевой функции закодированных в табличной форме и хра5

нящихся в ячейках ЗУ, 31 . Результат булевой функции появляется на выходе ЗУ 31 в соответствии с кодом операции, значением аргумента и содержимым элементов 30 памяти, совместно поступающими на адресные входы ЗУ 31.

Совокупность элементов 30 памяти вьшолняет функции ячеек промежуточного хранения результатов, постзшающих с выхода ЗУ 31 на информационные вхо ды каждого элемента 30, Выбор кон кретной ячейки элементов 30 осущест- вляется при помощи дешифратора 29,

управляющий вход второго блока памяти соединен с первым выходом второго дешифратора, второй выход которого соединен с третьим входом регистра памяти, первьш вход второго дешифратора соединен со счетным входом адресного счетчика, второй вход второго дешифратора соединен с первым выходом адресного счетчика, вторые выходы адресного счетчика соединены с первыми информационными входами первого коммутатора, выход генератора импзшьсов соединен с входом програм

| название | год | авторы | номер документа |

|---|---|---|---|

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА ИНФОРМАЦИИ | 1999 |

|

RU2159952C1 |

| Устройство для программного управления технологическим оборудованием | 1987 |

|

SU1476434A1 |

| УСТРОЙСТВО ДЛЯ ВВОДА В МИКРОЭВМ ДИСКРЕТНЫХ СИГНАЛОВ | 1990 |

|

RU2007751C1 |

| Имитатор для тестирования компонентов моноканальной локальной вычислительной сети | 1987 |

|

SU1446621A1 |

| Устройство для обработки информации датчиков | 1980 |

|

SU955093A1 |

| Программируемый контроллер | 1985 |

|

SU1352484A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Программируемый контроллер | 1989 |

|

SU1741100A1 |

| Устройство для исследования графов | 1984 |

|

SU1238099A1 |

Программируемый контроллер относится к управляющим системам с программным управлением и может быть использован для логического управления технологическим устройством. В состав устройства входят генератор 1 ы тульсоз, программный счетчик 2 первое запоминающее устройство 3, вычислительньм блок 4, блок 5 формирования выходных сигналов, первый дешифратор 6, формирователь 7 импульсов, состоящий из элемента В задержки и элемента И 9, второй дешифратор iO, первый коммутатор 11, адресный счетчик 12, элементы согласования 13, первьш мультиплексор 14, второе запоминающее устройство 15, регистр 16 памяти мажоритарный элемент 17, второй мультиплексор J8, блок 19 вычисления временных булевых функций, блок 20 задания кодов адреса вто - рой коммутатор 21, дисплей 23. Преимущество изобретения состоит в повышенной помехозащищенности, широких функциональных возможностях. 3 ил., 1 табл. S (Л с: 00 &д 00 00 Фи-г. /

выходы которого соединены с управляю- i5 миого счётчика, первый - т-й выходы

щими входами элементов 30, а входы - с разрядами кода операции.

Предлагаемый контроллер обладает повьппенной прмехоэащищенностью, широкими функциональными возможностями, 20 позволяющими его использование для реализации задач логического управления на основе решения различных классов булевых функций.. Наличие сервисной аппаратуры в виде селективного. индикатора.(дисплея) значительно упрощает пуско-наладочные работы, облегчает отладку программы, сокращает время и расходы, связанные с восстановлением отказавшего оборудования.

25

30

которого соединены с соответствующими первыми - т-м адресньгми входами первого блока памяти, m-I -адресный вход которого соединен с первым входом второго дешифратора, первые информационные выходы первого блока па мяти соединены с соответствукмцими управляющими входами вычислительного блока, а вторые информационные выходы соединены с соответствующими адресными входами первого дешифратора, с вторыми информационными входами первого коммутатора и адресньми входами блока формирования выходных сиг налов , выход котброго соединен с выходом программируемого контроллера, выход первого дешифратора соединен через формирователь импульсов с управляющим входом первого коммутатора отличающийся тем, что, с целью расширения функциональных возможностей и области применения, в него введены второй мультиплексор, блок вычисления временных булевых Функг1;ий, блок задания кодов адреса, второй коммутатор, компаратор и дисплей, первый информационный вход которого соединен с вькодом вычислительного блока, второй информацион- 45 ный вход соединен с третьим выходом второго блока памяти, третий информационный вход соединен с вторыми входами-выходами блока вычисления временных булевых функций, управляющий вход дисплея соединен с выходом компаратора, первые входы которых соединены с выходами второго коммутатора, вторые йходы компаратора сое динены с первыми выходами блока задания кодов адреса, второй выход которого соединен с управляющим входом второго коммутатора, первые информационные входы которого соединены с выходами программного счетчика, а

Формула изобретения

Программируемый контроллер, содержащий элементы согласования, входы которых соединены через замыкакяцие контакты с соответствующими входами программируемого контроллера, а выходы согласующих элементов соединены с соответствующими информационными входами первого мультиплексора, управляющие входы которого соединены с соответствующими первыми управляющими входами первого блока памяти и с выходами рервого коммутатора, выход первого мультиплексора соединен с первым, информационным входом первого блока памяти и с первым йходом мажоритарного элемента, второй информационный вход первого блока памяти соединен с первым выходом регистра памяти и с вторым входом мажоритарного элемента, третий вход которого соединен с вторым выходом регистра памяти, а выход мажоритарного элемента соединен с третьим. инфррмаи;ион ньм входом второго блока памят и, первый и второй, выходы которого соединены соответственно с первым и вторым входами регистра памяти, второй

5

0

5

которого соединены с соответствующими первыми - т-м адресньгми входами первого блока памяти, m-I -адресный вход которого соединен с первым входом второго дешифратора, первые информационные выходы первого блока памяти соединены с соответствукмцими управляющими входами вычислительного блока, а вторые информационные выходы соединены с соответствующими адресными входами первого дешифратора, с вторыми информационными входами первого коммутатора и адресньми входами блока формирования выходных сигналов , выход котброго соединен с выходом программируемого контроллера, выход первого дешифратора соединен через формирователь импульсов с управляющим входом первого коммутатора, отличающийся тем, что, с целью расширения функциональных возможностей и области применения, в него введены второй мультиплексор, блок вычисления временных булевых Функг1;ий, блок задания кодов адреса, второй коммутатор, компаратор и дисплей, первый информационный вход которого соединен с вькодом вычислительного блока, второй информацион- 5 ный вход соединен с третьим выходом второго блока памяти, третий информационный вход соединен с вторыми входами-выходами блока вычисления временных булевых функций, управляющий вход дисплея соединен с выходом компаратора, первые входы которых соединены с выходами второго коммутатора, вторые йходы компаратора соединены с первыми выходами блока задания кодов адреса, второй выход которого соединен с управляющим входом второго коммутатора, первые информационные входы которого соединены с выходами программного счетчика, а

0

0

5

вторые информационные входы второго коммутатора соединены с адресными выходами блока вычисления временных булевых функций, управляющие и адресные ВХОГ1Ы которого соединены с выходами адресной части второго блока памяти, а первый информационный вход- Ьыход соединен с выходом вычислительного блока и с первым информационным

I

А1

m

п

AZ

15

8

входом второго мультиплексора, второй информационный вход которого соединен с третьим выходом первого блока памяти и с вторым управляющим входом дисплея, адресные входы второго мультиплексора соединены с адресными выходами второго блока памяти, а выход соединен с информационным входом вычислительного блока.

Б1

И

гг

27

| Способ управления процессом прессования порошкового материала и устройство для его осуществления | 1987 |

|

SU1507537A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Программируемый контроллер | 1981 |

|

SU1001012A1 |

Авторы

Даты

1988-12-30—Публикация

1987-01-09—Подача