{54 ЦИФРОВОЙ КОРРЕЛЯТОР

| название | год | авторы | номер документа |

|---|---|---|---|

| Цифровой коррелятор | 1980 |

|

SU894719A1 |

| ОПТИЧЕСКИЙ ЦИФРОВОЙ СТРАНИЧНЫЙ УМНОЖИТЕЛЬ С ПЛАВАЮЩЕЙ ТОЧКОЙ | 1998 |

|

RU2137179C1 |

| Арифметическое устройство | 1978 |

|

SU687982A1 |

| Интегроарифметическое устройство | 1987 |

|

SU1515162A2 |

| УСТРОЙСТВО УМНОЖЕНИЯ | 1998 |

|

RU2148270C1 |

| Множительно-делительное устройство | 1980 |

|

SU902026A1 |

| Арифметическое устройство | 1989 |

|

SU1656525A1 |

| Устройство для умножения чисел | 1981 |

|

SU999045A1 |

| Устройство для вычисления функций | 1985 |

|

SU1297038A1 |

| Устройство для умножения | 1979 |

|

SU868751A1 |

. / ,; . : л . , ; : ,- -... ,;-; :

Изобретение относится к вычисяйтельйой технике и может быть испсЗль. 3 овано в систе.мах автоматическо р управления и контроля, применяемых например в радиолокации.

Известен коррелятор, предназначенный для вычисления значений корреляционной функции исследуемых случайных тфоцессов X (t) и у (t), включаюший в себя квантователи входных сигналов по уровню/ устройство выборки во времени, матричную схему умножения, генераторы импульсов выборки и импульсов заполнения ключ И со схемой управления и накапливающий счётчик, входы устройства выборки во времени подключены к выходам квантователей входных сигналов, а выходы - ко входам матричной схемы умножения, второй, выход .генератора1 импульсов выборки соединен с управляющим входом устройства выборки во времени. Первый, второй и третий выходы ключа И подключены соответственно к первым выходам генераторов импульсов заполнения и выборки, а также к управляющему выходу схемы управления ключом И. Информационные входы Накапливающего счетчика связаны с одноименными выходами матричной схемы умножения, управляющий вход - с первым выходом ключа И, управляющий вход схемы управления ключом соединен со вторым выходом ключа и, а информационные входа подключены к соответствующим выходам схемы матричного умножения 1. Недостаток .такого коррелятора низкое йлстродействие.

o

Известно также устройство цифровой корреляции, предназначенное для определения степени связи между дву-j мя временны ® рядадда. цифровых величин, выраженных в виде чисел с плаваквдей

5 запятой,содержащее два входных узла, сумматор порядков,узел неравнозначности, два сумматора Накопления результатов положительныз и отрицательных произведений, блок преобразова0ния отрицательных чисел в дополнительный код, сумматор произведений и выходной узел.Знаковые выходы входных узлов подключены к двум входам узла неравнозначности, а выходы раз5ядов порядков соединены со входами сумматора порядков. Выход сумматора порядков подключен к третьему входу узла неравнозначности, первый выход которого соединен со входом суммато0ра накопления результатов положительных произведений, а второй выход подключен ко входу сумматора накопления результата отрицательных произведений, выход последнего подключен ко входу блока преобразования отрица1%льных чисел в дополнительный код, первый вход суматора произведений соединен с выходом сумматора накопления результата положительных произведений, а второй вход - с выходом блока преобразования отрицательных чисел в дополнительный код, выход сумматора произведений соединен со входом выходного узла устройства цифровой корреляции 2.

Недостаток известного устройства большая статическая погрешность при ограниченном числе выборок.

Наиболее близким техническим решением к предлагаемому изобретению является цифровой коррелятор предназначенный для обработки случайных величин, представленных в нормальной форме и содержащий дба аналого-цифровых преобразователя, два входных регистра, сумматор произведений, промежуточные (входное и выходное) ЗУ, а также множительное устройство,состоящее из узла неравнозначности/ сумматора порядков и умножителя мантисс

В сумматоре порядков определяется значение порядка произведения , в умножителе - мантисса произведения модульных значений перемножаемых величин, а в узле неравнозначности определяется знак произведения. Полученные таким образом произведени поступают на сумматор произведений, которые затем заносятся в ЗУ RCi) для промежуточного хранения, Оконч:ательная величина оценки значений корреляционной функции R{it) формируется на выходе сумматора произведений 3 ,

Недостатком такого коррелятора является низкое быстродействие.

Цель изобретения - увеличение быстродействия устройства.

Поставленная достигается тем что в цифровой коррелятор, содержащий два аналого-цифровых преобразователя, входы которых являются соответственно первым и вторым входами коррелятора, а выходы подключены: ко входам- соответственно первого и второго регистров, выход знакового разряда каждого регистра подключен к cootвeтcтвyющeмy входу блока неравнозн чности, выход которого соединен р первым входом блока суммирования йроизведений, второй вход которого подключен к выходу сумматора порядков, входы которого подключены к соответствующим разрядным выходам первого и второго регистров, разрядные выходы первого регистра подключены к соответствующи входам первого блока памяти, выходы которого соединены с соответствующим

разрядными входами первого регистра, выход блока суммирования произведени соединен со входом второго блока памяти, выход которого подключен к третьему входу блока суммирования произведений, введены блок элементов И,бло сравнения и блок сложения мантисс, причем первые входы блока сложения мантисс и блока элементов И подключены к соответствующим разрядным выходам первого регистра, вторые входы блока сложения мантисс и блока эле ентов И подключены к соответствующи разрядным выходам второго регистра, вход блока элементов И соединен с . первым выходом блока сравнения,второ вход которого подключен к выходу блока сложения мантисс, а выход блока сравнения соединен с четвертым входом блока суммирования произведений,Y

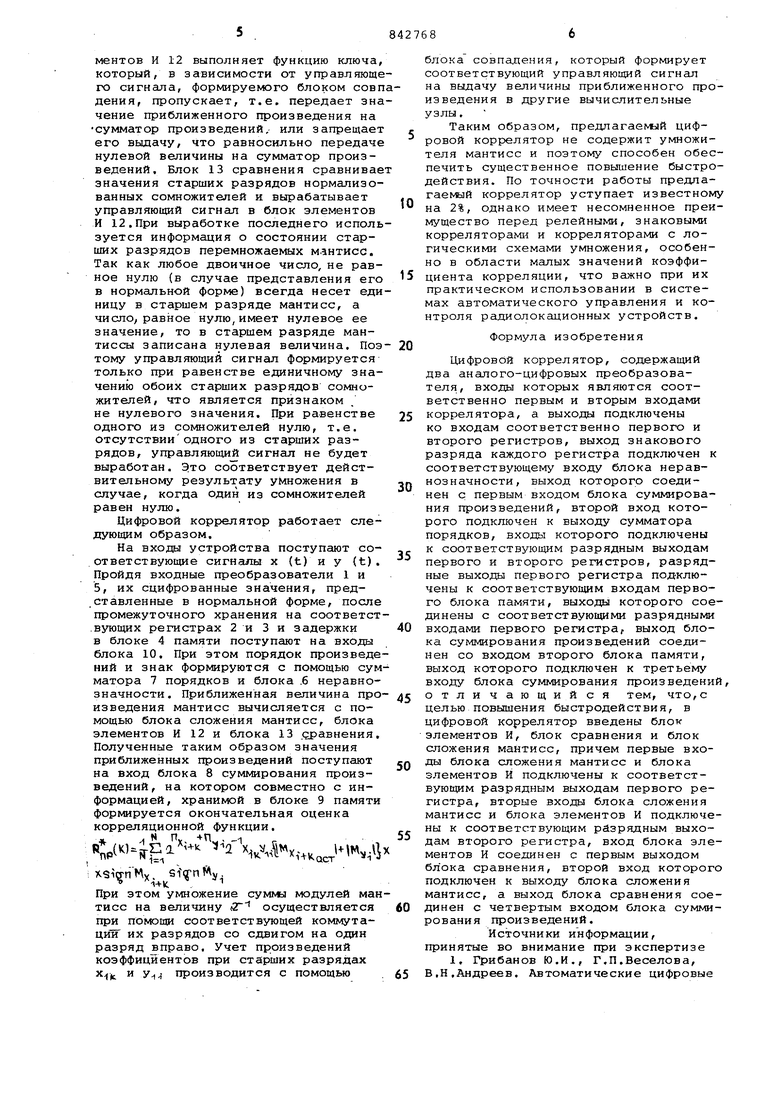

На чертеже показана структурная схема цифрового коррелятора.

Корреляторсодержит входной аналого-цифровой преобразователь 1, регистры 2 и 3, первый блок 4 памяти, аналого-цифровой преобразователь 5, блок б неравнозначности, сумматор 7 порядков, блок 8 суммирования произведений, второй блок 9 памяти, блок 10 умножения порядков, блок 11 сложения мантисс, блок 12 элементов И, блок 13 сравнения.

Входы двух аналого-цифровых преобразователей 1 являются соответственно первым и вторым входами цифрового коррелятора, а выходы соединены с одноименными входами двух регистров 2 и; 3,каждый из имеет выход знакового разряда и хода разрядов порядка и мантисс. Дополнительно регистр 2 связан с блоком 4 памяти, выходы знаковых разрядов регистров 2 и 3. подключены ко входам блоков неравнозначности, а выходы разрядов порядка - ко входам сумматора 7 порядков блока 10,. умножени порядков. Выходы всех разрядов мантисс регистра 2 подключены к первому входу блока 11 сложения мантисс, а выходы всех разрядов мантисс, за исключением старшего регистра 3. ко второму входу. Информационный вхо блока элементов И 12 подключен к выходу блока 11 сложения мантисс, а выход ко входу блока 8 суммирования произведений. Управляющий вход блока элементов И 12 соединен с выходом блока 13 сравнения, входы которого подключены к выходам старших разрядов мантисс регистров 2 и 3, Выходы блока неравнозначности и сумматора 7 порядков соединены с одноименными входами блока 8 суммирования произведений, последний дополнительно связан с промежуточным блоком. 9 памяти. Блок 11 сложения мантисс предназначен для формирования значений приближенного произведения. Блок элементов И 12 выполняет функцию ключа который, в зависимости от управляющ го сигнала, формируемого блоком сов дения, пропускает, т.е. передает зна чение приближенного произведения на сумматор произведений, или запрещает его выдачу, что равносильно передаче нулевой величины на сумматор произведений. Блок -13 сравнения сравнивае значения старших разрядов нормализованных сомножителей и вырабатывает управляющий сигнал в блок элементов И 12.При выработке последнего исполь зуется информация о состоянии старших разрядов перемножаемых мантисс. Так как любое двоичное число, не равное нулю (в случае представления его в нормальной форме) всегда несет еди ницу в старшем разряде мантисс, а число, равное нулю,имеет нулевое ее значение, то в старшем разряде мантиссы записана нулевая величина, ПОЭ ТОМУ управляющий сигнал формируется только при равенстве единичному значению обоих старших разрядов сомножителей, что является признаком не нулевого значения. При равенстве одного из сомножителей нулю, т.е. отсутствииодного из старших разрядов, управляющий сигнал не будет выработан. Это соответствует дейс вительному результату умножения в случае, когда один из сомножителей равен нулю. Цифровой коррелятор работает слеД1ТОЩИМ образом, На входы устройства поступает соответствующие сигналы X (t) и у (t). Пройдя входные преобразователи 1 и 5, их оцифрованные значения, представленные в нормальной форме, после промежуточного хранения на соответст .вующих регистрах 2 и 3 и задержки в блоке 4 памяти поступают на -входы блока 10. При этом порядок произведе ний и знак формируются с помощью сум матора 7 порядков и блока .6 неравнозначности. Приближенная величийа про изведения мантисс вычисляется с помощъю блока сложения мантисс, блока элементов И 12 и блока 13 .сгравнения. Полученные таким образом значения приближенных произведений поступают на вход блока 8 суммирования произведений, на котором совместно с информацией, хранимой в блоке 9 памяти формируется окончательная оценка корреляционной функции. «np(., xSi riMy. Sfyn y При этом умножение сумлл модулей ман тисс на величину S осуществляется при помощи соответствующей коммутаций их разрядов со сдвигом на одии разряд право. Учет произведений коэффициентов при старших разрядах и У-1 производится с помощью блока совпадения, который формирует соответствующий управляющий сигнал на выдачу величины приближенного произведения в другие вычислительные узлы, Таким образом, предпагаекый цифровой коррелятор не содержит умножителя мантисс и поэтому способен обеспечить существенное повышение быстродействия. По точности работы предлагаемой коррелятор уступает известному на 2%, однако имеет несомненное преимущество перед релейными, знаковыми корреляторами и корреляторами с логическими схемами умножения, особенно в области малых значений коэффициента корреляции, что важно при их практическом использовании в системах автоматического управления и контроля радиолокационных устройств. Формула изобретения Цифровой коррелятор, содержащий два аналого-цифровых преобразователя, входы которых являются соответственно первым и вторым входами коррелятора, а выходы подключены ко входам соответственно первого и второго регистров, выход знакового разряда каждого регистра подключен к соответствующему входу блока неравнозначности, выход которого соединен с первым входом блока суммирова ния произведений, второй вход которого подключен к выходу сумматора порядков, входы которого подключены к соответствующим разрядным выходам первого и второго регистров, разрядные выходаз первого регистра подключены к соответствующем входам первого блока памяти, выходы которого соединены с соответствующими разрядными входами первого регистра, выход блока суммирования произведений соединен со входом второго блока памяти, выход которого подключен к третьему входу блока сум1«ирования произведений, отличающи.йся тем, что,с целью повышения быстродействия, в цифровой коррелятор введены блок элементов И, блок сравнения и блок сложения майтисс, причем первые входы блока сложения мантисс и блока элементов И подключены к соответствующим разрядным выходам первого регистра, вторые входы блока сложения мантисс и блока элементов И подключены к соответствующим разрядным выходам второго резтистра, вход блока элементов И Соединен с первым выходом блока сравнения, второй вход которого подключен к выходу блока сложения мантисс, а выход блока сравнения соединен с четвертым входом блока суммирования произведений. Источники информации, принятые во внимание при экспертизе 1, Грибанов Ю.И., Г.П.Веселова, В.Н.Андреев. Автоматические цифровые

,корреляторы. М., Энергия, 1971, с. 110, 138.

Авторы

Даты

1981-06-30—Публикация

1979-10-03—Подача