(54) ДИСКРЕТНОЕ ФАЗОСДВИГАЩЕЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования управляемых отметок времени | 1984 |

|

SU1221638A1 |

| Устройство для формирования управляемых отметок времени | 1986 |

|

SU1370645A2 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Фазосдвигающее устройство | 1980 |

|

SU998973A1 |

| СИНХРОННЫЙ ДЕТЕКТОР | 1997 |

|

RU2124804C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Цифровой фазовращатель | 1986 |

|

SU1372593A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1432451A2 |

| Устройство коррекции шкалы времени | 1990 |

|

SU1774307A1 |

| Цифровой фазовращатель | 1984 |

|

SU1239630A1 |

1

Изобретение относится к импульсной технике и предназначено для использования в устройствах автоматического управления и контроля в каналах цифровых следящих систем, в генераторах кодовых групп импульсов, в синхронизаторах радиолокационных и радионавигационных индикаторов.

По основному авт. св. № 496509 известно дискретное фазосдвигающее устройство, содержащее опорный генератор, счетчик, S1- и R1-дешифраторы, .коммутатор и блок управления ij .

Недостатком этого устройства является низкое быстродействие, т.е. время, необходимое для перестройки фазы выходного сигнала на заданную величину. Например, устройство за один цикл; пересчета его счетчика способно сдвинуть фазу выходного сигнала только на Один дискрет. В этой связи чем больше коэффициент пересчета счетчика k, тем медленнее происходит перестройка фазы. Для сдвига фазы выходного сигнала на п дискретов требуется подать п последовательно управляющих импульсов и затратить чистого времени только на перестройку фазы Т пТц, где Тц - цикл пересчета счетчика. В это время не входят затраты

на передачу управляквдих сигналов. В результате существенно ограничивается область использования дискретного фазосдвигающего устройства.

Цель изобретения - повышение быст-; родействия.

Поставленная цель достигается тем, что в дискретное фазосдвигающее устройство, содержащее опорный генера10тор, счетчик, коммутатор, S1- и R1дешифраторы и блок управления, дополнительно введены первый и второй блоки сопряжения, 52- и R2-дешифраторы, причем S1- и R1-дешифраторы,

15 выполнены четырехвходовыми, выход счетчика соединен со входами S2-, R2-дешифраторов и входами первого и второго блоков сопряжения, выход первого из которых соединен с инверс20ными входами S1 -, К1-дешифраторов, а выход второго - с одними из входов S2-, R2-дешифраторов, другие входы котОЕИЛх соединены соответственно с прямым и инверсным выходами KONnviyTa25тора, а выходы S2- R2-дешифраторев соответственно с S2- и R-2 входами счетчика.

Под S2- и R2-дешифраторами подразумеваются комбинации И, ИЛИ, НЕ логических элементов, выполняющие функции совпадения. Например, можно использовать два четырехвходовых элемента И. Под блоком сопряжения подразумевается цифровой автомат, выполняющий функцию преобразования входного сигнала произвольной длительности в сигнал требуемой длительности и передачи его синхронно с работой счетчика на его управлякидий вход.Сущность изобретения в функциональном смысле состоит в том, что устройство позволяет за цикл пересчета счетчика изменять дискрет не только на половину, но и на период сигнала опорного генератора от управляющего сигнала произвольной длительности в зависимости от того, на какой из входов подать этот сигнал.

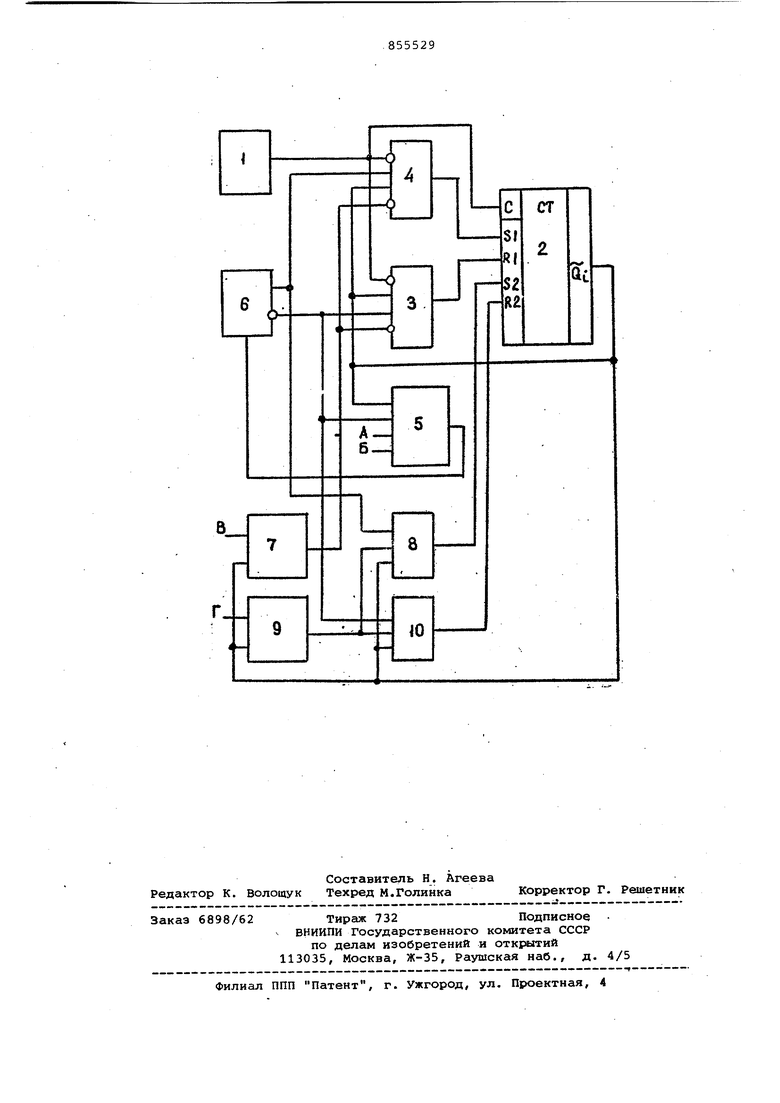

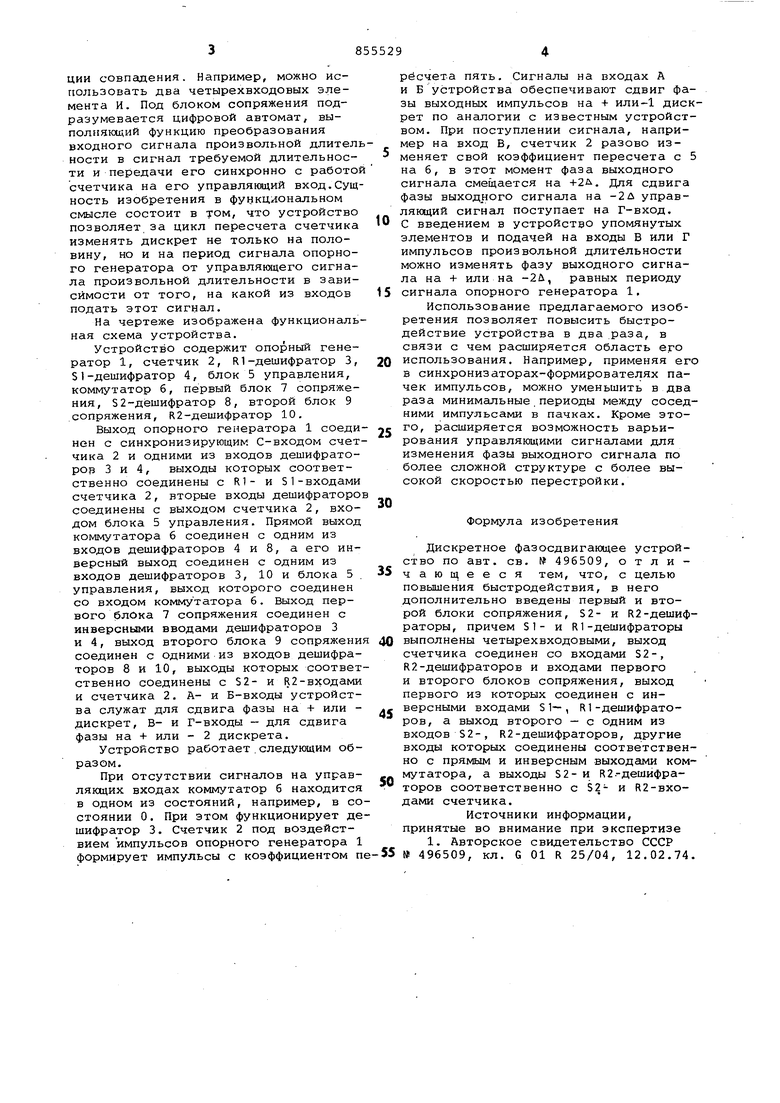

На чертеже изображена функциональная схема устройства.

Устройство содержит опорный генератор 1, счетчик 2, R1-дешифратор 3, S)-дешифратор 4, блок 5 управления, коммутатор 6, первый блок 7 сопряжения, S2-дешифратор 8, второй блок 9 сопряжения, К2-дешифратор 10.

Выход опорного генератора 1 соединен с синхронизирующим С-входом счетчика 2 и одними из входов дешифраторов 3 и 4, выходы которых соответственно соединены с R1- и 51-входами счетчика 2, вторые входы дешифраторо соединены с выходом счетчика 2, входом блока 5 управления. Прямой выход коммутатора 6 соединен с одним из входов дешифраторов 4 и 8, а его инверсный выход соединен с одним из входов дешифраторов 3, 10 и блока 5 . управления, выход которого соединен со входом коммутатора 6. Выход первого блока 7 сопряжения соединен с инверсными вводами дешифраторов 3 и 4, выход второго блока 9 сопряжени соединен с одними из входов дешифраторов 8 и 10, выходы которых соответственно соединены с S2- и К2-входами и счетчика 2. А- и Б-входы устройства служат для сдвига фазы на + или дискрет. В- и Г-входы - для сдвига фазы на + или - 2 дискрета.

Устройство работает.следующим образом.

При Отсутствии сигналов на управляющих входах коммутатор б находится в одном из состояний, например, в состоянии 0. При этом функционирует дешифратор 3. Счетчик 2 под воздействием импульсов опорного генератора 1 формирует импульсы с коэффициентом пресчета пять. Сигналы на входах А и Б устройства обеспечивают сдвиг фазы выходных импульсов на + или-1 дискрет по аналогии с известным устройством. При поступлении сигнала, например на вход в, счетчик 2 разово из меняет свой коэффициент пересчета с 5 на б, в этот момент фаза выходного сигнала смещается на +2Д. Для сдвига фазы выходного сигнала на -2Д управляющий сигнал поступает на Г-вход.

С введением в устройство упомянутых элементов и подачей на входы В или Г импульсов произвольной длительности можно изменять фазу выходного сигнала на + или на -2й, равных периоду

5 сигнала опорного генератора 1,

Использование предлагаемого изобретения позволяет повысить быстродействие устройства в два раза, в связи с чем расширяется область его

0 использования. Например, применяя его в синхронизаторах-формирователях пачек импульсов, можно уменьшить в два раза минимальные.периоды между соседними импульсами в пачках. Кроме этос го, расширяется возможность варьирования управляющими сигналами для изменения фазы выходного сигнала по более сложной структуре с более высокой скоростью перестройки.

Формула изобретения

Дискретное фазосдвигающее устройство по авт. св. № 496509, о т л и чающееся тем, что, с целью повышения быстродействия, в него дополнительно введены первый и второй блоки сопряжения, S2- и R2-дешифраторы, причем S1- и К1-дешифраторы

выполнены четырехвходовыми, выход счетчика соединен со входами S2-, R2-дешифраторов и входами первого и второго блоков сопряжения, выход первого из которых соединен с инверсными входами S 1-, R1-дешифраторов, а выход второго - с одним из входов S2-, R2-дешифраторов, другие входы которых соединены соответственно с прямым и инверсным выходами коммутатора, а выходы S2- и R2.-дeшифpaторов соответственно с 52- и RZ-BXoдами счетчика.

Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР

№ 496509, кл. G 01 R 25/04, 12.02.74.

Авторы

Даты

1981-08-15—Публикация

1979-11-16—Подача