(риг.1

Изобретение относится к радиотехнике и может использоваться в синхронизирующих устройствах и автономных хранителях времени.

Известно устройство для коррекции шкалы времени, в котором коррекция осуществляется за счет использования в качестве фазосдвигающего блока делителя с переменным коэффициентом деления К±1, что дает возможность вводить коррекцию любого знака 1. К недостаткам данного устройства следует отнести малый диапазон и большое время коррекции.

Известно устройство коррекции шкалы времени, предназначенное для точной коррекции времени внутри секундного интервала и использующее в качестве инструмента коррекции схему сравнения для выделения момента обнуления делителя, когда на кодовых шинах последнего появляется код, равный коду коррекции. Благодаря этому осуществляется укорочение цикла пересчета в делителе и происходит сдвиг фазы, соответствующий величине коррекции. Устройство имеет более рациональную по сравнению с предыдущим схему 2. К его недостаткам следует отнести малый диапазон и большое время коррекции.

Наиболее близким к заявляемому решению является устройство для коррекции шкалы времени, реализующее коррекцию времени за счет использования делителя с переменным коэффициентом деления. Устройство содержит генератор, фазосдвигаю- щий блок, делитель частоты, реверсивный счетчик, регистр сдвига, преобразователь кода коррекции, два элемента И, счетчик, дешифратор, два формирователя одиночных импульсов, формирователь сигналов управления, два RST-триггера, D-триггер, генератор пачки импульсов, два элемента ИЛИ, элемент ИЛИ-НЕ, мультиплексор 3.

Благодаря использованию мультиплексора, регистра сдвига, реверсивного счетчика, триггера знака в устройстве используется режим точной и грубой коррекции. Соответственно обеспечиваются высокая точность и широкий диапазон коррекции.

Однако устройство-прототип обладает большими затратами времени на коррекцию, обусловленными тем, что для смещения шкалы времени затрачивается время, в к раз больше, чем величина времени коррекции. Определяется это тем, что для смещения шкалы времени на один дискрет (один такт опорного генератора) затрачивается один цикл времени пересчета в фазосдвига- ющем блоке, выполненном на делителе с

переменным коэффициентом деления, равным К±1.

Цель изобретения - сокращение времени коррекции.

Достигается цель тем, что в устройство

коррекции шкалы времени, содержащее генератор импульсов, фазосдвигающий блок, делитель и триггер знака, причем выход генератора импульсов соединен с тактовым

0 входом фазосдвигающего блока, прямой выход триггера знака соединен с первым управляющим входом фазосдвигающего блока, выход делителя соединен с выходом устройства, введены счетчик поправки, блок

5 управления делителем, блок управления счетчиком поправки, при этом выход генератора импульсов дополнительно соединен со счетным входами делителя и счетчика поправки, информационная магистраль ко0 да коррекции соединена с информационными входами фазосдвигающего блока и счетчика поправки, вход знака поправки соединен с D-входом триггера знака, командный вход устройства подключен к счетному

5 входу триггера знака, входом записи фазосдвигающего блока и счетчика поправки, первому входу блока управления счетчиком поправки, выход фазосдвигающего блока подключен к второму входу блока управле0 ния счетчиком поправки и входу переноса блока управления делителем, прямой выход триггера знака дополнительно соединен с входом поправки блока управления делителем, инверсный выход триггера знака сое5 динен с вторым управляющим входом фазосдвигающего блока, выход счетчика поправки подключен к третьему входу блока управления счетчиком поправки, выход которого соединен с входом разрешения счета

0 поправки и с управляющим входом блока управления делителя, выходы направления счета и разрешения счета блока управления делителем соединены с соответствующими входами делителя.

5 При этом фазосдвигающий блок состоит из счетчика прямого счета, реверсивного счетчика. JK-триггера. трех двухвходовых и двух трехвходовых элементов И, двух элементов ИЛИ, элемента НЕ, причем счетный

0 вход блока соединен со счетными входами обоих счетчиков и JK-триггера, информационный вход блока соединен с информационным входом реверсивного счетчика, первый управляющий вход блока подключен к входу

5 направления счета реверсивного счетчика и первому входу первого трехвходового элемента И, второй управляющий вход блока соединен с первым входом второго трехвходового элемента И, вход записи блока соединен с входом записи реверсивного

счетчика и первым входом первого элемен та ИЛИ, выход счетчика прямого счета соединен с первыми входами первого и второго двухвходовых элементов И, выход переноса реверсивного счетчика подключен к вторым входам трехвходовых элементов И, К-входу JK-триггера и через элемент НЕ к второму входу первого и первому входу третьего двухвходовых элементов И, прямой выход JK-триггера соединен с третьими входами трехвходовых и вторым входом третьего двухвходового элементов И, инверсный выход триггера соединен с вторым входом второго двухвходового элемента И и входом разрешения счета счетчика прямого счета, выход первого двухвходового элемента И соединен с J-входом триггера, выход третьего двухвходового элемента И соединен с входом разрешения счета реверсивного счетчика, выходы первого трехвходового и второго двухвходового элементов И через второй элемент ИЛИ подключены к выходу блока, выход второго трехвходового элемента И через первый элемент ИЛИ соединен с R-входом триггера.

Таким образом, отличительной особенностью заявляемого устройства является использование максимальной тактовой частоты (частоты задающего генератора) для коррекции состояния делителя,

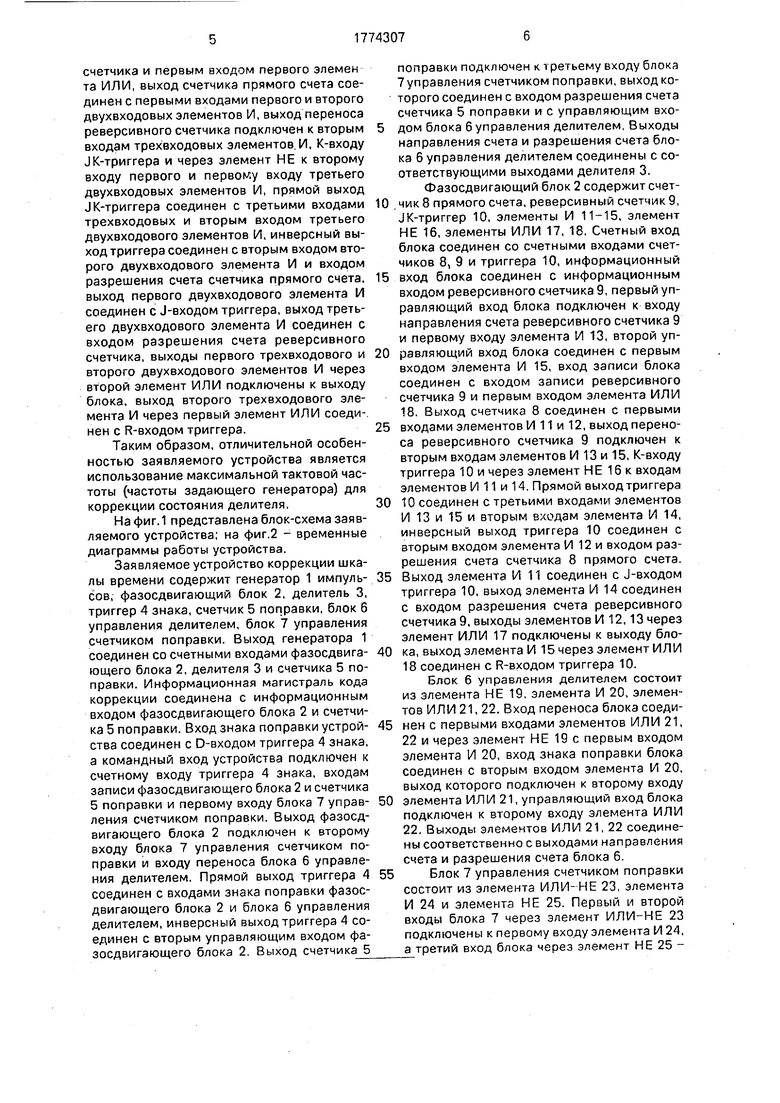

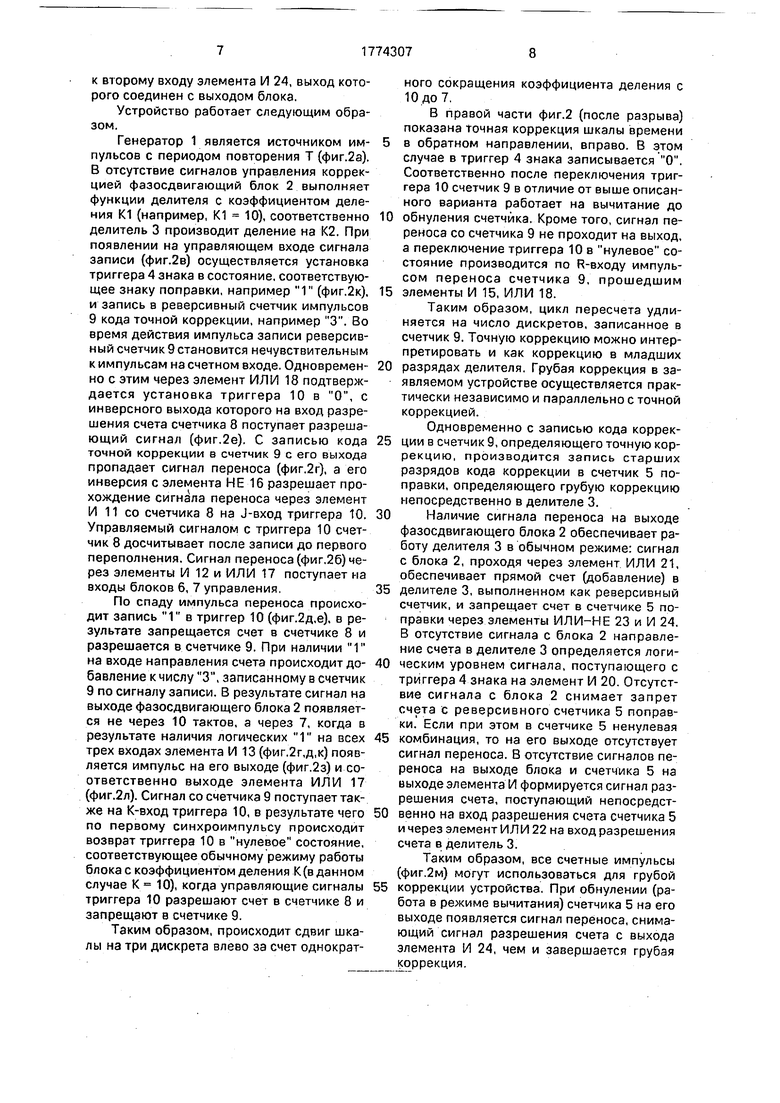

На фиг.1 представлена блок-схема заявляемого устройства; на фиг.2 - временные диаграммы работы устройства.

Заявляемое устройство коррекции шкалы времени содержит генератор 1 импульсов, фазосдвигающий блок 2, делитель 3, триггер 4 знака, счетчик 5 поправки, блок 6 управления делителем, блок 7 управления счетчиком поправки. Выход генератора 1 соединен со счетными входами фазосдвига- гощего блока 2, делителя 3 и счетчика 5 поправки. Информационная магистраль кода коррекции соединена с информационным входом фазосдвигающего блока 2 и счетчика 5 поправки. Вход знака поправки устройства соединен с D-входом триггера 4 знака, а командный вход устройства подключен к счетному входу триггера 4 знака, входам записи фазосдвигающего блока 2 и счетчика 5 поправки и первому входу блока 7 управления счетчиком поправки. Выход фазосдвигающего блока 2 подключен к второму входу блока 7 управления счетчиком поправки и входу переноса блока 6 управления делителем. Прямой выход триггера 4 соединен с входами знака поправки фазосдвигающего блока 2 и блока 6 управления делителем, инверсный выход триггера 4 соединен с вторым управляющим входом фазосдвигающего блока 2. Выход счетчика 5

поправки подключен к i ретьему входу блока 7 управления счетчиком поправки, выход которого соединен с входом разрешения счета счетчика 5 поправки и с управляющим вхо- 5 дом блока 6 управления делителем, Выходы направления счета и разрешения счета блока 6 управления делителем соединены с соответствующими выходами делителя 3. Фазосдвигающий блок 2 содержит счет0 чик 8 прямого счета, реверсивный счетчик 9, JK-триггер 10, элементы И 11-15, элемент НЕ 16, элементы ИЛИ 17, 18. Счетный вход блока соединен со счетными входами счетчиков 8, 9 и триггера 10, информационный

5 вход блока соединен с информационным входом реверсивного счетчика 9, первый управляющий вход блока подключен к входу направления счета реверсивного счетчика 9 и первому входу элемента И 13, второй уп0 равляющий вход блока соединен с первым входом элемента И 15, вход записи блока соединен с входом записи реверсивного счетчика 9 и первым входом элемента ИЛИ 18. Выход счетчика 8 соединен с первыми

5 входами элементов И 11 и 12, выход переноса реверсивного счетчика 9 подключен к вторым входам элементов И 13 и 15, К-входу триггера 10 и через элемент Н Е 1 б к входам элементов И 11 и 14. Прямой выход триггера

0 10 соединен с третьими входами элементов И 13 и 15 и вторым входам элемента И 14, инверсный выход триггера 10 соединен с вторым входом элемента И 12 и входом разрешения счета счетчика 8 прямого счета.

5 Выход элемента И 11 соединен с J-входом триггера 10, выход элемента И 14 соединен с входом разрешения счета реверсивного счетчика 9, выходы элементов И 12,13 через элемент ИЛИ 17 подключены к выходу бло0 ка, выход элемента И 15 через элемент ИЛИ 18 соединен с R-входом триггера 10.

Блок 6 управления делителем состоит из элемента НЕ 19, элемента И 20, элементов ИЛИ 21, 22. Вход переноса блока соеди5 нен с первыми входами элементов ИЛИ 21, 22 и через элемент НЕ 19 с первым входом элемента И 20, вход знака поправки блока соединен с вторым входом элемента И 20, выход которого подключен к второму входу

0 элемента ИЛИ 21, управляющий вход блока подключен к второму входу элемента ИЛИ 22. Выходы элементов ИЛИ 21, 22 соединены соответственно с выходами направления счета и разрешения счета блока 6.

5Блок 7 управления счетчиком поправки

состоит из элемента ИЛИ-НЕ 23, элемента И 24 и элемента НЕ 25. Первый и второй входы блока 7 через элемент ИЛИ-НЕ 23 подключены к первому входу элемента И 24, а третий вход блока через элемент НЕ 25 к второму входу элемента И 24, выход которого соединен с выходом блока.

Устройство работает следующим образом.

Генератор 1 является источником импульсов с периодом повторения Т (фиг.2а).

8отсутствие сигналов управления коррекцией фазосдвигающий блок 2 выполняет функции делителя с коэффициентом деления К1 (например, К1 10), соответственно делитель 3 производит деление на К2. При появлении на управляющем входе сигнала записи (фиг.2в) осуществляется установка триггера 4 знака в состояние, соответствующее знаку поправки, например 1 (фиг.2к), и запись в реверсивный счетчик импульсов

9кода точной коррекции, например 3. Во время действия импульса записи реверсивный счетчик 9становится нечувствительным к импульсам на счетном входе. Одновременно с этим через элемент ИЛИ 18 подтверждается установка триггера 10 в О, с инверсного выхода которого на вход разрешения счета счетчика 8 поступает разрешающий сигнал (фиг.2е). С записью кода точной коррекции в счетчик 9 с его выхода пропадает сигнал переноса (фиг.2г), а его инверсия с элемента НЕ 16 разрешает прохождение сигнала переноса через элемент И 11 со счетчика 8 на J-вход триггера 10. Управляемый сигналом с триггера 10 счетчик 8 досчитывает после записи до первого переполнения. Сигнал переноса (фиг,2б) через элементы И 12 и ИЛИ 17 поступает на входы блоков 6, 7 управления.

По спаду импульса переноса происходит запись 1 в триггер 10 (фиг.2д,е). в результате запрещается счет в счетчике 8 и разрешается в счетчике 9. При наличии 1 на входе направления счета происходит добавление к числу 3, записанному в счетчик 9 по сигналу записи. В результате сигнал на выходе фазосдвигающего блока 2 появляется не через 10 тактов, а через 7, когда в результате наличия логических 1 на всех трех входах элемента И 13 (фиг.2г,д,к) появляется импульс на его выходе (фиг.2з) и соответственно выходе элемента ИЛИ 17 (фиг.2л). Сигнал со счетчика 9 поступает также на К-вход триггера 10, в результате чего по первому синхроимпульсу происходит возврат триггера 10 в нулевое состояние, соответствующее обычному режиму работы блока с коэффициентом деления К (в данном случае К 10), когда управляющие сигналы триггера 10 разрешают счет в счетчике 8 и запрещают в счетчике 9.

Таким образом, происходит сдвиг шкалы на три дискрета влево за счет однократного сокращения коэффициента деления с 10 до 7.

В правой части фиг.2 (после разрыва) показана точная коррекция шкалы времени

в обратном направлении, вправо. В этом случае в триггер 4 знака записывается О. Соответственно после переключения триггера 10 счетчик 9 в отличие от выше описанного варианта работает на вычитание до

0 обнуления счетчика. Кроме того, сигнал переноса со счетчика 9 не проходит на выход, а переключение триггера 10 в нулевое состояние производится по R-входу импульсом переноса счетчика 9, прошедшим

5 элементы И 15, ИЛИ 18.

Таким образом, цикл пересчета удлиняется на число дискретов, записанное в счетчик 9. Точную коррекцию можно интерпретировать и как коррекцию в младших

0 разрядах делителя. Грубая коррекция в заявляемом устройстве осуществляется практически независимо и параллельно с точной коррекцией.

Одновременно с записью кода коррек5 ции в счетчик 9, определяющего точную коррекцию, производится запись старших разрядов кода коррекции в счетчик 5 поправки, определяющего грубую коррекцию непосредственно в делителе 3.

0 Наличие сигнала переноса на выходе фазосдвигающего блока 2 обеспечивает работу делителя 3 в обычном режиме: сигнал с блока 2, проходя через элемент ИЛИ 21, обеспечивает прямой счет (добавление) в

5 делителе 3, выполненном как реверсивный счетчик, и запрещает счет в счетчике 5 поправки через элементы ИЛИ-НЕ 23 и И 24. В отсутствие сигнала с блока 2 направление счета в делителе 3 определяется логи0 ческим уровнем сигнала, поступающего с триггера 4 знака на элемент И 20. Отсутствие сигнала с блока 2 снимает запрет счета с реверсивного счетчика 5 поправки. Если при этом в счетчике 5 ненулевая

5 комбинация, то на его выходе отсутствует сигнал переноса. В отсутствие сигналов переноса на выходе блока и счетчика 5 на выходе элемента И формируется сигнал разрешения счета, поступающий непосредст0 венно на вход разрешения счета счетчика 5 и через элемент ИЛИ 22 на вход разрешения счета в делитель 3.

Таким образом, все счетные импульсы (фиг.2м) могут использоваться для грубой

5 коррекции устройства. При обнулении (работа в режиме вычитания) счетчика 5 на его выходе появляется сигнал переноса, снимающий сигнал разрешения счета с выхода элемента И 24, чем и завершается грубая коррекция.

Эффективность заявляемого устройства можно определить путем сравнения времени, затрачиваемого на коррекцию шкалы времени на одну и ту же величину устройством-прототипом и заявляемым устройством. Пусть эта величина

At-Кфсб Кд -Т,

где Кфсб - коэффициент деления, реализуемый фазосдвигающим блоком;

Кд - коэффициент деления делителя;

Т - минимальный дискрет коррекции, равный периоду генератора 1.

В этих условиях можно записать

tnpoi Кфсб КДТ {Кфсб ± 1).

Поскольку в заявляемом устройстве процесс точной и грубой коррекции осуществляется параллельно и независимо, то время коррекции для него будет определяться максимальной из двух величин

1точн.ззяв И Тгруб.заяв

1точн.эаяе - 2 Кфсб Т;

1груб.заяв Кд Кфсб Т

Кфсб - 1

Так как обычно Кд Кфсб. то можно принять гзаяв ируб.заяв и определить отношение

Кфсб Кд Т ( Кфс6 ± 1 ) ( Кфс6 - 1 ) Кфсб Кд Т

- (Кфсб ± 1) (Кфсб - 1) - (Кфсб - 1) 2.

Приведенные расчеты доказывают эффективность заявляемого устройства по сравнению с устройством-прототипом.

Формула изобретения Устройство коррекции шкалы времени, содержащее генератор импульсов, фазосд- вигающий блок, делитель и триггер знака, прямой выход которого соединен с первым управляющим входом фазосдвитающего блока, выход генератора импульсов соединен с тактовым входом фазосдвигающего блока, а выход делителя соединен с выходом устройства, отличающееся тем, что, с целью сокращения времени коррекции, в устройство введены счетчик поправки, блок управления делителем, блок

управления счетчика поправки, выход генератора импульсов соединен со счетными входами делителя и счетчика поправки, информационная магистраль кода коррекции 5 соединена с информационными входами фазосдвигающего блока и счетчика поправки, вход знака поправки соединен с D-вхо- дом триггера знака, командный вход устройства подключен к счетному входу

0 триггера знака, входу записи фазосдвигающего блока и счетчика поправки, первому входу блока управления счетчиком поправки, выход фазосдвигающего блока подключен к второму входу блока управления

5 счетчиком поправки и входу переноса блока управления делителем, прямой выход триггера знака дополнительно соединен с входом знака поправки блока управления делителем, инверсный выход триггера зна0 ка соединен с вторым управляющим входом фазосдвигающего блока, выход счетчика поправки подключен к третьему входу блока управления счетчиком поправки, выход которого соединен с входом разрешения счета

5 счетчика поправки и с управляющим входом блока управления делителем, выходы направления счета и разрешения счета блока управления делителем соединены с соответствующими входами делителя, фазосд0 витающий блок содержит счетчик прямого счета, реверсивный счетчик, JK-триггер, три двухвходовых и два трехвходовых и два трехвходовых элемента И, два элемента ИЛИ, элемент НЕ, счетный вход фазосдви5 тающего блока соединен со счетными входами реверсивного счетчика и счетчика прямого счета и с тактовым входом JK- триггера, информационный вход блока соединен с информационным входом ре0 версивного счетчика, первый управляющий вход фазосдвигающего блока подключен к входу направления счета реверсивного счетчика и к первому входу первого трехвхо- дового элемента И, второй управляющий

5 вход фазосдвигающего блока соединен с первым входом второго трехвходового элемента И, вход записи фазосдвигающего блока соединен с входом записи реверсивного счетчика и первым входом первого элемента

0 ИЛИ, выход счетчика прямого счета соединен с первыми входами первого и второго двухвходовых элементов И, выход переноса реверсивного счетчика подключен к вторым входам трехвходовых элементов И, к входу

5 JK-триггера и через элемент НЕ к второму входу первого и первому входу третьего двухвходовых элементов И, прямой выход JK-триггера соединен с третьими входами трехвходовых и вторым входом третьего двухвходового элемента И, инверсный выход JK-триггера соединен с вторым входом второго двухвходового элемента 1/1 и входом разрешения счета счетчика прямого счета, выход первого двухвходового элемента И соединен с J-входом триггера, выход треть- его двухвходового элемента И соединен с входом разрешения счета реверсивного счетчика, выходы первого трехвходового и второго двухвходового элементов И через второй элемент ИЛИ подключены к выходу фазосдвигающего блока, выход второго трехвходового элемента И через первый элемент ИЛИ соединен с R-входом JK-триггера, блок управления делителем содержит второй элемент НЕ, дополнительный эле- мент И и третий и четвертый элементы ИЛИ, вход переноса блока управления делителем соединен с первыми входами третьего и четвертого элементов ИЛИ и через второй элемент НЕ - с первым вхо- дом дополнительного элемента И, вход знака поправки блока управления делителем соединен с вторым входом дополнительного элемента И, выход которого подключен к второму входу третьего элемента ИЛИ, управляющий вход блока управления делителем подключен к второму входу четвертого элемента ИЛИ, выходы третьего и четвертого элементов ИЛИ соединены соответственно с входами направления счета и разрешения счета блока управления делителем, а блок управления счетчиком поправки состоит из элемента ИЛИ-НЕ, вспомогательного элемента И и третьего элемента НЕ, первый и второй входы блока управления счетчиком через элементы ИЛИ-НЕ подключены к первому входу вспомогательного элемента И, а третий вход блока управления счетчиком поправки через третий элемент НЕ соединен с вторым входом вспомогательного элемента И, выход которого соединен с выходом блока.

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2014 |

|

RU2553093C1 |

| Устройство для коррекции шкалы времени | 1986 |

|

SU1365039A2 |

| Электронные часы | 1984 |

|

SU1224786A1 |

| УСТРОЙСТВО ПОИСКА ИНФОРМАЦИИ | 2006 |

|

RU2313128C1 |

| Устройство для коррекции шкалы времени | 1990 |

|

SU1709268A1 |

| Устройство поиска информации | 2017 |

|

RU2656736C1 |

| Устройство для коррекции шкалы времени | 1982 |

|

SU1095431A1 |

| Устройство для коррекции шкалы времени | 1987 |

|

SU1506570A1 |

| Устройство для управления вентильным преобразователем | 1990 |

|

SU1753561A1 |

| Умножитель частоты | 1978 |

|

SU798831A1 |

Изобретение относится к радиотехнике и может использоваться в синхронизирующих устройствах а автономных хранителях времени. Сущность изобретения: устройство содержит генератор 1 импульсов, фазос- двигающий блок 2, делитель 3, триггер 4 знака, счетчик 5 поправки, блоки управления делителем 6 и счетчиком поправки 7. 2 ил.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1992-11-07—Публикация

1990-08-01—Подача