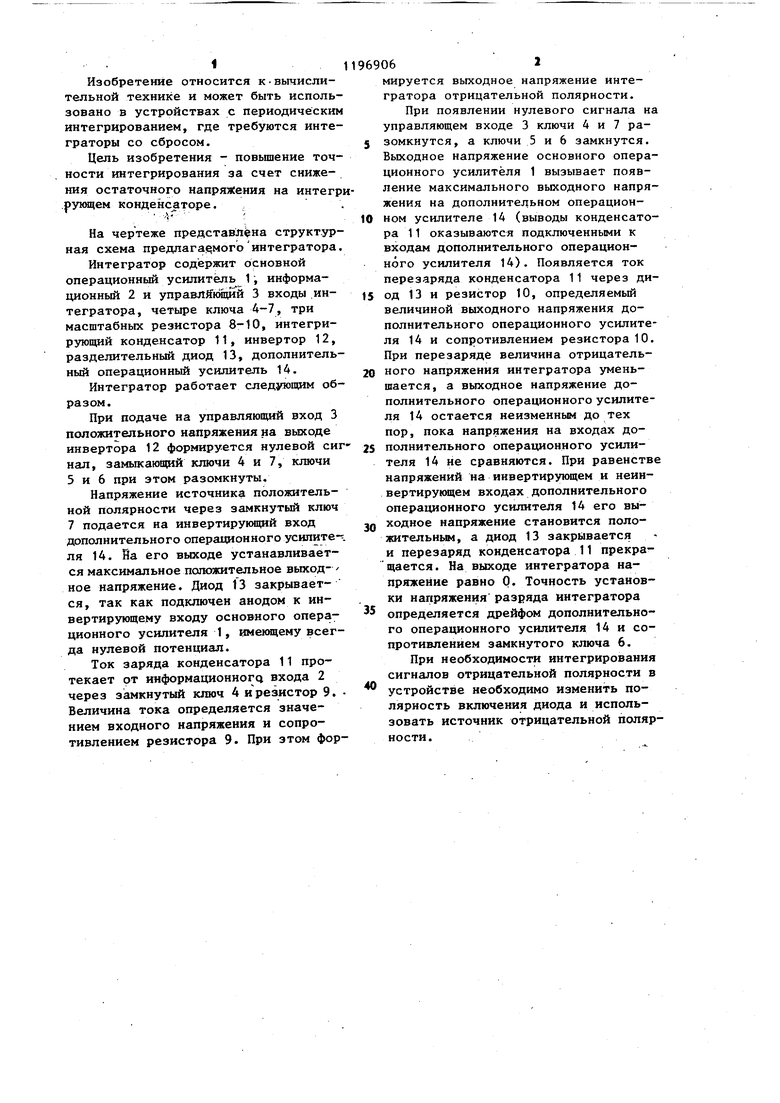

1 Изобретение относится квычислительной технике и может быть исполь зовано в устройствах с периодически интегрированием, где требуются инте граторы со сбросом. Цель изобретения - повышение точ ности интегрирования за счет снижения остаточного напряжения на интег руиицем конденсаторе. На чертеже представлена структур ная схема предлагаемогоинтегратора Интегратор содержит основной операционный усилитель 1, информационный 2 и управлЯкшщй 3 входы интегратора, четыре ключа А-7, три масштабных резистора 8-10, интегрируюцщй конденсатор 11, инвертор 12, разделительный диод 13, дополнитель ный операционный усилитель 14. Интегратор работает следующим об разом. При подаче на управляющий вход 3 положительного напряжения на вьлсоде инвертора 12 формируется нулевой си нал, замыкаю1ций ключи 4 и 7, ключи 5 и 6 при этом разомкнуты. Напряжение источника положительной полярности через замкнутый ключ 7 подается на инвертирующий вход дополнительного операционного усипителя 14. На его выходе устанавливается максимальное положительное выходное напряжение. Диод 13 закрывается, так как подключен анодом к инвертирующему входу основного операционного усилителя 1, имеющему всегда нулевой потенциал. Ток заряда конденсатора 11 протекает от информационногQ входа 2 через замкнутый ключ 4 и резистор 9. Величина тока определяется значением входного напряжения и сопротивлением резистора 9. При зтом фор 061 мируется выходное напряжение интегратора отрицательной полярности. При появлении нулевого сигнала на управляющем входе 3 ключи 4 и 7 разомкнутся, а ключи 5 и 6 замкнутся. Выходное напряжение основного операционного усилителя 1 вызывает появление максимального выходного напряжения на дополнительном операционном усилителе 14 (выводы конденсатора 1 1 оказываются подключенными к входам дополнительного операционного усилителя 14). Появляется ток перезаряда конденсатора 11 через диод 13 и резистор 10, определяемый величиной выходного напряжения дополнительного операционного усилителя 14 и сопротивлением резистора 10. При перезаряде величина отрицательного напряжения интегратора уменьшается, а выходное напряжение дополнительного операционного усилителя 14 остается неизменным до тех пор, пока напряжения на входах дополнительного операционного усилителя 14 не сравняются. При равенстве напряжений на инвертирующем и неинвертирующем входах дополнительного операционного усилителя 14 его выходное напряжение становится положительньм, а диод 13 закрывается и перезаряд конденсатора 11 прекращается. На выходе интегратора напряжение равно 0. Точность установки напряжения разряда интегратора определяется дрейфом дополнительного операционного усилителя 14 и сопротивлением замкнутого ключа 6. При необходимости интегрирования сигналов отрицательной полярности в устройстве необходимо изменить полярность включения диода и использовать источник отрицательной полярности.

X

| название | год | авторы | номер документа |

|---|---|---|---|

| Интегратор | 1978 |

|

SU855674A1 |

| Нуль-орган | 1976 |

|

SU596906A1 |

| Решающий усилитель с релейной характеристикой | 1984 |

|

SU1179378A1 |

| Интегратор со сбросом | 1984 |

|

SU1260977A1 |

| Интегратор | 1979 |

|

SU847330A1 |

| Устройство для моделированияиМпульСНОгО дАТчиКА чАСТОТы ВРАщЕНия | 1979 |

|

SU849245A1 |

| СПОСОБ ИЗМЕРЕНИЯ СРЕДНЕГО ЗНАЧЕНИЯ НАПРЯЖЕНИЯ ПРОИЗВОЛЬНОЙ ФОРМЫ И УСТРОЙСТВО ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 1990 |

|

RU2034302C1 |

| Многопредельный усилитель заряда | 1982 |

|

SU1113754A1 |

| Интегратор | 1978 |

|

SU748439A1 |

| Интегратор | 1988 |

|

SU1728871A1 |

ИНТЕГРАТОР, содержащий основной операционный усилитель,неинвентирующий вход которого подключен через первый масштабный резистор к шине нулевого потенциала, а инвентирующий вход через интегрирующий конденсатор - к выходу основного операционного усилителя, который является выходом интегратора, соединенные последовательно первый и второй ключи, включенные между информационным входом интегратора и шиной нулевого потенциала, третий ключ, подключенный первым выводом к выходу основного операционного усилителя,инверти-рующий вход которого через второй масштабный резистор подключен к общему выводу первого и второго ключей, причем управляющие входы второго и третьего ключей непосредственно, а управляющий вход первого ключа через инвертор подключены к управ-. ляющему входу интегратора, о т л и ч а ющи и ся тем, что, с целью повышения точности интегрирования, в него введены четвертый ключ, разделительный диод, третий масштабный резистор и дополнительный операцион§ ный усилитель, инвертирующий вход которого подключен к инвертирующему сл входу основного операционного усилителя и через последовательно соединенные разделительный диод и третий масштабньй резистор - к своему выходу, а неинвентирующий вход подключен к второму выводу третьего ключа и через четвертый ключ - к пш- :о не источника питания, при этом управ3 ляющий вход четвертого ключа подклю чен к выходу инвертора. . . 35

| Ленк Д | |||

| Руководство для пользователей операционных усилителей | |||

| М.: Связь, 1978, с.194, рис.4.3 | |||

| Управляемый интегратор | 1979 |

|

SU853630A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Шило В.Л | |||

| Линейные интегральные схемы | |||

| М.: Советское радио, 1979, с | |||

| Водяной двигатель | 1921 |

|

SU325A1 |

| Топка с несколькими решетками для твердого топлива | 1918 |

|

SU8A1 |

Авторы

Даты

1985-12-07—Публикация

1984-06-01—Подача