(54) СЧЕТНОЕ УСТРОЙСТВО

| название | год | авторы | номер документа |

|---|---|---|---|

| Формирователь сетки частот | 1985 |

|

SU1287257A1 |

| Устройство для управления обменом информацией | 1990 |

|

SU1783525A1 |

| Устройство для формирования очереди | 1986 |

|

SU1446626A1 |

| Устройство для вывода информации | 1986 |

|

SU1377849A1 |

| Устройство для контроля выполнения программ | 1987 |

|

SU1434439A1 |

| СЕЛЕКТОР ИМПУЛЬСНЫХ ПОСЛЕДОВАТЕЛЬНОСТЕЙ | 1994 |

|

RU2085028C1 |

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| Устройство для контроля за ходом вычислительного процесса | 1987 |

|

SU1539780A1 |

| Устройство тестового контроля | 1989 |

|

SU1691842A1 |

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

Изобретение относится к цифровой технике и предназначено для использования в аппаратуре обработки цифровой информации. Устройство может найти применение в измерительной аппаратуре, в частности в электронных измерителях времени. Известно счетное устройство, содержащее регист сдвига, блок коррек ции, блок двоичного вычитания, блок синхронизации и элементы И, ИЛИ 1 Недостатки этого устройства - ег относительная сложность и малое быстродействие. Наиболее близким техническим решением к предлагаемому является сче ное устройство, содержащее матрицу памяти, с дешифратором адреса, счет чик адреса, счетчик числа, входную шину, шину установки и блок управле ния , информационные выходы и входы счетчика числа соединены орответственно с информационными входами и выходами матрицы памяти с дешифратором адреса, адресные входы кото роЙ ; соединены с информационными выходами счетчика адреса, входная шин соединена с тактовым входом счетчика числа, первый и второй выходы блока управления соединены соответственно со счетным входом счетчика числа и со входом управления записи матрицы памяти с дешифратором адреса. Это устройство работает следующим образом. Из блока управления на вход управления записи матрицы памяти с дешифратором поступает импульс, по которому содержимое счетчика числа записывается в ячейку памяти с адресом, выбранным содержимым счетчика сщреса, после чего содержимое счетчика адреса увеличивается на единицу и в счетчик числа переписывается содержимое ячейки памяти с гщресом, указанным содержимым счетчика адреса. После этого к содержимому регистра числа прибавляются импульсы, поступающие по входной шине до тех пор, пока из блока управления не поступит следующий импульс на вход управления записи матрицы памяти и цикл повторяется (2 . Недостаток этого устройства - оно не может быть использовано в качестве многоразрядного счетчика импульсов. Цель изобретения-расширение функциональных возможиостой.

Поставленная цель достигается тем что в счетном устройстве, содержащем матрицу памяти с даиифратором адреса, счетчик адреса, счетчик числа, входную шину, цшну установки и блок управления, информационные выходы и входы счетчика чисел соединены соответственно с информационными входами и выходами матрицы памяти с дешифратором адреса, адресные входы которой соединены с информационными выходами счетчика адреса, блок управления состоит из узла анализа переносов и хранения импульсов, из узла установки и элемента ИЛИ, выход которого соединен со входом записи матрицы памяти с дешифратором адреса, входная шина соединена с тактовыми входами узла анализа переносов и хранения импульсов и узла установки, первый, второй, третий и четвертый выходы которого соединены соответственно со входами сброса счетчика адреса, счетчика числа, первым входом элемента ИЛИ и со входом сброса узла анализа переносов и хранения импульсов, первый,второй, третий и четвертый выходы которого соединены соответственно с тактовыми входами счетчиков адреса, числа, входом управления загрузкой счетчика числа, и ВТОЕ«М ВХ.ОДОМ элемента ИЛИ, шина установки соединена с первым входом узла установки, второй вход которого соединен с выходом переноса счетчика адреса и с первым входом узла анализа переносов и хранения импульсов, второй вход которого соединен с выходом переноса счетчика числа,

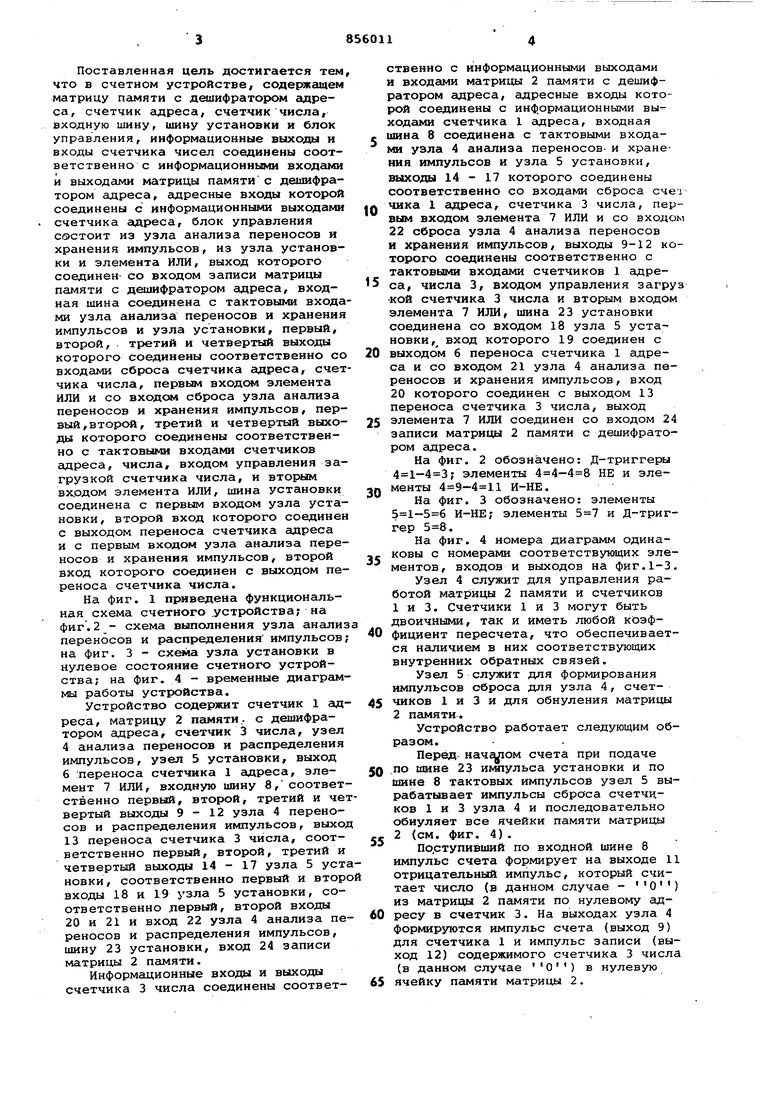

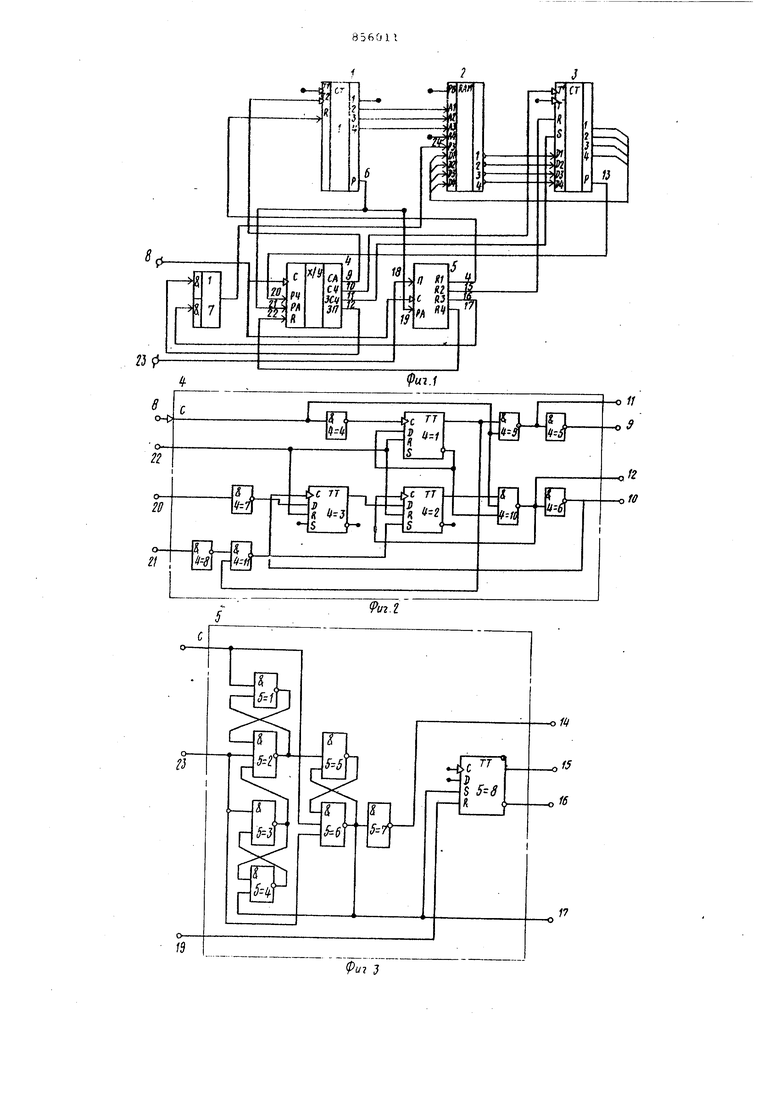

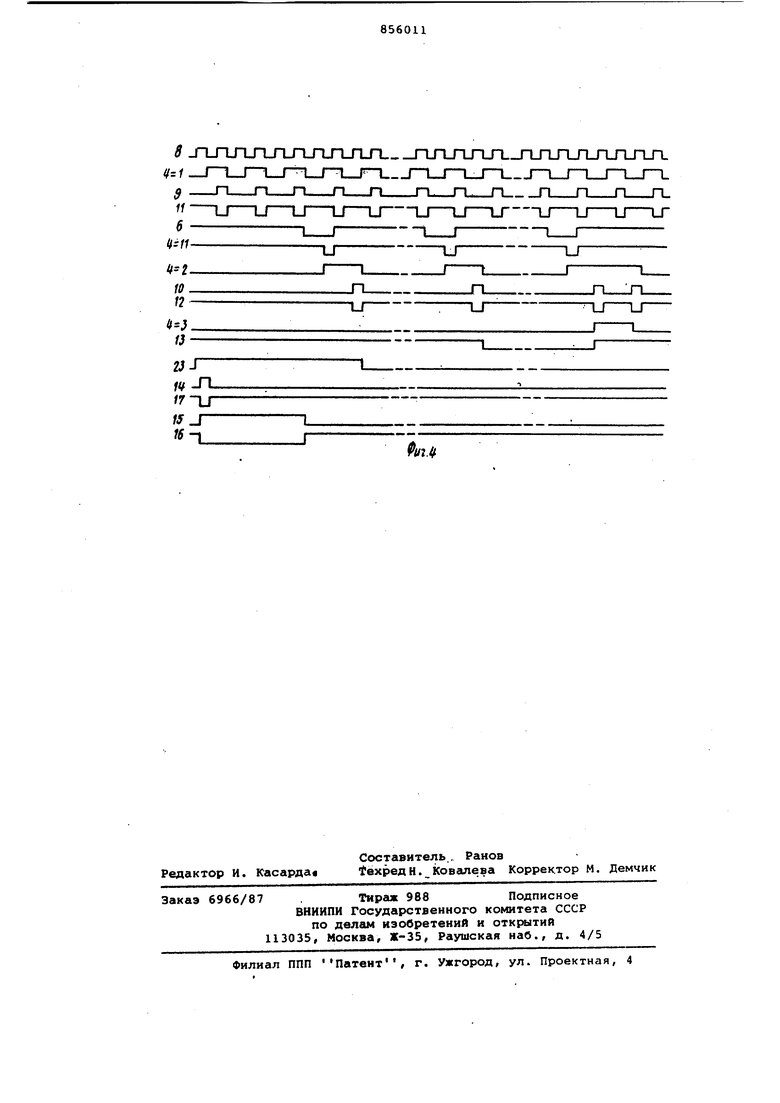

На фиг. 1 приведена функциональная схема счетного .устройства; на фиг.2 - схема вьтолнения узла ангшиз переносов и распределения импульсов; на фиг. 3 - схема узла установки в нулевое состояние счетного устройства; на фиг. 4 - временные диаграммы работы устройства.

Устройство содержит счетчик 1 адреса, матрицу 2 памяти., с дешифратором адреса, счетчик 3 числа, узел 4 анализа переносов и распределения импульсов, узел 5 установки, выход 6 переноса счетчика 1 адреса, элемент 7 ИЛИ, входную шину 8,соответственно первый, второй, третий и четвертый выходы 9-12 узла 4 переносов и распределения импульсов, выход 13 переноса счетчика 3 числа, соответственно первый, второй, третий и четвертый выходы 14 - 17 узла 5 установки, соответственно первый и второ входы 18 и 19 узла 5 установки, соответственно лервый, второй входы 20 и 21 и вход 22 узла 4 анализа переносов и распределения импульсов, шину 23 установки, вход 24 записи матрицы 2 памяти.

Информационные входы и выходы счетчика 3 числа соединены соответственно с информационными выходами и входами матрицы 2 памяти с дешифратором адреса, адресные входы которой соединены с информационными выходами счетчика 1 адреса, входная шина 8 соединена с тактовыми входами узла 4 анализа переносов- и хранения импульсов и узла 5 установки, выходы 14-17 которого соединены соответственно со входами сброса сче чика 1 адреса, счетчика 3 числа, первым входом элемента 7 ИЛИ и со входо 22 сброса узла 4 анализа переносов и хранения импульсов, выходы 9-12 которого соединены соответственно с тактовыми входами счетчиков 1 адреса, числа 3, входом управления загру кой счетчика 3 числа и вторым входом элемента 7 ИЛИ, шина 23 установки соединена со входом 18 узла 5 установки, вход которого 19 соединен с выходом б переноса счетчика 1 адреса и со входом 21 узла 4 ангшиза переносов и хранения импульсов, вход 20 которого соединен с выходом 13 переноса счетчика 3 числа, выход элемента 7 ИЛИ соединен со входом 24 записи матрицы 2 памяти с дешифратором адреса.

На фиг. 2 обозначено: Д-триггеры элементы НЕ и элементы И-НЕ.

На фиг. 3 обозначено: элементы И-НЕ; элементы и Д-триггер .

На фиг. 4 номера диаграмм одинаковы с номерами соответствующих элементов, входов и выходов на фиг.1-3.

Узел 4 служит для управления работой матрицы 2 памяти и счетчиков

1и 3. Счетчики 1 и 3 могут быть двоичными, так и иметь любой коэффициент пересчета, что обеспечивается наличием в них соответствующих внутренних обратных связей.

Узел 5 служит для формирования импульсов сброса для узла 4, счетчиков 1 и 3 и для обнуления матрицы

2ПсШЯТИ.

Устройство работает следующим образом.

Перед счета при подаче .по шине 23 импульса установки и по шине 8 тактовых импульсов узел 5 вырабатывает импульсы сброса счетчцков 1 и 3 узла 4 и последовательно обнуляет все ячейки памяти матрицы 2 (см. фиг. 4).

По.ступивший по входной шине 8 импульс счета формирует на выходе 11 отрицательный импульс, который считает число (в данном случае - О ) из матрицы 2 памяти по нулевому адресу в счетчик 3. На выходах узла 4 формируются импульс счета (выход 9) для счетчика 1 и импульс записи (выход 12) содержимого счетчика 3 числа (в данном случае О ) в нулевую ячейку памяти матрицы 2. Следующий счетный импульс по шине 8 производит считывание числа из памяти матрицы 2 по первому адресу, но изменения состояния сче1чика 3 числа и записи в память матрицы 2 произведено не будет, так как триггеры и {см. фиг. 2) находятся в нулевом состоянии (см. фиг, Последующие импульсы на шине 8 вызывают появление импульсов на выходах 9 и 11 узла тех пор, пока счетчик 1 не переберет по очереди вс числа из памяти матрицы 2. Переполне ние счетчика 1 переводит триггер 4 в состояние единицы и следующим импульсом по шине 8 содержимое памяти матрицы 2 по нулевому адресу увеличивается на единицу. Данный цикл повторяется без изменения до тех пор пока по нулевому адресу в памяти мат рицы 2 не формируется число, которое в счетчике 3 вызывает сигнал перепол нения на выходе 13. Переполнение счетчика 3 числа переводит триггеры и (см.фиг.2 в состояние единицы, что обеспечивает добавление единицы в содержимое матрицы 2 памяти по следующему адресу, т.е. будет рсуществлен в след ющую тетраду. В счетном устройстве младшие разряды кодиЕ уются параллельным кодом на выходах счетчика 1 адреса, старшие разряды кодируются последователь ным кодом, получаемым на выходах счетчика 3. При необходимости, индикация состояния счетного устройства в младших разрядах осуществляется статистическим индикатором, в старших раз рядах - динамическим индикатором, в данном случае роль распределителя импульсов играет счетчик адреса с дешифратором адреса, информацию на индикатор необходимо снимать со счет чика числа . Формула изобретения Счетное устройство, содержащее матрицу памяти с дешифратором гщреса, счетчик адреса, счетчик числа входную шину, шину установки и блок управления, информационные выходы и входы счетчика числа соединены соответственно с информационными входами и выходс1ми матрицы памяти с дешифратором адреса, отличающеес я тем, что, с целью расширения функциональных возможностей, блок управления состоит из узла анализа переносов и хранения импульсов у из узла установки и элемента ИЛИ, выход которого соединен со входом записи матрицы памяти с дешифратором аДреса, входная шина соединена с тактовыми входами узла анализа переносов и хранения импульсов и узла установки, первый, второй, третий и четвертый выходы которого соединены соответственно со входами сброса счетчика адреса,, счетчика числа, первым входом элемента ИЛИ и со входом сброса узла анализа переносов и хранения импульсов, первый,второй, третий и четвертый выходы которого соединены соответственно с тактовыми входами счетчиков гщреса, числа, входом управления загрузкой счетчика числа, и вторым входом элемента ИЛИ, шина установки соединена с первым входом узла установки, второй вход которого соединен с выходом переноса счетчика адреса и с первым входом узла анализа переносов и хранения импульсов, второй вход которого соединен с выходом переноса счетчика числа. Источники информации, принятые во внимание при экспертизе 1.Авторское свидетельство СССР по заявке 2610335/18-21, кл. Н 3 К 27/00, 24.04.7S. 2.Техническое описание накопителя спектров Сигма П53031.0Ь2 Сх.Б., 1968 (прототип). .

2JJ W-TL 5 Jtf-l

Й/7.«

Авторы

Даты

1981-08-15—Публикация

1979-11-15—Подача