N

00

4:

С СО

Изобретение относится к цифровой вычислительной технике и может быть использовано для контроля выполнения программ в цифровых вьмислительных машинах и программируемых контроллерах, построенных по принципу Общей магистрали.

Целью изобретения является повышение достоверности контроля за ходом выполнения программ.

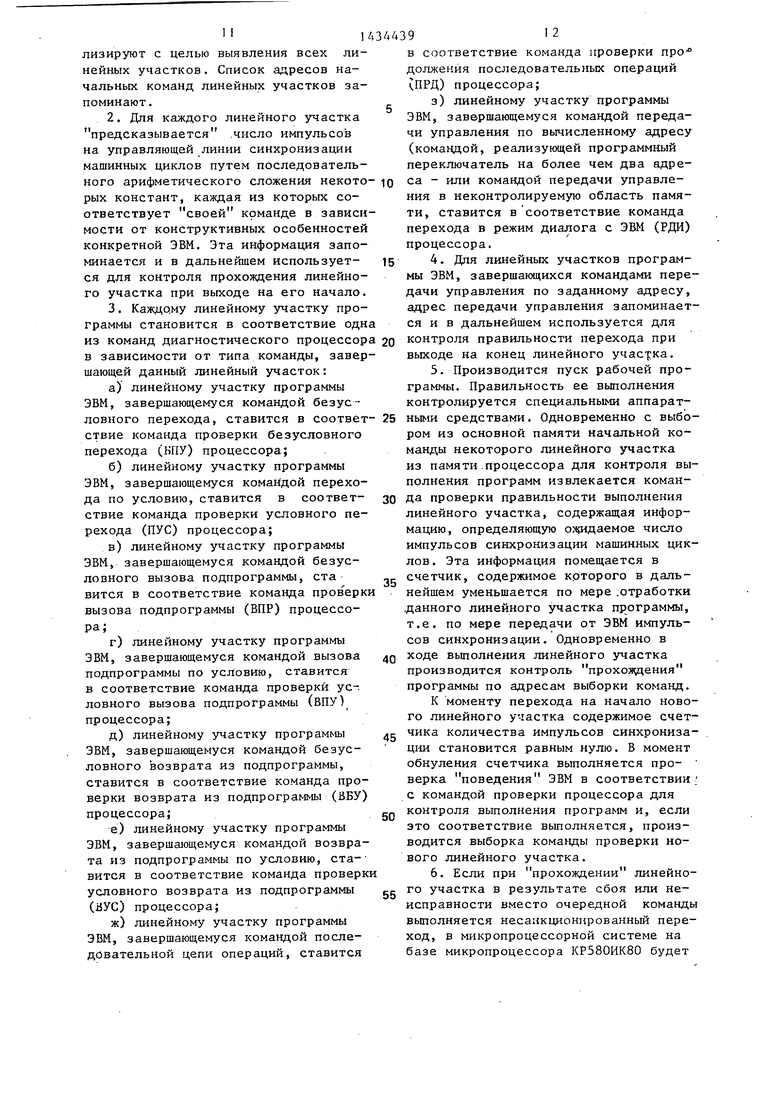

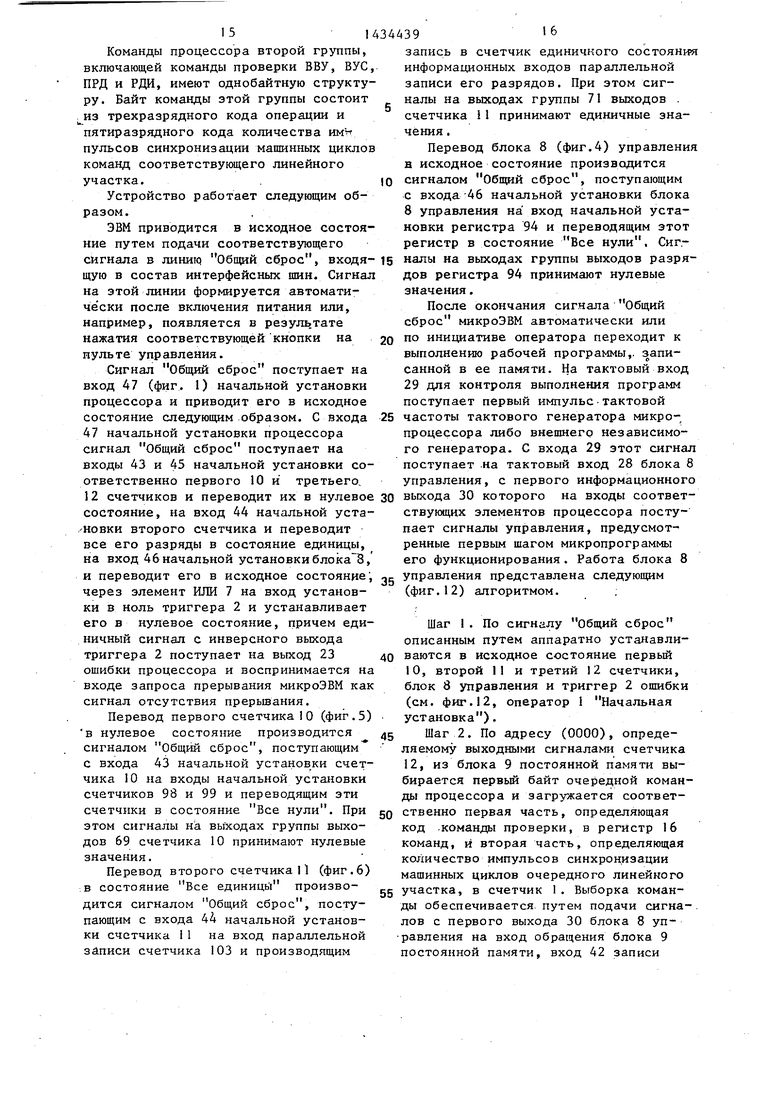

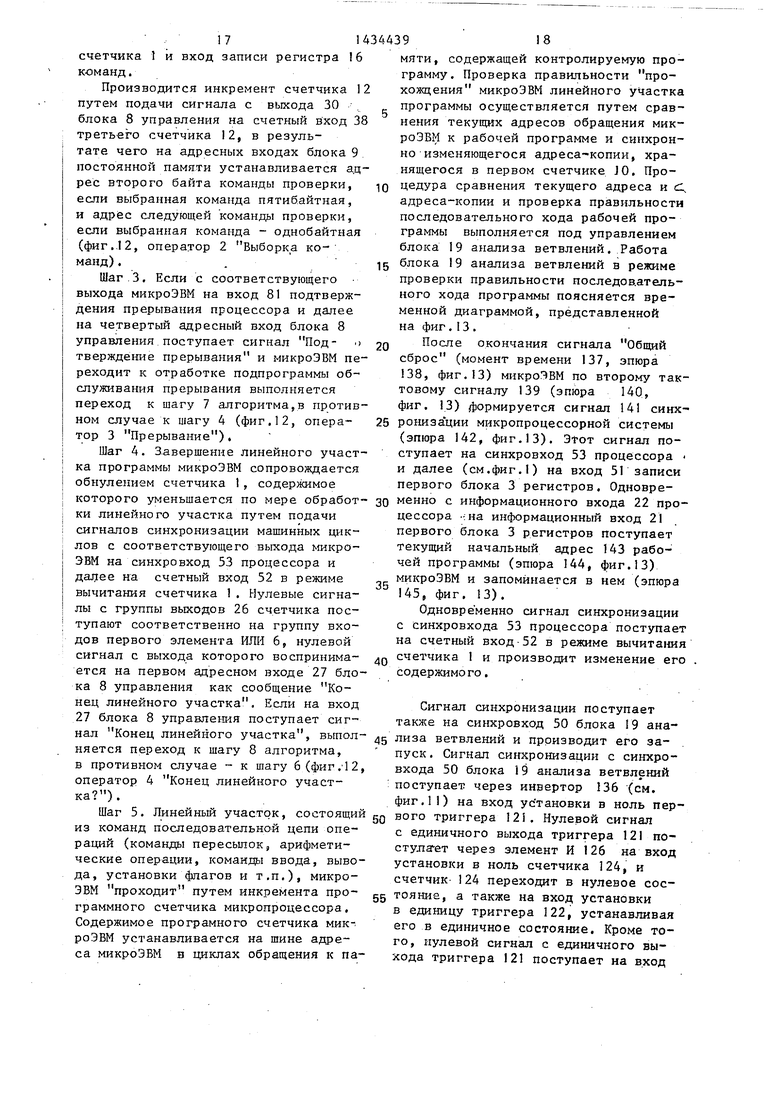

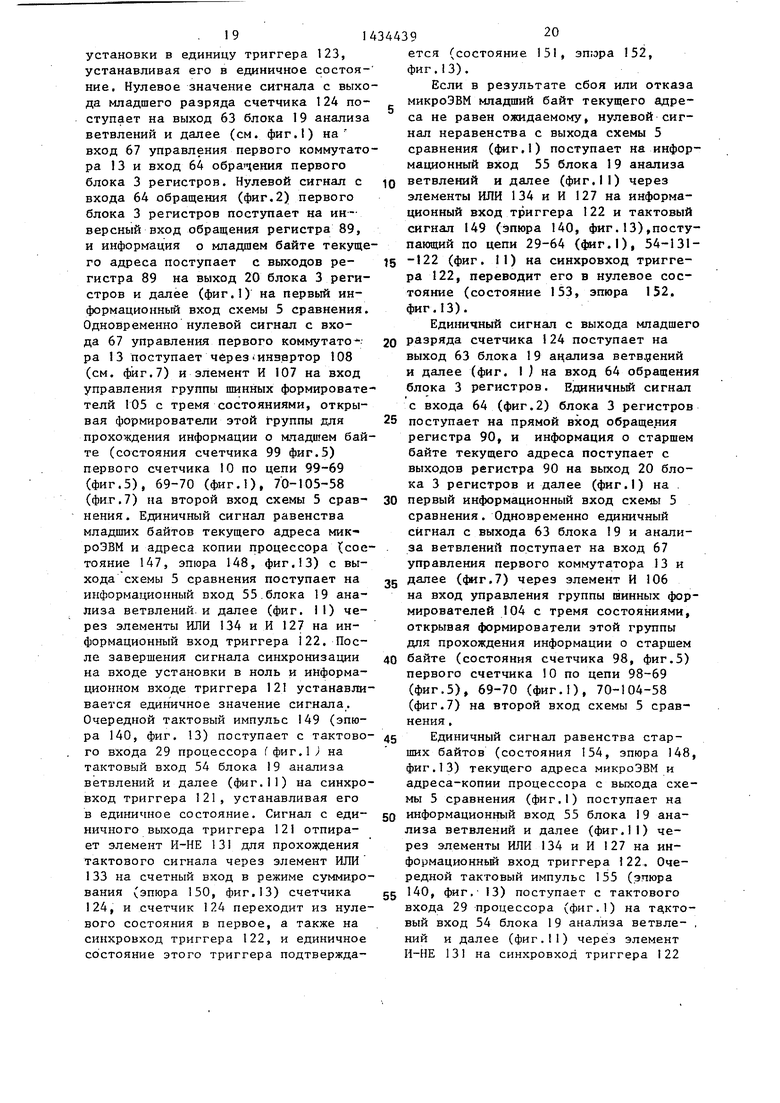

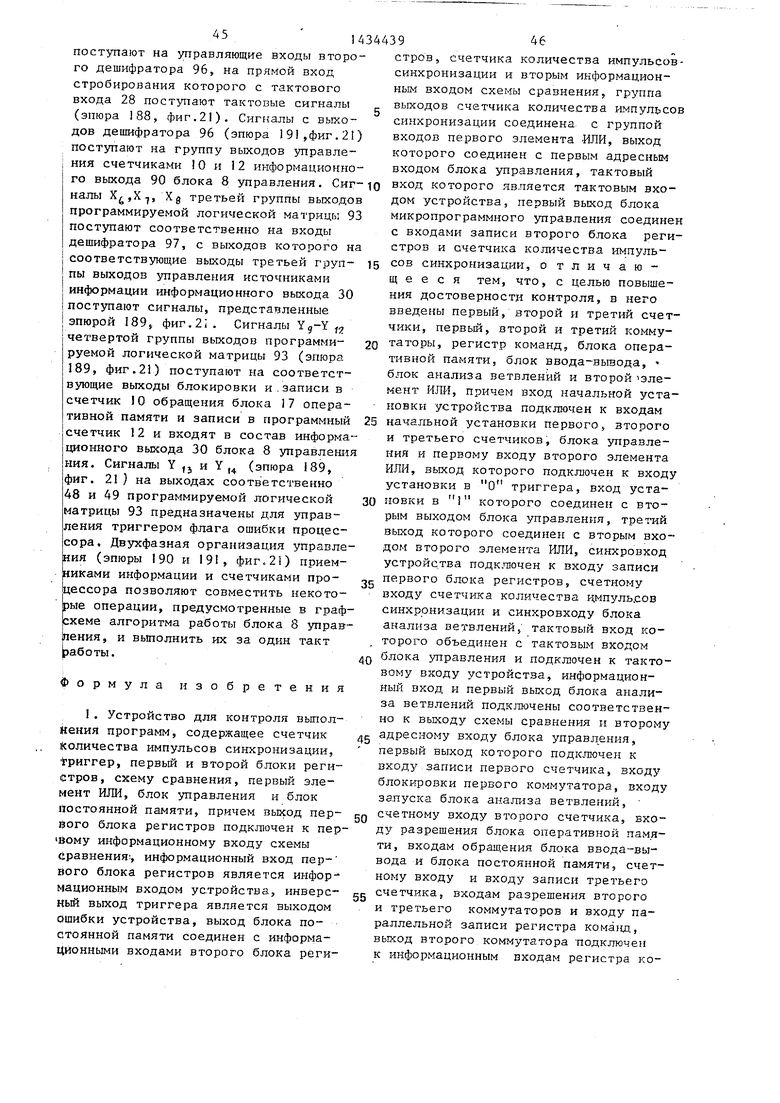

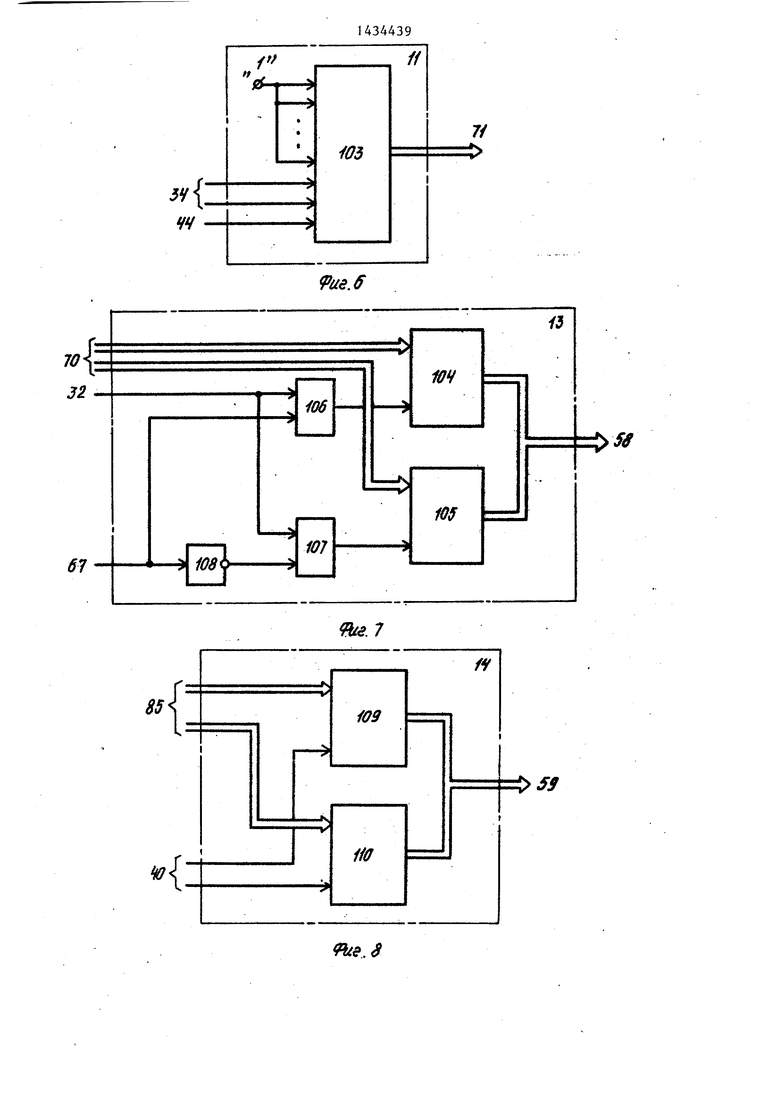

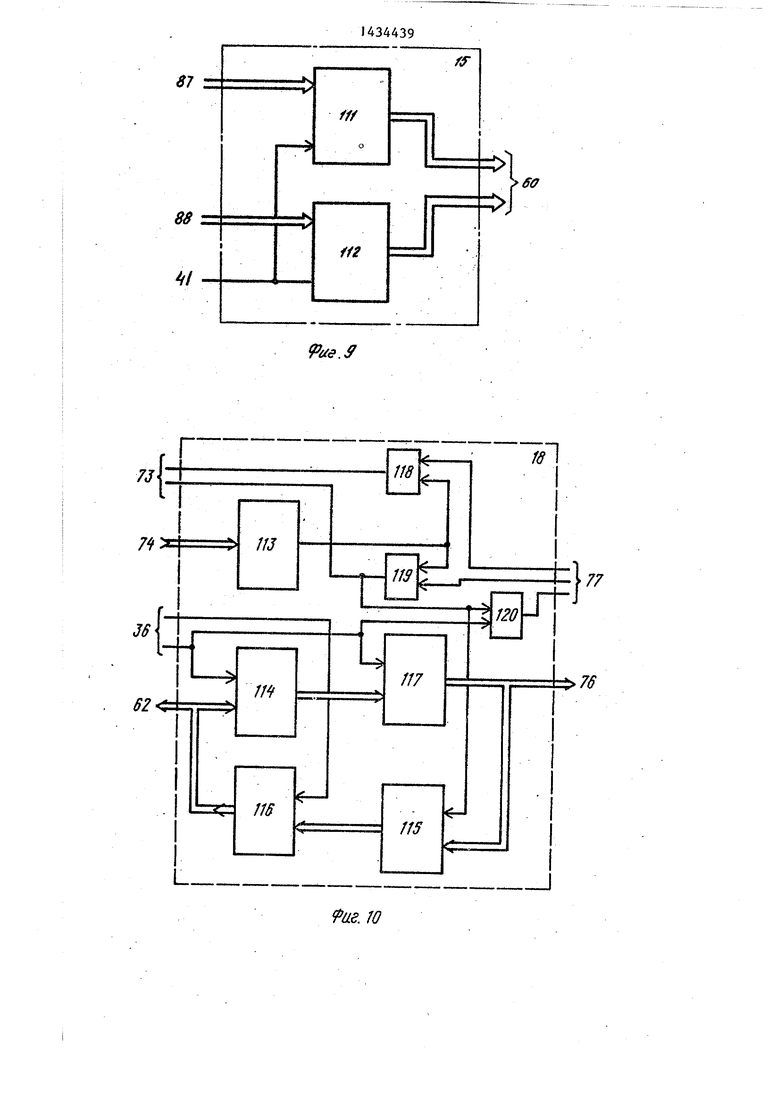

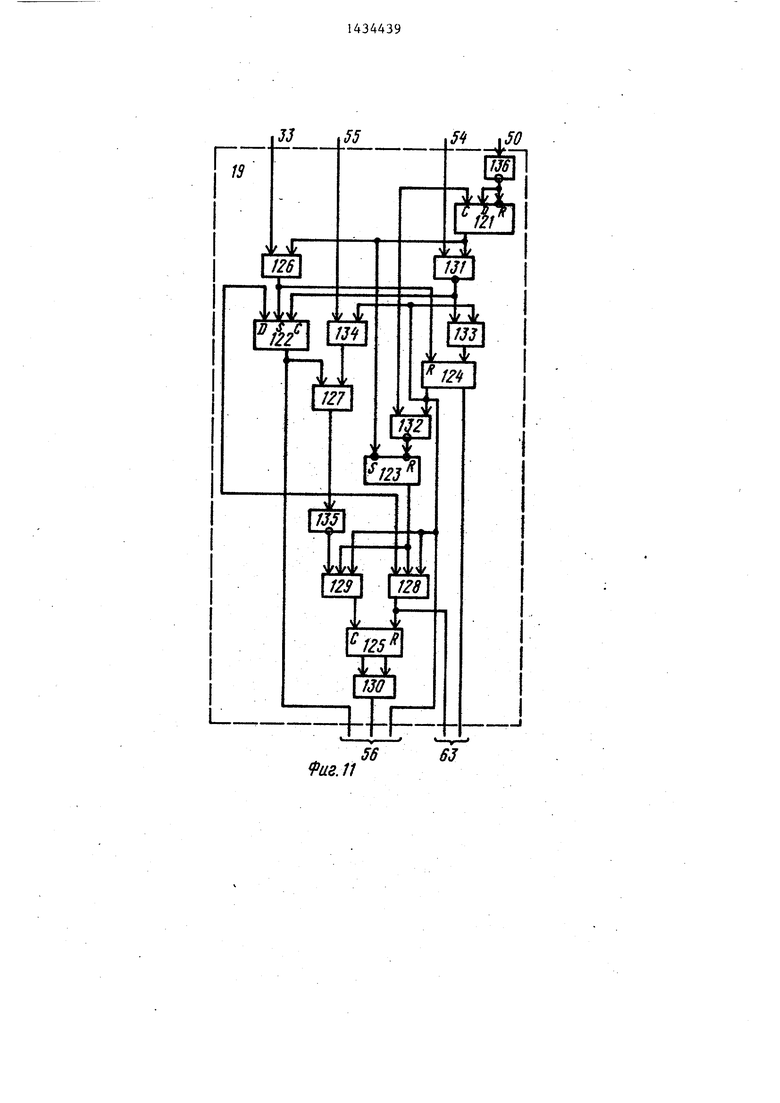

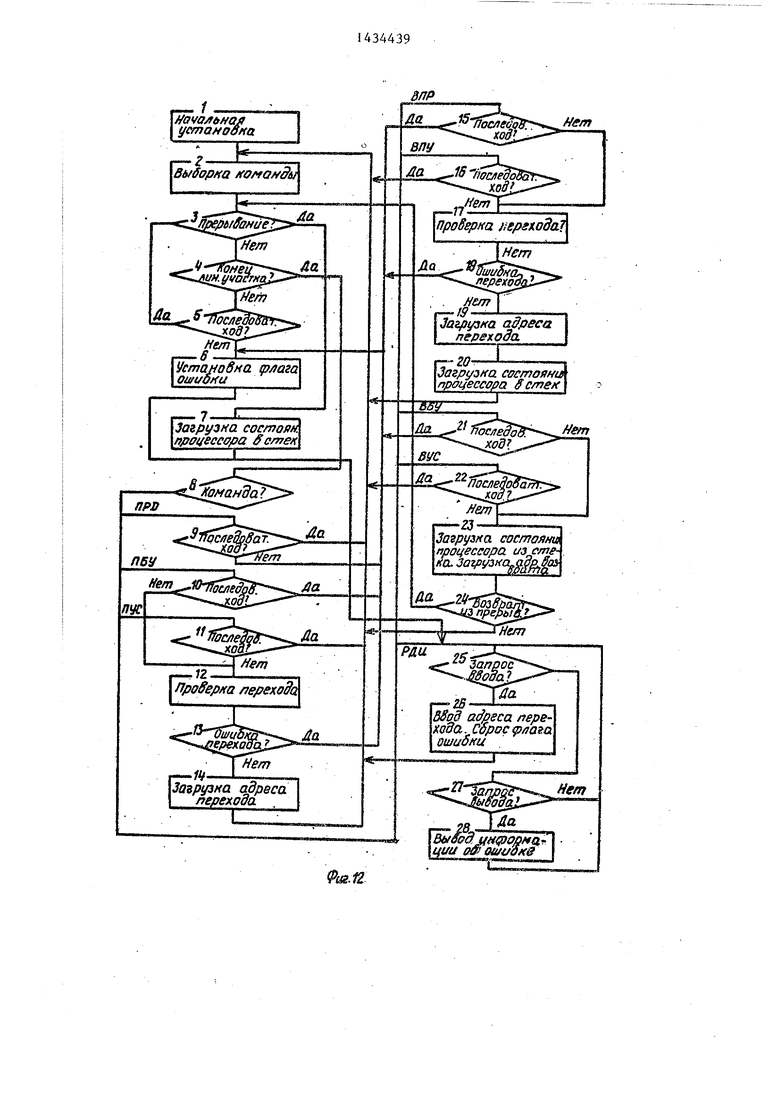

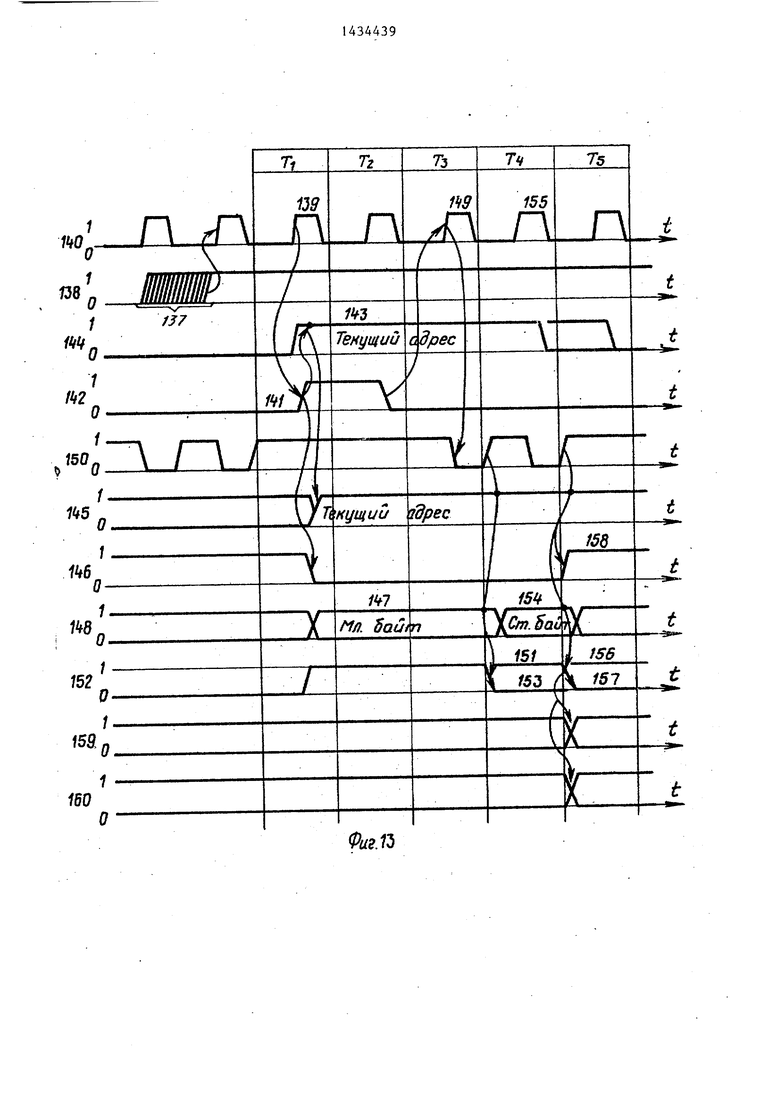

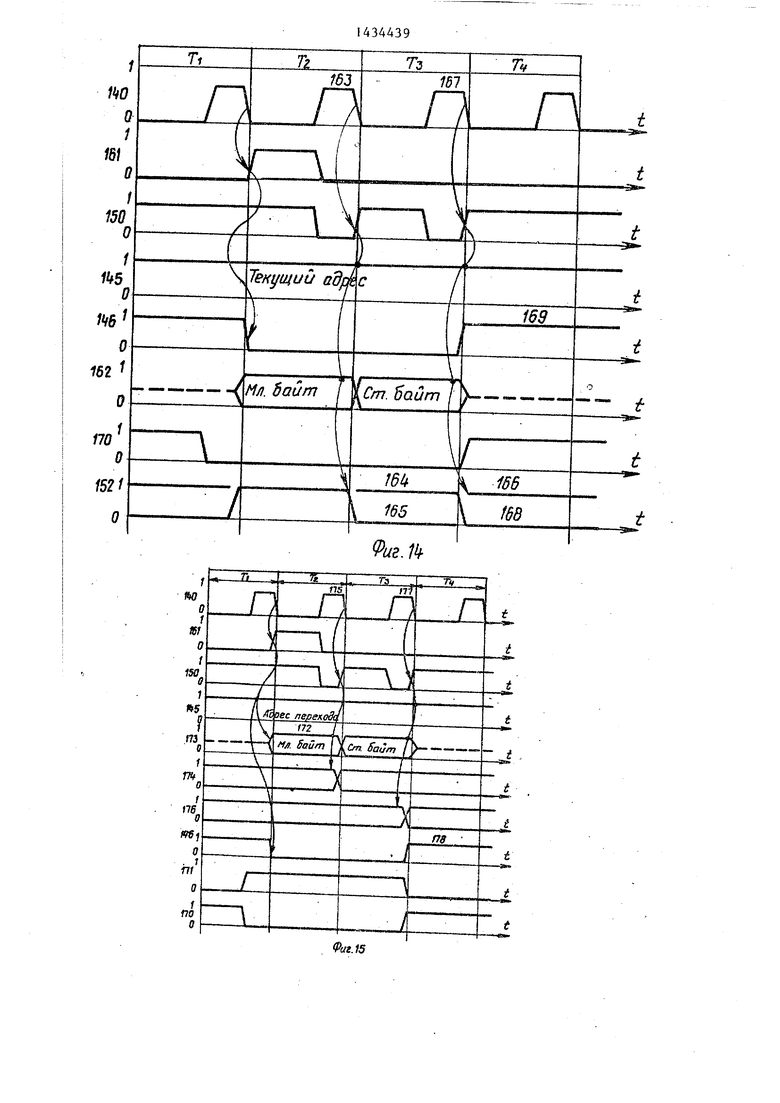

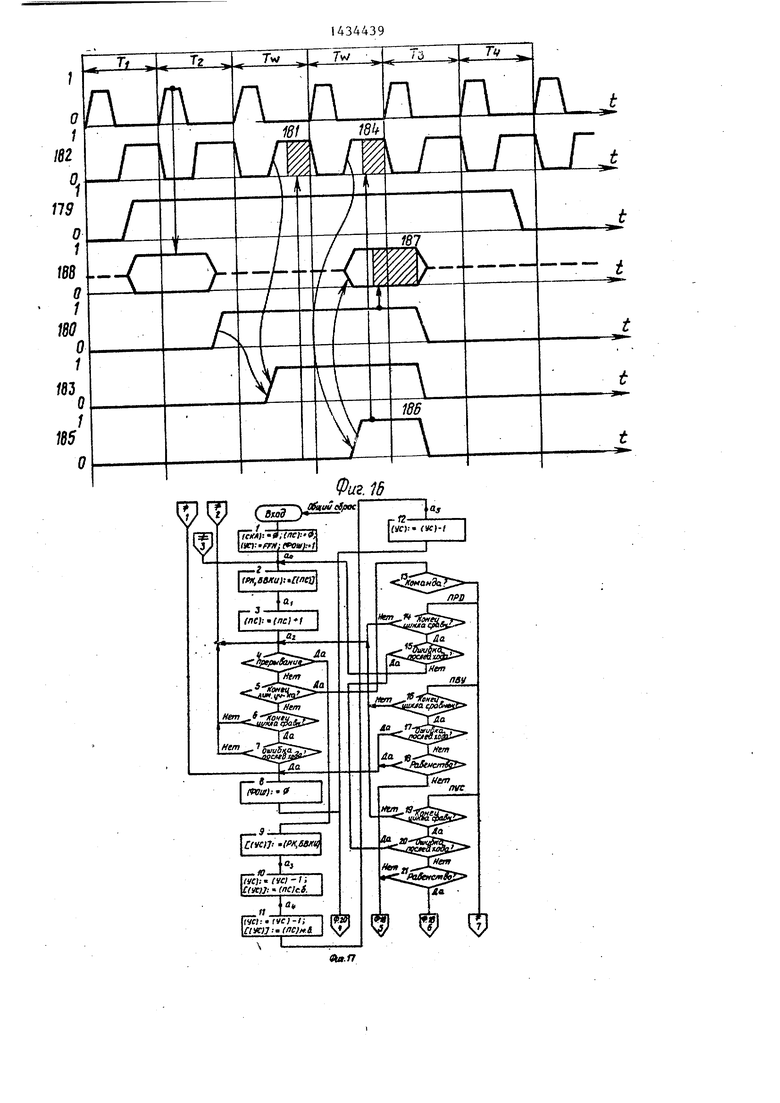

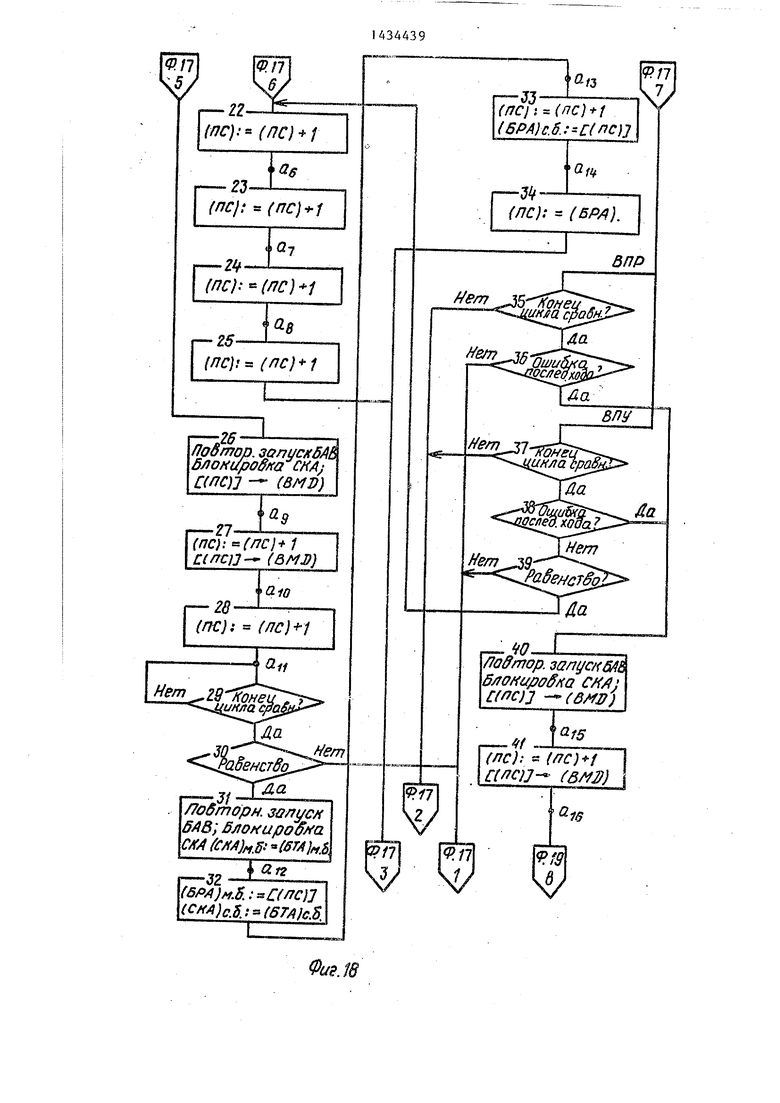

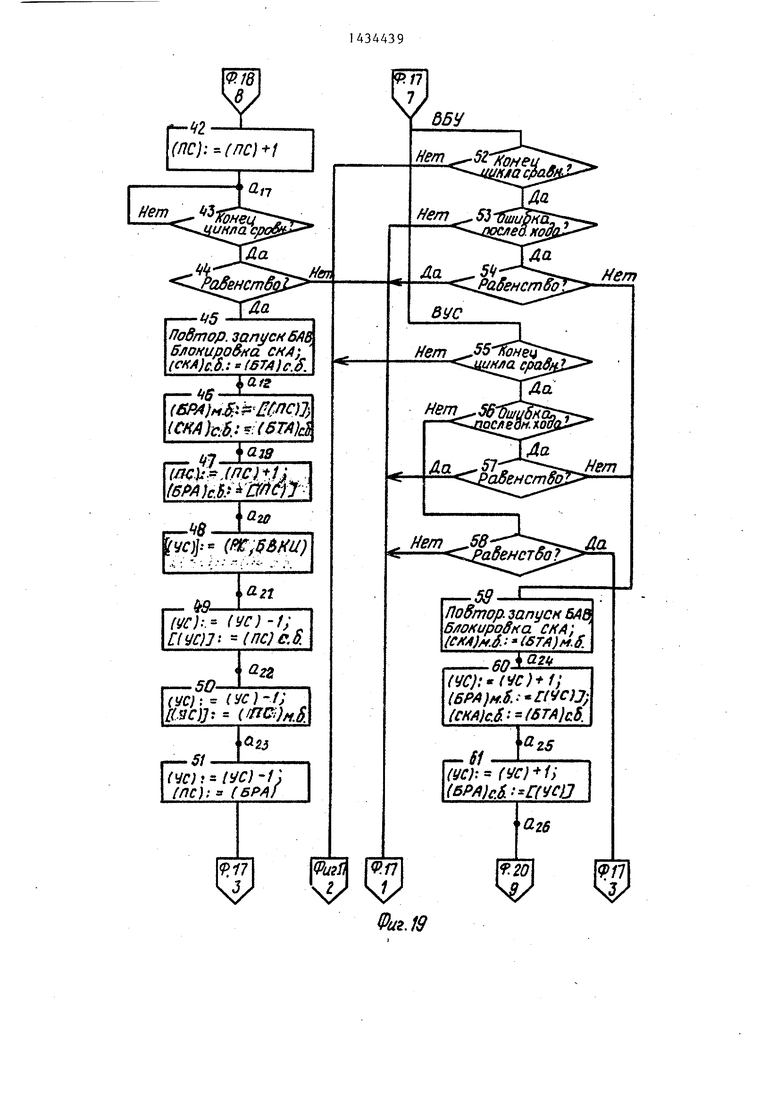

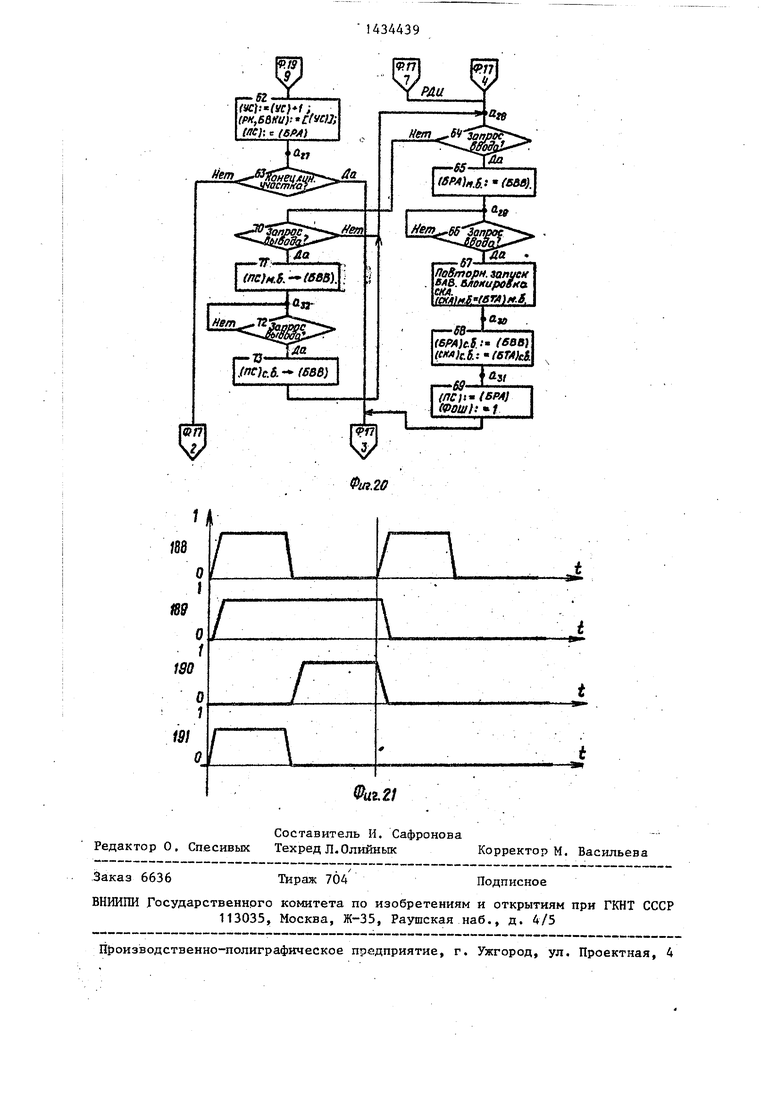

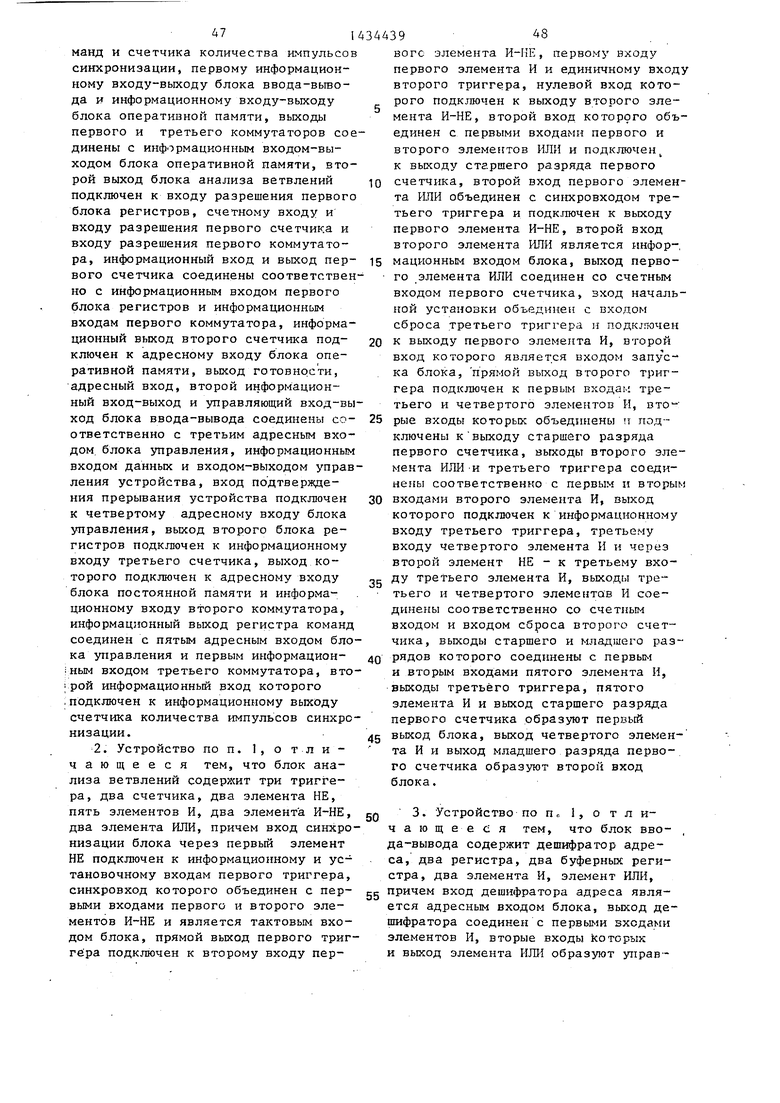

На фиг, 1 представлена функциональная схема устройства процессора для контроля выполнения программ; на фиг. 2-10 - примеры реализации функциональных узлов устройства для контроля выполнения программ микропроцессорной системы ца базе микропроцессора КР58РИК80; на фиг.2 - функциональная схема первого блока регистров; на фиг. 3 - функциональная схема второго блока регистров; на фиг. 4 - функциональная схема блока управления; на фиг. 5 - функциональная схема первого счетчика; на фиг. 6 - функциональная схема второго счетчика; на фиг. 7 - функциональная схема первого коммутатора; на фиг,8 - функциональная схема вто- рогр коммутатора; на фиг. 9 - функциональная схема третьего коммутатора; на фиг. 10 - функциональная схема блока ввода-вьшода; на фиг. П - функциональная схема блока анализа ветвлений; на фиг. 12 - граф-схема алгоритма функционирования блока управления ; на фиг. 13 - п временная . диаграмма выполнения процессором проверки правильности прямого хода про граммы МИКРОЭВМ; на фиг. 14 -временная диаграмма выполнения процессором проверки правильности перехода микро ЭВМ; на фиг. 15 - временная диаграмма выполнения процессором записи адреса перехода микроЭВМ; на фиг. 16 - временная диаграмма, поясняющая работу процессора в режиме вывода в мик- роЭВМ информации об ошибке; нафиг. 20 - праф-схема алгоритма . работы блока управления; на фиг. 21 - временная диаграмма сигналов на информационных выходах блока управления.

Устройство для контроля выполнени программ (фиг.1) содержит счетчик 1 количества импульсов синхронизации, триггер 2, первьш 3 и второй 4 блоки регистров, схема 5 сравнения, пер- вьй 6 и второй 7 элементы ИЛИ, блок 8 упрабдения, блок 9 постоянной памя

5

0

5

0

5

0

5

0

S

тн, первый 10, второй 11 и третий 12 счетчики, первый 13, второй 14 и третий 15 коммутаторы, регистр 16 команд, блок 17 оперативной памяти, блок 18 ввода-вывода и блок 19 анализа ветвлений. Информационный выход 20 первого блока 3 регистров соединен с первым информационным-входом схемы 5 сравнения, информационный вход 21 первого блока 3 регистров является информационным входом 22 процессора, инверсный выход триггера 2 является выходом 23 ошибки процессора, выход блока 9 постоянной памяти соединен ,с информационным входом 24 второго блока 4 регистров, входом 25 счетчика 1 и вторым информационным входом схемы 5 сравнения. Группа выходов 26 счетчика 1 соединена соот-;( ветственно с группой входов первого элемента ИЛИ 6, выход которого соединен с первым адресным входом 27 блока В управления, тактовый вход 28 блока 8 управления является тактовым входом 29 процессора, первый управ-; ляющий выход 30 блока 8 управления соединен с входом 31 записи первого 10 счетчика, входом 32 блокировки первого коммутатора 13, входом 33 повторного запуска блока 19 анализа ветвлений, счетным входом 34 второго счетчика 11, входом 35 записи блока 17 оперативной памяти, входом 36 обращения блока 18 ввода-вывода, входом 37 записи второго блока 4 регистров, счетным входом 38 и входом 39 записи третьего счетчика 12, входами 40 управления второго 14 и 41 третьего 15 коммутаторов, а также с входами 42 записи счетчика 1 и регистра 16 команд, и входом обращения блока 9 постоянной памяти. Первый вход второго элемента ИЛИ 7 соединен с входами 43-46 начальной установки соответственно первого 10, второго 11, третьего 12 счетчиков, блока 8 управления и является входом 47 начальной установки устройства. Выход второго элемента ИЛИ 7 подключен к входу установки в ноль триггера 2, вход установки в единицу которого соединен с вторым информационным выходом 48 блока 8 управления, третий информационный выход 49 которого соединен с вторым входом второго элемента ИЛИ 7, Вход 50 синхронизации блока 19 анализа ветвлений соединен с входом 51 записи первого 3 блока

регистров и счетным входом 52 счетчика I и является синхровходом 53 устройства. Тактовый 54, информационный 55 входы и первый выход 56 блока 19 анализа ветвлений подключены соответственно к тактовому входу 28 блока 8 управления, выходу схемы 5 сравнения и второму адресному входу 57 блока 8 управления. Выход блока 9 постоянной памяти через магистраль соединен с информационным выходами 58-60 соответственно первого 13, в второго 14, третьего 15 коммутаторов информационным входом регистра I6 команд, информационным входом-выходом 61 блока 17 оперативной памяти и первым информационным входом-выходом 62 блока 18 ввода-вывода. Второй выход 63 блока 19 анализа ветвлений подключен к входу 64 обращения первого блока 3 регистров, счетному входу 65 и входу 66 обращения первого счетчика 10 и входу 67 управления первого коммутатора 13. Информационный вход 68 и выход 69 первого счетчика 10 соединены соответственно с информационным выходом 20 первого блока 3 регистров и с информационным входом 70 первого коммутатора 13, Информационный вьпсод 71 второго счетчика 11 подключен к адресному входу

72блока 17 оперативной памяти. Выход

73готовности и адресный вход 74 блока 18 ввода-вывода соединены соответственно с третьим адресным входом 75 блока 8 управления и с информа- , ционным входом 21 первого блока 3 регистров, а второй информационный вход-выход 76 и вход-выход 77 управления блока 18 ввода-вывода являются соответственно входом-выходом 78 данных и входом-выходом 79 управления устройства. Четвертый адресный вход 80 блока 8 управления является входом 81 подтверждения прерывания устройства. Информационный выход 82 второго блока 4 регистров соединен с информационным входом 83 третьего счетчика 12, информационный выход 84 которого подключен к адресному входу блока 9 постоянной памяти и информационному входу 85.второго коммутатора 14, Информационный выход регистра 16 команд соединен с пятым адресным входом 86 блока 8 управле- ния и с первым информационным входом 87 третьего коммутатора 15, второй информационный вход 88 которого под0

5

0

5

0

5

0

5

0

5

ключей к информационному выходу 26 ° счетчика 1, Счетчик 1 количества импульсов синхронизации является пятиразрядным двоичным счетчиком, информационные входы параллельной записи которого объединены и являются информационным входом 25 счетчика 1, выходы разрядов счетчика являются группой 26 выходов счетчика, вход 42 записи которого является входом параллельной записи счетчика, а счетный вход 52 счетчика I является счетным входом в режиме вычитания 1 счетчика 1,

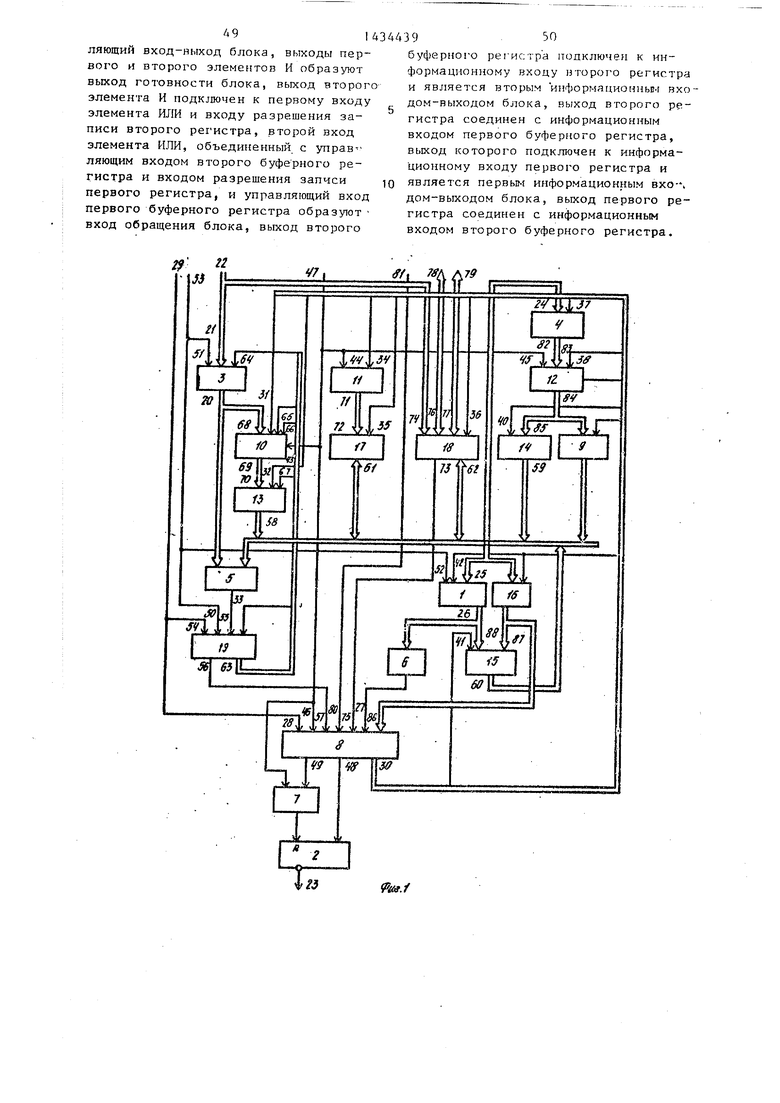

Первый блок 3 регистров (фиг,2) содержит восьмиразрядные регистры 89 и 90, информационные входы которых объединены и являются шестнадцатиразрядным информационным входом 21 первого блока 3 регистров, синхро ходы регистров 89 и 90 соединены и являются входом 51 записи первого блока 3 регистров, одноименные выходы регистров 89 и 90 соответственно соединены и являются восьмиразрядным информационным выходом 20 первого блока 3 регистров, а инверсный вход обращения регистра 89 соединен с прямым входом обращения регистра 90 и является входом 64 обращения первого блока 3 регистров.

Второй блок 4 регистров (фиг,3) содержит восьмиразрядные регистры 91 и 92, информационные входы которых соответственно соединены и .являются восьмиразрядным информационным входом 24 второго блока 4 регистров, информационные выходы регистров 91 и 92 объединены и являются шестнадцатиразрядным информационным выходом 82 второго блока 4 регистров, входы параллельной записи регистров 91 и 92 объединены и являются входом 37 записи второго блока 4 регистров.

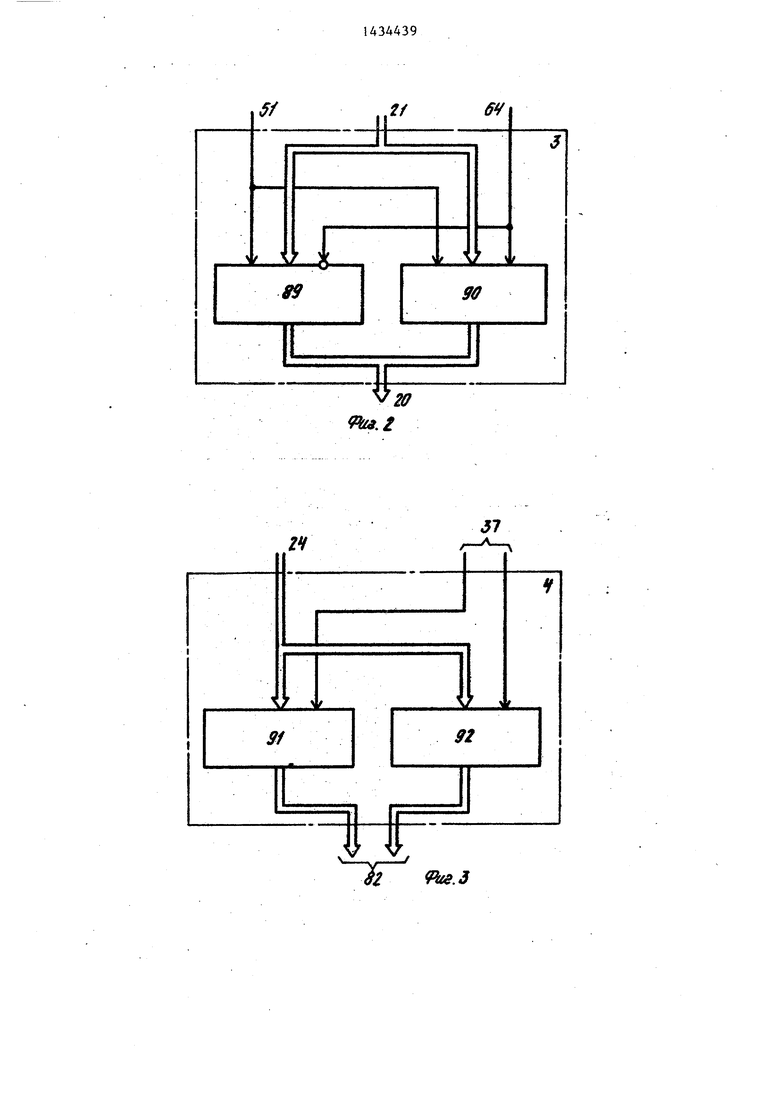

Блок 8 управления (фиг,4) содержит программируемую логическую матрицу 93, пятиразрядный регистр 94, первьй 95, второй 96 и третий 97 дешифраторы, первый вход программируемой логической матрицы 93 является -первым адресным входом 27 блока 8 управления, второй, третий и четвертый входы программируемой логической матрицы 93 объединены и являются вторым адресным входом 57 блока, пятый и шестой входы программируемой логической матрицы 93 объединены и являются третьим адресным входом 75 блока седьмой вход программируемой логической матрицы 93 является четвертым адресным входом 80 блока, восьмой, девятый и десятый входы программируемой логической матрицы 93 объединены и является пятым адресным входом 86 блока, одиннадцатый вход программируемой логической матрицы 93 соединен с входом начальной установки регистра 94 и является входом 46 начальной установки блокаj двенадцатый, тринадцатый, четырнадцатый, пятнадцатый и шестнадцатый входы программируемой логической матрицы подключены соответственно к группе информационных выходов регистра 94, первьй, второй и третий выходы программируемой логической.матрицей 93 соединены соответственно с группой управляющих входов первого дешифратора 95, инверсный вход обращения которого является тактовым входом 28 блока и соединен с входом обращения программируемой логической матрицы 93 входом параллельной записи регистра 94 и прямым входом обращения второго дешифратора 96, группа управляющих входов которого подключена к четвертому и пятому выходам программируемой логической матрицы 93, шестой, седьмой и восьмой выходы которой соединены с группой управляющих входов третьего дешифратора 97, группы выходов первого 95, второго 96 и третьего 97 дешифраторов, девятый, десятый, одиннадцатый и двенадцатый выходы программируемой логической матрицы 93 объединены и являются первым информационным выходом 30 блока, тринадцатый и четырнадцатый выходы программируемой логическо матрицы 93 являются соответственно вторым 48 и третьим 49 информацион- ными выходами программируемой логичес кой матрицы 93, пятнадцатый, шест- надцатый, семнадцатьй, восемнадцатый и девятнадцатый выходы которой соединены с группой информационных входов регистра 94.

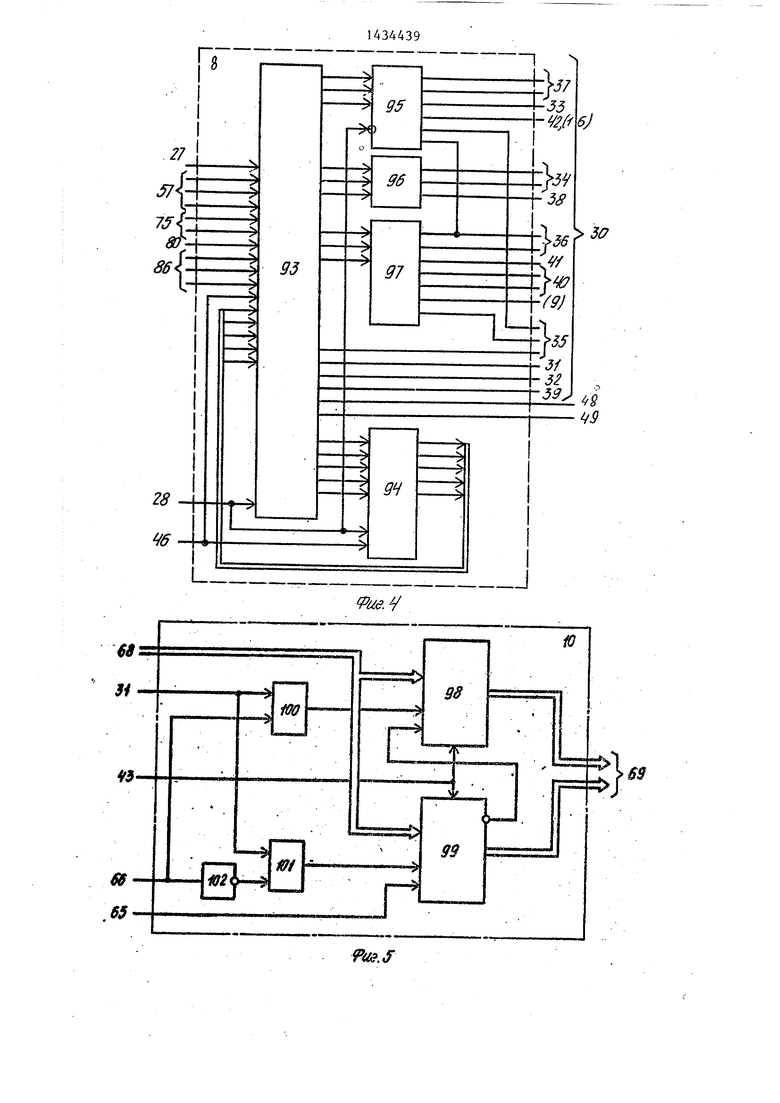

Первый.счетчик 10 (фиг. 5 ) содержит восьмиразрядные двоичные счетчики 98 и 99, первый 100 и второй 101 элементы И и инвертор 102, информационный вход параллельной записи счетчика 98 соединен с информационным входом параллельной записи второго счетчика 99 и является восьмиразрядным информационным входом 68

5

0

5

0

5

0

5

0

5

первого счетчика 10, информационные выходы счетчиков 98 и 99 образуют шестнадцатиразрядный выход 69 первого счетчика 10, вход начальной установки счетчиков 98 и 99 соединен с входом 43 начальной установки первого счетчика 10, вход параллельной записи счетчика 98 подключен к выходу элемента И 100, первый вход которого соединен с первым входом второго элемента И 101 и является входом 31 записи первого .счетчика 10, второй вход первого элемента И 100 является входом 36 обращения первого счетчика 10 и подключен через инвертор 102 к второму входу второго элемен- та И 101, выход которого соединен с входом параллельной записи второго счетчика 99, счетный вход счетчика 98 подключен к выходу прямого переноса счетчика 99, счетный вход которого является счетным входом 65 первого счетчика 10.

Второй счетчик II (фиг.6) является восьмиразрядным двоичным счетчиком 103i информационные входы параллельной записи которого соединены с шиной единичного потенциала, информационные выходы счетчика 103 являются информационным выходом 71 первого счетчика 11, вход параллельной записи очетчика 103 является входом 44 начальной установки второго счетчика 11, а счетные входы суммирования +1 и вычитания -I счетчика 103 и являются счетным входом 34 второго счетчика 11.

Третий счетчик 12 является шестг , надцатиразрядным -двоичным счетчиком, имеющим входы 45 начальной установки, 39 параллельной записи, счетный вход 38, шестнадцатиразрядный информационный вход 83 параллельной записи и шестнадцатиразрядный информационный выход 84.

Первый коммутатор 13 (фиг.7) со- дерлсит первую 104 и вторую 105 группы из восьми шинных формирователей с стремя состояниями, первый 106 и второй 107 элементы И и инвертор 108, информационные Входы шинных формиро-, ваталей первой 104 и второй 105 групп являются Шестнадцатиразрядным информационным входом 70 первого коммутатора 13, выходы пшнных формирователей первой I04 и второй 105 групп соответственно соединены и являются восьмиразрядным выходом 58 первого

коммутатора 13, управлякщие входы шинных формирователей первой группы 104 соединены с выходом первого элемента И 106, первый вход которого соединен с первым входом второго элемента И 107 и является входом 32 блокировки первого коммутатора 13, второй вход первого элемента И 106 является входом 67 управления первого коммутатора I3 и соединен через инвертор 108 с вторым входом второго элемента И 107, выход которого подключен к входам управления шинных формирователей второй группы 105.

Второй коммутатор 14 (фиг.8) содержит первую 109 и вторую 110 группы из восьми шинных формирователей с тремя состояниями, выходы шинных формирователей первой 109 и второй 110 групп соответственно соединены и являются восьмиразрядным информационным выходом 59. второго коммутатора 14, информационные входы шинных формирователей первой 109 и второй 110 групп объединены и являются шестнадцатиразрядным информационным входом 85 второго коммутатора 14, управляющие входы шинных формирователей первой 109 и второй 110 группы объединены и являются входом 40 управления второго коммутатора 14.

Третий коммутатор 15 (фиг.9) содержит первую группу 1П из трех и вторую группу 112 из пяти шинных формирователей с тремя состояниями, информационные выходы которых и являются восьмиразрядным информационным выходом 60 третьего коммутатора 15, управляющие входы шинных формирователей первой 111 и второй 112 групп соединены и являются входом 41 управления третьего коммутатора 15, а информационные входы шинных формирователей первой 111 и второй 112 групп соответственно являются первым 87 и вторым 88 информационными входами третьего коммутатора 15.

Блок 18 ввода-вывода (фиг.10) содержит дешифратор 113 адреса, первый 114 и второй 115 восьмиразрядные регистры, первый 116 и второй 117 восьмиразрядные буферные регистры, первый 118 и второй элементы И 119 и элемент ИЛИ 120, группа из шестнадцати (восьми ) входов дешифратора 113 адреса является адресным входом 74 блока 18 ввода-вывода, выход дешифратора 113 адреса соединен с

первыми входами первого J 18 и второ-о го 119 элементов И, группа информационных входов параллельной записи первого регистра 114 соответственно соединена с группой выходов первого буферного регистра 16 и является первым информационным входом-выходом 62 блока 18 ввода-вывода, вход

Q параллельной записи первого регистра 114 и управляющий вход первого буферного регистра 116 объединены и являются входом 36 обращения блока 18 ввода-вывода, выходы первого 118

5 и второго 119 элементов И объединены и являются выходом 73 готовности блока 18 ввода-вывода, группа информационных выходов первого регистра 114 соответственно соединена с груп0 пой информационных входов второго буферного perijcTpa 117, управляюп| ий вход которого подключен к входу па- раллельной записи регистра 114 и к первому входу элемента ИЛИ 120, вто5 рой вход которого соединен с выходом второго элемента И 119 и с входом параллельной записи второго регистра 115, группа выходов которого соот.- . зетственно соединена с группой инфор0 мационных входов первого буферного

регистра 116, группа информационных . входов параллельной записи второго регистра 115 соответственно соединена с группой выходов второго буферного регистра 117 и является вторым инфор- мацион1шм входом-выходом 76 блока 18 ввода-вывода, а выход элемента И.Г1И 120 и вторые входы первого 118 и второго 119 элементов И объединены и

0 являются входом-выходом 77 управления блока 18 ввода-вывода.

Блок 19 анализа ветвлений (фиг. 1) содержит первый 121, второй 122 и третий 123 триггеры, первый 124 и

5 второй 125 двухразрядные счетчики, первый 126, второй 127, третий 128, четвертый 129 и пятый 130 элементы И, первый 131 и второй 132 элементы И-НЕ, первый 133 и второй 134 элеменQ ты ИЛИ и первый 135 и второй 136 инверторы, вход установки в ноль и информационный вход первого триггера 12 соединены и подключены к выходу второго инвертора 136, вход которого

g является синхровходом 50 блока 19 анализа ветвлений, синхровход первого триггера 121 является тактовым входом 54 блока 19 анализа ветвлений и соединен с nepBMNm входами пер5

вого 131 и второго 132 элементов И-НЕ, единичный выход первого триггера 121 соединен с вторым входом первого элемента И-НЕ 132, первым входом первого элемента И 1 26 и входом установки -в единицу третьего триггера . : 1-23, выход первого элемента И-НЕ 131 подключен к первому входу первого элемента ИЛИ 133 и к синхровходу второго триггера 122, вход установки в единицу которого соединен с входом начальной установки первого счетчика 124 и с выходом первого элемента PI 126, второй вход которого является входом 33 повторного запуска блока 19 анализа ветвлений, первый вход второго элемента ИЛИ.134 является информационным входом 55 блока 19 анализа ветвлений, вторые входы первого 133 и второго 134 элементов ИЛИ, второго элемента И-НЕ 132 и первые входы третьего 128 и четвертого 129 элементов И соединены с информационным выходом старшего разряда первого Счет чика 124, выходы первого 133 и второго 134 элементов ИЛИ подключены соответственно к счетному входу в режиме суммирования первого счетчика 124 и к первому входу второго элемента И 127, второй вход которого соединен с единичным выходом второго триггера 122, выход второго 127 элемента И подключен к информационному входу второго триггера 122, второму входу третьего элемента И 128 и через инвертор 135 к второму входу четвертого элемента И 129, выход второго элемента И-НЕ соединен с нулевым входом тре тьего триггера 123, едишмный выход которого соединен с третьими входами третьего-128 и четвертого элементов И 129, выходы которых подключены со- ответственно к входу начальной уста-, новки и счетному входу в режиму суммирования второго счетчика 125, инфор мационные выходы которого соединены соответственно с первым и вторым входами пятого элемента И 130, информационный выход младшего разряда первого счетчика 124 и выход третьего элемента И 128 объединены и являются вторым выходом 63 блокд 19 анализа ветвлений, а единичный выход второго триггера 122, информационный выход старшего разряда первого счетчика 124 и выход пятого элемента И 130 объединены и являются первым выходом 56 блока 19 анализа ветвлений.

Любую программу, записанную в машинах кодах в памяти ЭВМ, можно представить в виде набора линейных участков, связанных между собой командами передачи управления. Команда пёре- дачи управления является завершающей командой линейного участка, если он не последний линейный участок программы - в этом случае линейный участок может завершаться, например, ко- мандой Останов . Начальный командой линейного участка может быть либо команда, являющаяся внешним входом

программы, либо команда, на которую производится передача управления одной из команд перехода. Если некоторый линейный участок программы содержит несколько начальных команд (точек вхождения), то он может рассматриваться как цепь из нескольких ли- нейньгх участков, каждый из которых имеет одну начальную команду. В этом случае конечной командой любого зве на цепи, кроме посдеднего, является

команда, предшествующая начальной команде следующего звена.

Таким образом, любую программу можно разбить на отдельные линейные

участки, на которых поведение ЭВМ строго детерминированно, в том смысле, что при правильном прохождении ЭВМ через данный линейный участок программы на заправляющей линии синх-г

ронизации машинных циклов должно быть зарегистрировано строго определенное число импульсов, которое известно для каждого линейного участка еще до начала работы ЭВМ по программе. Это утНерадение остается справедливым и тогда, когда процесс прохождения данного участка временно приостанавливается в связи с реакцией на внешние прорраммно-независимые события (прерывания). В этих случаях используется стековый механизм запоминания и восстановления необходимой информации. Следование сигналов синхрониза ции машинных циклов, которыми сопровождается вьтолнение команд передачи управления, не зависит от того, вы- полнеао ли проверяемое условие или нет.

Основную идею работы устройства

для контроля выполнения программ можно выразить следующим образом.

1. После (или в процессе) трансляции исходной программы на язык машинных команд рабочую программу анализируют с целью выявления всех линейных участков. Список адресов начальных команд линейных участков запоминают.

2.Для каждого линейного участка предсказывается .число импульсов на управляющей линии синхронизации машинных циклов путем последовательного арифметического сложения некото- рых констант, каждая из которых соответствует своей команде в зависимости от конструктивных особенностей конкретной ЭВМ, Эта информация запоминается и в дальнейшем использует- ся для контроля прохоядения линейного участка при выходе на его начало.

3.Каждому линейному участку программы становится в соответствие одна из команд диагностического процессора в зависимости от типа команды, завершающей данный линейный участок:

а)линейному участку программы ЭВМ, завершающемуся командой безусловного перехода, ставится в соответ- ствие команда проверки безусловного перехода (КПУ) процессора;

б)линейному участку программы ЭВМ, завершающемуся командой перехода по условию, ставится в соответ- ствие команда проверки условного перехода (ПУС) процессора;

в)линейному участку программы ЭВМ, завершающемуся командой безусловного вызова подпрограммы, ста

вится в соответствие команда проверк вызова подпрограммы (ВПР) процессора;

г)линейному участку программы

ЭВМ, завершающемуся командой вызова подпрограммы по условию, ставится в соответствие команда проверки ус-. ЛОБНОГО вызова подпрограммы (ВПУ) процессора;

д)линейному участку программы ЭВМ, завершающемуся командой безусловного возврата из подпрограммы, ставится в соответствие команда проверки возврата из подпрограммы (ВБУ) процессора;

е)линейному участку программы ЭВМ, завершающемуся командой возврата из подпрограммы по условию, ста- вится в соответствие команда проверк условного возврата из подпрограммы (БУС) процессора;

ж)линейному участку программы ЭВМ, завершающемуся командой последовательной цепи операций, ставится

Q s

0

5

о

5

0

g Q

g

в соответствие команда проверки про-° должения последовательных операций ПРД) процессора;

з) линейному участку программы ЭВМ, завершающемуся командой передачи управления по вычисленному адресу (командой, реализующей программный переключатель на более чем два адреса - или командой передачи управления в неконтролируемую область памяти, ставится в соответствие команда перехода в режим диалога с ЭВМ (РДИ) процессора.

4.Для линейных участков программы ЭВМ, завершающихся командами передачи управления по заданному адресу, адрес передачи управления запоминается и в дальнейшем используется для контроля правильности перехода при выходе на конец линейного участка.

5.Производится пуск рабочей программы. Правильность ее выполнения контролируется специальными аппаратными средствами. Одновременно с выбором из основной памяти начальной команды некоторого линейного участка

из памяти .процессора для контроля выполнения программ извлекается команда проверки правильности выполнения линейного участка, содержащая информацию, определяющую ожидаемое число импульсов синхронизации машинных циклов . Эта информация помещается в счетчик, содержимое крторого в дальнейшем уменьшается по мере .отработки данного линейного участка программы, т.е. по мере передачи от ЭВМ импульсов синхронизации. Одновременно в ходе выполнения линейного участка производится контроль прохояадения программы по адресам выборки команд.

К моменту перехода на начало нового линейного участка содержимое счетчика количества импульсов синхронизации становится равным нулю. В момент обнуления счетчика вьшолняется про- верка поведения ЭВМ в соответствии. с командой проверки процессора для контроля выполнения программ и, если это соответствие выполняется, производится выборка команды проверки нового линейного участка.

6.Если при прохождении линейного участка в результате сбоя или неисправности вместо очередной команды вьтолняется несанкционированный переход, в микропроцессорной системе на базе микропроцессора КР580ИК80 будет

131

обнаружен в третьем машинном цикле после его возникновения, что позво-t ляет организовать своевременноменную реакцию устройства.управления в случае аварийной ситуации.

Память программ контролируемой микроэвм и программируемых контроллеров выполняется в виде постоянного или полупостоянного запоминающего устройства. Вводимая в память рабоч чая программа представлена в виде по следовательности машинных кодов. Ее ввод в память микроЭВМ должен сопровождаться вводом в блок памяти процессора заранее подготовленной программы контроля вьщолненИя рабочей программы. Программа контроля также должна быть представлена в виде последовательности машинных кодов. Фор маты команд проверки, конструктивные особенности элементов схемы процесса ра и алгоритм работы блока микропрограммного управления определяются конструктивными особенностями, ин;, терфейсом и форматом команд конкрет ной микроэвм.

34439

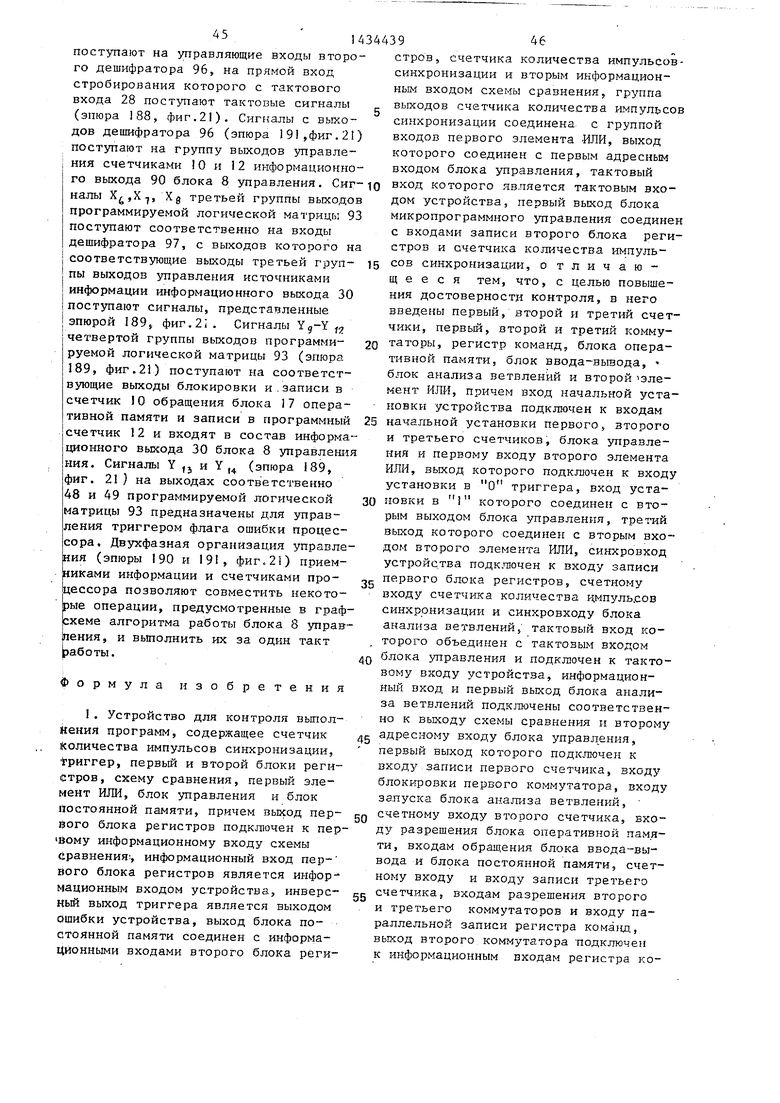

Рассмотрим построение системы конт,-. роля выполнения программ для микроЭВМ на базе микропроцессора КР580ИК80. Форматы команд проверки линейных участков представлены в таблице.

По своему формату команды процессора разделяются на две группы. Ко манды процессора первой группы, вклю- Q чающей команды проверки ПБУ, ПУС,

ВПР и ВПУ, имеют пятибайтную структуру. Первый байт комавд этой группы состоит из двух частей: трехразрядного кода операции машинных циклов 15 соответствующего линейного участка. Второй и третий байты команд этой группы являются соответственно младшим и старшим байтами адреса перехода соответствующего линейного участ- 20 Четвертый и пятый байты команд первой группы являются соответственно младшим и старшим байтами адреса пег -. рехода процессора, т.е. .адреса команды проверки программы контроля, на 25 которую передается управление при переходе к новому линейному участку рабочей программы.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для контроля выполнения программ | 1989 |

|

SU1709319A1 |

| Устройство для контроля выполнения программ (его варианты) | 1985 |

|

SU1315981A1 |

| Распределенная система управления | 1989 |

|

SU1732345A1 |

| УСТРОЙСТВО КОНТРОЛЯ ПРОЧНОСТИ КРЫЛА ВОЗДУШНОГО СУДНА | 2011 |

|

RU2469289C1 |

| Устройство для контроля хода программ | 1988 |

|

SU1617442A1 |

| Устройство для формирования команд с аппаратной организацией циклических программ | 1979 |

|

SU942018A1 |

| Устройство для отладки программ микроЭВМ | 1989 |

|

SU1815643A1 |

| Устройство для сопряжения двух магистралей | 1986 |

|

SU1348874A1 |

| Устройство для отладки программ | 1987 |

|

SU1462327A1 |

| Система ввода-вывода для микропрограммируемой ЭВМ | 1988 |

|

SU1667084A1 |

Изобретение относится к вычислительной технике и может быть.не1о пользовано для контроля выполнения программ в цифровых вычислительных машинах и программируемых контроллерах, построенных по принципу Общей магистрали. Цель изобретения - повышение достоверности контроля за ходом выполнения программ. Процессор содержит счетчики, триггер, блоки регистров, схему сравнения, элементы ИЛИ,блок управления, блок постоянной памяти, коммутаторы, регистр команд, блок оперативной памяти, блок ввода-вьюода и блок анализа ветвлений. 2 з.п. ф-лы, 21 ил., 1 табл. с (О

Проверка безусловного перехода

Проверка перехода по условию

Проверка, безуслов - ного вызова подпрограммы

Проверка вызова

подпрограммы по условию

Проверка возврата

из подпрограммы безусловного

Проверка возврата из подпрограммы по условию

Проверк а продолжения последовательности операций

Переход в режим диалога

Код команды Количество импульсов синхр.

Младший байт адреса перехода линейного участка

Старший байт адреса перехода процессора

Младший байт адреса перехода процессора

Старший байт адреса перехода процессора

Код команды Количество импульсов синхр.

Команды процессора второй группы, включающей команды проверки ВВУ, БУС, ПРД и РДИ, имеют однобайтную структуру. Байт команды этой группы состоит из трехразрядного кода операции и пятиразрядного кода количества им пульсов синхронизации машинных циклов команд соответствующего линейного участка.

Устройство работает следующим образом.

ЭВМ приводится в исходное состояПеревод блока 8 (фиг.4) управления в исходное состояние производится 10 сигналом Обпщй сброс, поступающим с входа-46 начальной установки блока 8 управления на вход начальной установки регистра 94 и переводящим этот регистр в состояние Все нули. Сиг,ние путем подачи соответствующего сигнала в линию Общий сброс, входя- 15 налы на выходах группы выходов разря- щую в состав интерфейсных шин. Сигнал дов регистра 94 принимают нулевые на этой линии формируется автоматически после включения питания или, например, появляется в результате нажатия соответствующей кнопки на пульта управления.

Сигнал Общий сброс поступает на вход 47 (фиг. 1) начальной установки

значения.

После окончания сигнала Общий сброс микроэвм автоматически или

20

по инициативе оператора переходит к выполнению рабочей программы,, записанной в ее памяти. На тактовый вход 29 для контроля выполнения программ поступает первый импульстактовой 25 частоты тактового генератора микро-, процессора либо внешнего независимого генератора. С входа 29 этот сигнал поступает .на тактовый вход 28 блока 8 управления, с первого информационного

процессора и приводит его в исходное состояние следующим образом. С входа 47 начальной установки процессора сигнал Общий сброс поступает на входы 43 и 45 начальной установки соответственно первого 10 и третьего.

12 счетчиков и переводит их в нулевое ЗО выхода 30 которого на входы соответствующих элементов процессора пос пает сигналы управления, предусмо ренные первым шагом микропрограммы его функционирования. Работа блок

состояние, на вход 44 начальной уста. Новки второго счетчика и переводит все его разряды в состояние единицы, на вход 46 начальной установки блока 8, и переводит его в исходное состояние , ос Управления представлена следующим через элемент ИЛИ 7 на вход установ- (фиг.12) алгоритмом. ; ки в ноль триггера 2 и устанавливает его в нулевое состояние, причем единичный сигнал с инверсного выхода триггера 2 поступает на выход 23 дО ошибки процессора и воспринимается на входе запроса прерывания микроЭВМ как сигнал отсутствия прерьшания.

Перевод первого счетчика О (фиг.5) .

в нулевое состояние производится сигналом Общий сброс, поступающим с входа 43 начальной установки счетчика 10 на входы начальной установки счетчиков 98 и 99 и переводящим эти счетчики в состояние Все нули. При этом сигналы на выходах группы выходов 69 счетчика 10 принимают нулевые значения.

Перевод второго счетчика 11 (фиг.6) в состояние Все единицы производится сигналом Общий сброс, посту 45

50

55

пающим с входа 4Д начальной установки счетчика I1 на вход параллельной ЗАПИСИ счетчика 103 и производящим

Шаг I . По сигналу Общий сброс описанным путем аппаратно устанав ваются в исходное состояние первы 10, второй 11 и третий 12 счетчик блок 8 управления и триггер 2 оши (см. фиг.12, оператор 1 Начальна установка).

Шаг 2. По адресу (0000), опреде ляемому выходными сигналами счетчи 12, из блока 9 постоянной памяти в бирается первьй байт очередной ком ды процессора и загружается соотве ственно первая часть, определяющая код .команды проверки, в регистр 1 команд, и вторая часть, определяющ количество импульсов синхронизации машинных циклов очередного линейно участка, в счетчик 1. Выборка кома ды обеспечивается, путем подачи сиг лов с первого выхода 30 блока 8 уп равления на вход обращения блока 9 постоянной памяти, вход 42 записи

запись в счетчик единичного состояния информационных входов параллельной записи его разрядов. При этом сигналы на выходах группы 71 выходов . счетчика i1 принимают единичные значения .

Перевод блока 8 (фиг.4) управления в исходное состояние производится сигналом Обпщй сброс, поступающим с входа-46 начальной установки блока 8 управления на вход начальной установки регистра 94 и переводящим этот регистр в состояние Все нули. Сиг,налы на выходах группы выходов разря- дов регистра 94 принимают нулевые

налы на выходах группы выходов раз дов регистра 94 принимают нулевые

значения.

После окончания сигнала Общий сброс микроэвм автоматически или

налы на выходах группы выходов разря- дов регистра 94 принимают нулевые

по инициативе оператора переходит к выполнению рабочей программы,, записанной в ее памяти. На тактовый вход 29 для контроля выполнения программ поступает первый импульстактовой частоты тактового генератора микро-, процессора либо внешнего независимого генератора. С входа 29 этот сигнал поступает .на тактовый вход 28 блока 8 управления, с первого информационного

ствующих элементов процессора поступает сигналы управления, предусмотренные первым шагом микропрограммы его функционирования. Работа блока 8

Управления представлена следующим (фиг.12) алгоритмом. ;

ос Управления представлена следующим (фиг.12) алгоритмом. ; дО

.

45

50

55

Шаг I . По сигналу Общий сброс описанным путем аппаратно устанавливаются в исходное состояние первый 10, второй 11 и третий 12 счетчики, блок 8 управления и триггер 2 ошибки (см. фиг.12, оператор 1 Начальная установка).

Шаг 2. По адресу (0000), определяемому выходными сигналами счетчика 12, из блока 9 постоянной памяти выбирается первьй байт очередной команды процессора и загружается соответственно первая часть, определяющая код .команды проверки, в регистр 16 команд, и вторая часть, определяющая количество импульсов синхронизации машинных циклов очередного линейного участка, в счетчик 1. Выборка команды обеспечивается, путем подачи сигна-. лов с первого выхода 30 блока 8 уп- равления на вход обращения блока 9 постоянной памяти, вход 42 записи

счетчика 1 и вход записи регистра 16 команд.

Производится инкремент счетчика 12 путем подачи сигнала с выхода 30 блока 8 управления на счетный вход 38 третьего счетчика 12, в результате чего на адресных входах блока 9 постоянной памяти устанавливается адрес второго байта команды проверки, если выбранная команда пятибайтная, и адрес следующей команды проверки, если выбранная команда - однобайтная (фиг..12, оператор 2 Выборка команд) ..

Шаг.З, Если с соответствующего выхода микроэвм на вход 81 подтверждения прерывания процессора и далее на четвертый адресный вход блока 8 управления поступает сигнал Под- тверждение прерывания и микроЭВМ переходит к отработке подпрограммы обслуживания прерывания выполняется переход к шагу 7 алгоритма,в противном случае к шагу 4 (фиг,12, оператор 3 Прерывание).

Шаг 4. Завершение линейного участка программы микроэвм сопровождается обнулением счетчика 1, содержимое которого уменьшается по мере обработ™ ки линейного участка путем подачи сигналов синхронизации машинных циклов с соответствующего выхода микро- ЭВМ на синхровход 53 процессора и даг1ее на счетный вход 52 в режиме вычитания счетчика 1. Нулевые сигналы с группы выходов 26 счетчика поступают соответственно на группу входов первого элемента ИЛИ 6, нулевой сигнал с выхода которого воспринимается на первом адресном входе 27 блока 8 управления как сообщение Конец линейного участка. Если на вход 27 блока 8 управления поступает сигнал Конец линейного участка, вьпюл- няется переход к шагу 8 алгоритма, в противном случае - к шагу 6(фиг. 12 оператор 4 Конец линейного участка).

Шаг 5. Линейный участок, состоящий из команд последовательно-й цепи операций (команды пересылок, арифметические операции, команды ввода, вывода, установки флагов и т.п.), микро- ЭВМ проходит путем инкремента программного счетчика микропроцессора. Содержимое програмного счетчика мик- роЭВМ устанавливается на шине адреса микроэвм в циклах обращения к па

5

0

мяти, содержащей контролируемую программу. Проверка правильности прохождения микроэвм линейного участка программы осуществляется путем сравнения текущих адресов обращения мик- роЭБМ к рабочей программе и синхронно изменяющегося адреса-копии, хранящегося в первом счетчике JO, Процедура сравнения текущего адреса и С адреса-копии и проверка правильности последовательного хода рабочей программы выполняется под управлением блока 19 анализа ветвлений. Работа блока I9 анализа ветвлений в режиме проверки правильности последоаатель- ного хода программы поясняется временной диаграммой, представленной на фиг.13.

После окончания сигнала Общий сброс (момент времени 137, эпюра 138, фиг.13) микроэвм по второму тактовому сигналу 139 (эпюра 140, фиг. 13) формируется сигнал 14 синх- 5 рониза ции микропроцессорной системы (эпюра 142, фиг.13). Эгот сигнал поступает на синхровход 53 процессора и далее (см.фиг.1) на вход 51 записи первого блока 3 регистров. Одновременно с информационного входа 22 процессора -:на информационный вход 21 первого блока 3 регистров поступает текущий начальный адрес 143 рабочей программы (эпюра 144, фиг.13) микроэвм и запоминается в нем (эпюра 145, фиг, 13).

Одновременно сигнал синхронизации с синхровхода 53 процессора поступает на счетный вход-52 в режиме вычитания счетчика 1 и производит изменение его содержимого.

0

5

0

Сигнал синхронизации поступает также на синхровход 50 блока 19 ана 45 лиза ветвлений и производит его запуск. Сигнал синхронизации с синхровхода 50 блока 19 анализа ветвлений

.

- поступает через инвертор 136 (см, фиг.Н) на вход установки в ноль пер50 вого триггера 121. Нулевой сигнал с единичного выхода триггера 121 по- стула ет через элемент И 126 на вход установки в ноль счетчика J24, и счетчик- 124 переходит в нулевое сос55 тояниа, а также на вход установки в еданицу триггера 122, устанавливая его в единичное состояние. Кроме того, нулевой сигнал с единичного выхода триггера 121 поступает на вход

19

установки в единицу триггера 123, устанавливая его в единичное состоякие. Нулевое значение сигнала с выхода младшего разряда счетчика 124 поступает на выход 63 блока 19 анализа ветвлений и далее (см. фиг.1) на вход 67 управления первого коммутатора 1 3 и вход 64 обра чения первого блока 3 регистров. Нулевой сигнал с входа 64 обращения (фиг,2) первого блока 3 регистров поступает на инверсный вход обращения регистра 89, и информация о младшем байте текущего адреса поступает с выходов регистра 89 на выход 20 блока 3 регистров и далее (фиг.1) на первый ин- формационньй вход схемы 5 сравнения. Одновременно нулевой сигнал с входа 67 управления первого коммутато ра 13 поступает через инвертор 108 (см. фиг.7) и элемент И 107 на вход управления группы шинных формировате- телй 105 с тремя состояниями, открывая формирователи этой группы для прохождения информации о младшем байте (состояния счетчика 99 фиг.5) первого счетчика 10 по цепи 99-69 (фиг.5), 69-70 (фиг.1), 70-105-58 (фиг.7) на второй вход схемы 5 сравнения. Единичный сигнал равенства младших байтов текущего адреса мик- роЭВМ и адреса копии процессора сое- тояние 147, эпюра 148, фиг.13) с выхода схемы 5 сравнения поступает на информационный вход 55.блока 19 анализа ветвлений и далее (фиг. И) через элементы ИЛИ 134 и И 127 на информационный вход триггера 122. После завершения сигнала синхронизации на входе установки в ноль и информационном входе триггера 121 устанавливается единичное значение сигнала. Очередной тактовый импульс 149 (эпюра 140, фиг. 13) поступает с тактового входа 29 процессора f фиг. 1/1 на тактовый вход 54 блока 19 анализа ветвлений и далее (фиг.11) на синхро- вход триггера 121, устанавливая его в единичное состояние. Сигнал с единичного выхода триггера 121 отпирает элемент И-НЕ 131 для прохождения тактового сигнала через элемент ИЛИ 133 на счетный вход в режиме суммирования (эпюра 150, фиг.13) счетчика 124, и счетчик 124 переходит из нулевого состояния в первое, а также на синхровход триггера 122, и единичное состояние этого триггера подтвержда1

- -43443920

ется (состояние 151, эшэра 152, фиг. 13).

Если в результате сбоя или отказа микроэвм младший байт текущего адреса не равен ожидаемому, нулевой сигнал неравенства с выхода схемы 5 сравнения (4мг. 1) поступает на информационный вход 55 блока 19 анализа

10 ветвлений и далее (фиг.II) через элементы ИЛИ 134 и И 127 на информационный вход триггера 122 и тактовый сигнал 149 (эпюра 140, фиг.13),поступающий по цепи 29-64 (фиг.1), 54-131J5 -122 (фиг. II) на синхровход триггера 122, переводит его в нулевое состояние (состояние 153, эпюра 152. фиг. 13).

Единичный сигнал с выхода младшего

20 разряда счетчика 124 поступает на выход 63 блока 19 анализа вeтвJJeний и далее (фиг. I ) на вход 64 обращения блока 3 регистров. Единичный сигнал с входа 64 (фиг.2) блока 3 регистров

25 поступает на прямой вход обращения регистра 90, и информация о старшем байте текущего адреса поступает с выходов регистра 90 на выход 20 блока 3 регистров и далее (фиг.1) на

30 первый информационный вход схемы 5 сравнения. Одновременно единичный сигнал с выхода 63 блока 19 и анализа ветвлений поступает на вход 67 управления первого коммутатора 13 и

2g далее (фиг.7) через элемент И 106 на вход управления группы шинных формирователей 104 с тремя состояниями, открывая формирователи этой группы для прохождения информации о старшем

40 байте (состояния счетчика 98, фиг.5) первого счетчика 10 по цепи 98-69 (фиг.5), 69-70 (фиг.1), 70-104-58 (фиг.7) на второй вход схемы 5 сравнения .

45 Единичный сигнал равенства старших байтов (состояния 154, эпюра 148, фиг.13) текущего адреса микроЭВМ и адреса-копии процессора с выхода схемы 5 сравнения (фиг.1) поступает на

50 информационный вход 55 блока 19 анализа ветвлений и далее (фиг.11) через элементы ИЛИ 134 и И 127 на информационный вход триггера 122. Очередной тактовый импульс 155 (эпюра

55 140, фиг, 13) поступает с тактового входа 29 процессора (фиг.1) на тдкто- вый вход 54 блока 19 анализа ветвле- , НИИ и далее (фиг.11) через элемент И-НЕ 131 на синхровход триггера 122

21

и подтверждает единичное состояние 156 (эпюра 152, фиг.13) этого триггера. Если в результате сбоя или отказ микроэвм старший байт текущего адрес не равен ожидаемому, нулевой сигнал неравенства с выхода схемы. 5 сравнения (фиг,1) поступает на информационный вход 55 блока 19 анализа ветвлений и далее (фиг. 11) через элемент ИЛИ 134 и И 127 на информационный вход триггера 122 и тактовый сигнал 155 (эпюра 140, фиг.53), поступающий по цепи 29-54 (фиг, 1), 54-131-122 (фиг. ll)s йа синхровход триггера 122, переводит его в нулевое состояние (состояние 157, эпюра 151, фиг. 13). Таким образом триггер 122 запоминает результат побайтного сравнения текущего адреса микроЭВМ и адреса копии процессора. Этот результат с едиьшчного выхода триггера 122 поступает на выход 56 блока 19 анализа ветвлений и далее (фиг,1) на адресный вход 57 блока 8 управления.

Тактовый импульс 155 (эпюра 140, фиг. 13) с тактового входа 29 процессора поступает также по цепи 29-54 (фиг.1), 54-131-133-124 (фиг.11) на счетный вход в режиме суммирования счетчика I24 и переводит этот счетчик из первого состояния во второе. При этом сигнал на выходе старшего счетчика 124 принимает единичное значение (состояния 158, эпюра 146, фиг,13).Этот сигнал запирает элементы ИЛИ 133 и j 34 для прохождения соответственно тактовых сигналов с входа 54 блока 19 анализа ветвлений через элемент И-НЕ 131 на счетный вход в режиме суммирования счетчика 124 и результат сравнения с информационного входа 55 через элемент И 127 поступает на информационный вход триггера 122, а также на первые входы элементов И 128 и 129, на третьи входы которых поступает единичное состояние сигнала с единич кого выхода триггера 123.. При этом в зависимости от результата сравне-- ния, поступающего с единичного выхода триггера 122 через элемент 127 на второй вход элемента И 128 и через инвертор 135 на второй вход элемента И 129, на выходах элементов И 128 и 129 появляются сигналы управлегшя счетчиком 125 блока 19 анализа ветвлений и- счетчика 10 процессора.

22

0

5

0

5

0

5

0

5

0

5

В случае равенства текущего адреса микроэвм и адреса-копии процессора единичное значение сигнала с выхода триггера 122 поступает через эле- мент И 127 на второй вход элемента И 128 и единичный сигнал с его выхода поступает на вход установки в ноль счетчика 125, устанавливая его в нулевые (эпюра 159, фиг.13) состояния. Одновременно сигнал с выхода элемента И 128 поступает на выход 63 блока 19 анализа ветвлений и далее (фиг,1) на счетный вход 65 счетчика 10 процессора и производит инкремент адреса-копии (эпюра 160, фиг.13). Если текущий адрес микроЭВМ и адрес-копии процессора не равны, нулевой сигнал с единичного выхода триггера 122 (фиг.11) поступает через элемент И 127 на второй вход элемента И 128 и запирает его для прохозвдения сигнала управления счетчиками. Одновременно этот сигнал поступает через элемент И 127 и инвертор 135 на второй вход элемента И 129, с выхода которого на счетный вход счетчика 125 поступает сигнал, производящий инкремент его содержимого (эпюра 159, фиг.13).

Единичный сигнал с выхода старшего разряда счетчика 124 поступает на вход элемента И-НЕ 132, и нулевой сигнал с его выхода поступает на вход установки в ноль триггера 123. Триггер I23 переходит в нулевое состояние, и нулевой сигнал с единичного выхода этого триггера запирает элементы И 128 и 129, запрещая управление счетчика 125 блока 19 анализа ветвлений и счетчика I О процессора до прихода следующего импульса синхронизации их микроэвм.

Единичный сигнал с выхода старше- то разряда счетчика 124 поступает ,f- также на выход 56 блока 19 анализа ветвлений и далее (фиг.) на второй адресный вход 57 блока 8 управления в качестве сигнала- Конец цикл сравнения. На этом первый цикл проверки правильности прохождения микро- ЭВМ линейного участка программы заканчивается ,

Счетчик 125 блока 19 анализа ветвлений предназначен для п одсчета количества следующих один за другим циклов микроэвм, в которых на шине адреса на информационном входе 22 процессора устанавливается производьиые , предусмотренные списком инструкций микропроцессора, адреса обращения к внешним устройствам. Команды последовательной цепи операций микропроцессора КР580ИК80 предусматривают до двух таких циклов. Например, команды записи в стек содержимого пары регистров микропроцессора предписывают во втором и третьем машинных циклах установку на игине адреса состояния регистра указателя стека. Следовательно, блок 19 анализа ветвлений при проверке последовательного хода выполнения программы должен до- пускать свободную адрессацию микро ЭВМ в течение двух циклов. Таким образом, если в течение трех следующих один за другим циклов микроЭВМ устанавливает на информационном входе 22 процессора нештатные адреса, блок 19 анализа ветвления в ответ на каждый из трех сигналов синхронизации машинных циклов выполняет указанные циклы проверки последовательного ход выполнения программы и счетчик 125 блока 19 анализа ветвлений переходит в третье состояние, единичные сигналы с выходов его разрядов поступают на входы элемента И I30 и на его выходе устанавливается сигнал Ошибка последовательного хода выполнения программы. Этот сигнал с выхода элемента И 130 поступает на выход 56 блока 19 анализа ветвлений и далее (фиг.1) на второй вход 57 адреса блока 8 управления.

Если на вход 57 блока 8 управления поступают сигналы Конец цикла сравнения и Ошибка последователь- ного хода выполнения программы) выполняется переход к шагу 6 алгоритма, в противном случае по сигналу Конец цикла сравнения выполняется переход к шагу 3 (фиг.12, оператор 5 Последовательный к ход).

Шаг 6. На втором информационном выходе 48 блока. 8 управления устанавливается сигнал Установка флага ошибки, который поступает на вход установки в единицу триггера 2, и устанавливает его в единичное состояние. Сигнал на нулевом выходе триггера 2 принимает нулевое значение. Этот сигнал поступает на выход 23 ошибки процессора и воспринимаетс на входе запроса прерывания микроЭВМ как сигнал запроса прерывания на обслуживание процессора, после чего вы

5 0 5 О

0 g

п

5

5

полияется переход к шаг-у 25 (фнг.., Оператор 6 Установки флага kinni6- кн).

Шаг 7. Заг рузка состояния процессора в стек предусматривает выполнение следующих операций:

а)запись- в стек команды состояние регистра 16 команд и состояние счетчика 1. С информационного выхода 30 (фиг. 1) блока 8 управления на вход 41 управления коммутатора 15 и далее (фиг.9) на входы управления первой 111 и второй 112 групп шинных формирователей с тремя состояниями поступает сигнал управления, и повторители открываются для прохождения информации о состоянии регистра 16 команд и счетчика I выделения импуль сов соответственно по цепям 26-88 (фиг.1), 88-1 12-60(фиг.9) и 16-87 {(фиг.1),87-1 1 1-60 (фиг.9) и далее (фиг. 1) с информационного выхода 60 коммутатора 15 на информационный вход-выход 61 блока 17 оперативной памяти. С информационного выхода 30 блока 8 управления на вход 35 управления блока 17 оперативной памя1и поступают сигналы обращения и записи, и состояние входов - выходов 61 записывается в ячейку блока 17 оперативной памяти. Адрес ячейки памяти определяется состоянием счетчика 1I, информация о котором поступает с информационного выхода 71 этого счетчика на адресный вход 72 блока 17 оперативной памяти;

б)декремент счетчика 11 (указателя стека). С информационного выхода 30 блока 8 управления поступает сигнал на счетный вход 34 в режиме вычитания счетчика 1I и производит декремент содержимого этого счетчика;

в)запись в стек старшего байта содержимого программного счетчика 12 процессора. С выхода 30 блока 8 управления на вход 40 управления коммутатора 14 и далее (фиг.8) на управляющие входы группы шинных формирователей 109 поступает управляющий сигнал, открывая повторители этой группы для прохождения информации о старшем байте состояния программного счетчика 12 процессора по цепи 84-85 (фиг.1), 85-109-59 (фиг. 8), 59-61 (фиг. 1) на информацимационный вход- выход 61 блока 17 оперативной информации. С информационного пыхоца 30 блока 8 управления на вход 35 ynpnn25I

ления блока 17 оперативной памяти поступают сигналы обращения и записи, и состояние входов-выходов 61 записывается в. ячейку блока 17 оперативной информации. Адрес ячейки памяти определяется состоянием счетчика I1, ин- Iформация о котором поступает с инфор мационного выхода 71 этого счетчика на адресный вход 72 блока 17 опера- |тивной памяти;

г)декремент сч етчика 1 (указателя стека);

д)запись в стек младшего байта содержимого программного счетчика 12 процессора. С выхода 30 блока 8 уп- равления на вход 40 управления ком-- мутатора 14 и далее (фиг.8) на управ ляющие входы группы шинных формирова 1телей 110 поступает управляющий сигнал, открывая шинные повторители этой группы для прохождения информации о младшем байте состояния программного счетчика 12 процессора по цепи 84-85 (фиг, I) 85-110-59 (фиг,8) |59-61 (фиг,1) на информационный вход |выход 61 блока 17 оперативной памя- |ти, и записывается в ячейку памяти |этого блока по адресу, определяемому состоянием счетчика 11, информация

b котором поступает с информацион- рого выхода :71 этого счетчика на Адресный вход 72 блока 17 оперативной памяти, под воздействием сигна.-- jioB обращения и записи, поступающих на вход 35 управления блока 17 опера тивной памяти с информационного выхода ЗО блока 8 управления;

е)декремент счетчика 1 (указа- геля стека). На этом загрузка состоя яия процессора в стек завершается

и выполняется переход к шагу 25 ал- 1 Оритма (фиг. 12, оператор 7 Загрузка состояния процессора в стек).

Шаг 8. Выполняется декодирование команды, код которой поступает с информационного выхода регистра 16 команд на пятый адресный вход 36 блока 8 управления, и в зависимости от этого кода выполняется переход к соответствующему шагу алгоритма:

при выполнении команды ПРД - к шагу 9 алгоритма,

при выполнении команды ПБУ - к ша ГУ 10 алгоритма,

при вьтолнении команды ПУС - к шагу 11 алгоритма,

при выполнении команды ВПР - к ша ГУ 15 алгоритма.

3443926

при выполнении команды ВПУ - к шагу 16 алгоритма,

при выполнении команды ВБУ - к шагу 21 алгоритма,

при выполнении команды ВУС - к ша- гу 22 алгоритма,

при выполнении команды РДИ - к ша гу 27 алгоритма (фиг.12, оператор 8

1Q Команда),

Шаг 9. Завершение линейного участка программы .микроэвм командой последовательной цепи операций сопро-- вождается выполнением команды ПРД

15 процессором. Выполняется процедура сравнения текущего адреса микроЭВМ и адреса-копии процессора и проверка правильности последовательного хода рабочей программы. Работа блока 19

20 анализа ветвлений в режиме проверки правильности последовательного хода программы описана в шаге 5 данного . алгоритма. Если с выхода 56 блока 19 анализа ветвлений на .вход 57 блока 8 25 управления поступает сигналы Конец цикла сравнения и Ошибка.последова тельного хода выполнения программы,: выполняется переход к шагу 6 алгорит ма, в противном случае по сигналу

30 Конец цикла сравнения выполняется переход к шагу 2(фиг «12, оператор 9 Последовательный ход).

Шаг 10, Завершение линейного участка программы микроэвм командой

безусловной передачи управления со- пров.о вдается выполнением команды ПБУ процессора. Выполняется процедура сравнения текущего адреса микроЭВМ и адреса-копии процессора, описанная

д0 в шаге 5 алгоритма. Если с выхода

56 блока 19 анализа ветвлений на вход 57 блока 8 управления поступают сигналы Конец цикла сравнения и Р-авенство текущего адреса микроЭВМ

g и адреса копии процессора, свидетельствующий о том, что в результате сбоя или отказа на шине адреса микро- ЭВМ нместр адреса безусловного перехода устанавливается инкрементированgQ ный адрес последней команды предыдущего линейного участка, вьтолняется перехед к шагу 6 алгоритма, в противном случае к шагу 12 алгоритма (фиг, 11, оператор 10 Последовательgg ный ход).

Шаг .,11. Завершение линейного участка программы микроэвм командой передачи управления по условию сопровождается выполнением команды ПУС

2714

процессора. Выполняется процедура, описанная в шаге 5 алгоритма. Если с выхода 56 блока 19 анализа ветвлений на вход 57 блока 8 управления поступает сигнал Конец цикла сравнения и Равенство текущего адреса микроэвм и адреса-копии процессора, свидетельствующий о том, что в результате вьшолнения команды условного перехода микроЭВМ перешла к выполнению следующей команды (условие передачи управления рабочей программой микроэвм не вьтолнялось), с информационного выхода 30 блока 8 управле- ния на счетный вход 38 в режиме суммирования счетчика 12 поступает серия из четырех импульсов и производят увеличение на четыре содержимого этого счетчика. С информационного вы- хода 84 счетчика 12 на адресный вход блока 9 постоянной памяти поступает адрес следующей команды процессора и выполняется переход к шагу 2 алгоритма, в противном случае - к шагу 12 алгоритма (фиг.12, оператор Последовательный ход).

Шаг 12. Проверка правильности выполнения микроэвм передачи управления заключается в сравнении teKyntero ад- реса микроэвм и ожидаемого адреса перехода, содержащегося во втором и третьем байтах команды процессора, и выполняется под управлением блока 19 анализа ветвлений. Работа блока 19 анализа ветвлений в режиме про- ,верки правильности перехода поясняется временной диаграммо.й, представленной на фиг. 14, G информационного выхода 30 блока 8 управления на вход 33 повторного запуска блока 19 анализа ветвлений поступает сигнал Повторный запуск (эпюра 161, фиг.14). Этот сигнал с входа 33 повторного запуска (фиг. П) Ьлока 19 анализа ветвлений поступает через элемент И 126 на входу установки в единицу триггера 122 и устанавливает его в единичное состояние (эпюра 152, фиг . 14), а также на вход начальной установки счетчика 124 и устанавливает его в нулевое состояние (эпюра 146, фиг. 14). Нулевое значение сигнала с выхода.младшего разряда счет

чика 124 поступает на вход элемента ИЛИ 133 и отпирает его для прохождения тактовых сигналов, а также на выход 63 блока I9 анализа ветвлений и далее (см. фиг.) на вход 64 рб

о 5

О Q g Q

5

5

39 28 ращения первого блока 3 регистров. Нулевой сигнал с входа 64 обращения (фиг.2) первого блока 3 регистрЪв поступает на инверсный вход обращения регистра 89, и информация о младшем байте текущего адреса поступает с выходов регистра 89 на вход 20 блока 3 регистров и далее (фиг.) на первый информационный вход схемы 5 сравнения. Одновременно с выхода 30 блока 8 управления на вход обращения блока 9 постоянной памяти поступает сигнал обращения, а с информационного выхода 84 счетчика 12 на адресный вход блока 9 постоянной памяти поступает адрес второго байта команды проверки процессора, т.е. адрес ячейки памяти, содержащей младший байт ожидаемого адреса перехода микроЭВМ. Младший байт ожидаемого адреса перехода поступает с выхода блока 9 постоянной памяти на второй информа- щюнный вход схемы 5 сравнения. Единичный сигнал равенства младших байтов текущего адреса микроЭВМ (эпюра 14, фиг.14) ожидаемого адреса перехода (эпюра 162, фиг. 14) с выхода схемы 5 сравнения поступает на информационный вход 55 блока 19 анализа ветвлений и далее (фиг. 1I) через элементы 1ШИ 134 и И 127 на информационный вход триггера 122. Очередной тактовый импульс 163 (эпюра 140, фиг.14) поступает с тактового входа 29 процессора (фиг.1) на тактовый вход 54 блока 19 анализа ветвлений н далее (фиг. 11) на сннхровход триггера 122 и подтверждает единичное состояние этого триггера (состояние,, 164, эпюра 152, фиг. 14). Если в результате сбоя или отказа микроЭВМ младший байт текущего адреса не равен ожидаемому, нулевой сигнал неравенства с выхода схемы 5 сравнения поступает по цепи 5-55 (фиг.1), 55- -134-127-122 (фиг,11) на информационный вход триггера 122 и тактовый импульс 163J поступаюпц й по цепи 29-54 (фиг. 1), 54-131-122 (фиг.11) на синхровход триггера 122, переводит его в нулевое состоятше (состояние 165, эпюра 152, фиг.14). Одновременно этот импульс поступает по цепи 54-131-133-123 (фиг,II) на счетный вход в режиме суммирования (эпюра 150, фиг, 14) счетчика 124 и счетчик 124 переходит из нулевого состояния в первое. Единичный сигнал

,с выхода младшего разряда счетчика 124 поступает на выход 63 блока 9 анализа ветвлений и далее (фиг.) на вход 64 обращения блока 3 регистров, Единичный сигнал с входа 64 (фиг,2) блока 3 регистров поступает на прямо вход обращения регистра 90, и информация о старшем байте текущего адре- : са поступает с выходов регистра 90 I на выход 20 блока 3 регистров и да- I лее (фиг, 1) на первый информационны I вход схемы 5 сравнения. Одновременно I с информационного входа 30 блока 8 I управления на счетный вход 38 счетчи : ка 12 поступает сигнал, производящий I инкремент его содержимого, и с ин- формационного выхода этого счетчика : на адресный вход блока 9 постоянной ; памяти поступает адрес третьего бай- та команды проверки процессора, т.е. I адрес ячейки памяти, содержащий : старший байт ожидаемого адреса пере- i хода микроэвм. Эта информация посту- j пает с выхода блока .9 постоянной памяти на второй информационный вход : схемы 5 сравнения. Единичный сигнал равенства старших байтов текущего j адреса микроЭВМ и ожидаемого адреса I перехода (соответственно эпюры и 162, фиг. 14) с выхода схемы 5 i сравнения поступает на информационный вход 55 блока 19 анализа ветвлений и указанным путем подтверждает еди- I ничное (состояние 166, эпюра 152, I фиг.14) состояние триггера 122 в мо- I мент прихода тактового импульса 167 I (эпюра J40, фиг.14). Если в резуль- I тате сбоя или отказа микроЭВМ стар- ший байт текущего адреса не равен : ожидаемому, нулевой сигнал неравенства с выхода схемы 5 сравнения посту- ; пает на вход 55 блока 19 анализа ветвлений и указанным путем устанавливает триггер 122 в нулевое состоя- ние (состояние 168, эпюра 152, фиг. 14) в момент прихода тактового импульса 167 (эпюра 140, фиг.14). Одновременно тактовый импульс 167 (эпюра 140, фиг. 14) поступает по цепи 54-131-133-124 (фиг.II) на счетный вход в режиме суммирования (эпюра 150, фиг.14) счетчика 124 и счетчик 124 переходит из первого состояния во второе. Единичный сигнал с выхода старшего разряда счетчика 124 поступает на выход 56 блока 19 анализа ветвлений, и далее (фиг.1) на второй адресный вход 57 блока 8 управления в качестве сигнала Конец цикла сравнения (состояние 169, эпюра 146 фиг.14).

Одновременно с информационного выхода 30 блока 3 управления на счетный вход 38 в режиме суммирования счетчика 12 поступает импульс, вызь вающий инкремент его содержимого и с информационного выхода 84 этого счетчика на адресный вход блока 9 постоянной памяти поступает адрес четвертого байта команды проверки перехода.

Подача сигнала Повторный запуск на вход 33 повторного запуска блока 19 ветвлений (эпюра,161, фиг. 14) сопровождается подачей сигнала Блокировка счетчика (эпюра 170,фиг.14) с информационного выхода 30 блока 8 управления на вход 32 блокировали коммутатора 13 и далее (фиг, 7) через элементы И 106 и 107 на входы управления шинных формирователей первой 104 и второй 105 групп с тремя состояниями, который переводит эти формирователи в высокоимпедансное состояние до окончания цикла сравнения текущего адреса и адреса перехода (эпюра 146, фиг.14). На этом цикл проверки правильности перехода микро ЭВМ заканчивается и выполняется переход к шагу 13 алгоритма (фиг.12, оператор 12 Проверка перехода),

Шаг 13. Результат сравнения текущего адреса микроЭВМ и ожидаемого адреса перехода с выхода триггера 12 поступает на выход 56 блока 19 анализа ветвлений и далее (фиг.1) на второй адресный вход 57 блока 8 управления. Если на этом входе устанавливается сигнал Ошибка перехода, соответствующий неравенству текущего адреса и ожидаемого адреса перехода, выполняется переход к шагу 6 алгоритма, в противном случае - к шагу 14 алгоритма (см.фиг.12, оператор 14 Ошибка перехода).

Шаг 14. При выполнении микроЭВМ команд последовательной цепи операций формирование адреса-копии процессора выполняется путем инкремента счетчика 10 синхронно с инкрементом программного счетчика. При выполнении микроэвм команд переходов формирование адреса-копии процессора выполняется путем записи в сЧетчик 10 адреса перехода после подтверждения

правильности его выполнения микроЭВМ. Запись адреса перехода в счетчик 10 выполняется под управлением блока 19 анализа ветвлений в соответствии с временной диаграммой, представленной на фиг.15. С информационного выхода 30 блок.1 8 управления п оступают сигналы Повторный запуск на вход 33 повторного запуска блока 19 анализа ветвлений, Запись в счетчик на вход 31 записи первого счетчика 10 и Блокировка счетчика на вход 32 блокировки коммутатора 13 (соответ10

Одновременно с информационного выхода 30 блока микропрограмного управления на вход обращеадя блока 9 постоянной памяти поступает сигнад обращения и четвёртый байт команды проверки перехода (информация о младшем байте адреса перехода процессора) устанавливается на выходе блока 9 постоянной памяти. Эта информация поступает на информационный вход бло- ка регистров 4 и далее (фиг.З) на информационный вход параллельной записи регистра 91. С выхода 30 (фиг,1)

ственно эпюры 161,- 171 и 170 фиг.15). 15блока 8 управления на вход 37.записи

Сигнал Повторный запуск поступаетблока 4 регистров и далее (фиг.З) |

с входа -33 (фиг.11) повторного запус-на вход параллельной записи.регистра

ка .блока 19 анализа ветвлений через91 по.ступает сигнал .записи, и шадэлемент И 126 - на вход начальной ИЙ байт адреса перехода процессора

установки счетчика 124 и устана влива-20записывается в регистр 91.

ет его в нулевое состояние. Нулевое значение сигнала с выхода старшего разряда счетчика 124 поступает на вход элемента ИЛИ 133 и отпирает его для прохождения тактовых сигналов, а нулевое значение сигнала с выхода младшего разряда счетчика 124 поступает на выход 63 блока 19 анализа . ветвления и далее (фиг.1) на вход 64 обращения первого 3 блока регистров. Нулевое значение сигнала с входа 64 обращения (фиг.2) первого блока 3 регистров поступает на инверсный вход обращения регистра 89, и информации и младшем байте текущего адреса адреса перехода поступает с. выходов регистра 89 на выход 20 блока 3 регистров и далее (фиг.1). на информационный вход 68 параллельной записи, счетчика 10 (состояние Т72., эпюра 173, фиг.15), Сигнал Запись в счетчик с входа 3.1 записи первого счетчика 10 .поступает (фиг.5) на входы элементы И 100 и 101 и отпирает их для прохождения сигналов обращения на входы параллельной- записи счетчиков 98 и 99. Сигнал Блокировка счет чика с входа 32 блокировки коммутатора 13 (фиг. 7), поступая на входы элементов И 106 и 107, запирает их для прохождения сигналов управления на управляющие входы -шинных -формирователей первой 104 и второй 105 группы формирователей с тремя состояниями. Выходы этих буферов переводятся . в высокоимпедансное состояние и блокируют поступление информ ации о состоянии счетчика 10 на внутреннюю шину. - .

Одновременно с информационного выхода 30 блока микропрограмного управления на вход обращеадя блока 9 постоянной памяти поступает сигнад обращения и четвёртый байт команды проверки перехода (информация о младшем байте адреса перехода процессора) устанавливается на выходе блока 9 постоянной памяти. Эта информация поступает на информационный вход бло- , ка регистров 4 и далее (фиг.З) на информационный вход параллельной записи регистра 91. С выхода 30 (фиг,1)

0

5

Сигнал с выхода младшего разряда счетчика 124 (фиг.11) поступает на выход 63 блока 19 анализа ветвлений по цепи 63-66 (фиг. и, 66-102-101-99 5 (фиг.5) на в.ход параллельной записи счетчика 99, и информация о младшем байте адреса перехода, поступающая с информационного входа 68 счетчика 0 на информационный -вход параллельной записи, записывается в счетчик 99 (эпюра 174, фиг. 15).

Тактовый сигнал 175 (эрюра 140. фиг. 15) поступает по цепи 29.-54 . (фиг.1), 54-131-133-124 (фиг.11), на счетный вход s режиме суммирования счетчика 124 и переводит его из -нулевого состояния в первое. Единичный сигнал с выхода младшего разряда счетчика 124 поступает по цепи 124-- 63 (фиг.11) 63-64 (фиг.1) и далее (фиг.2.) на прямой вход обращения регистра 90, и информация о старшем байте текущего адреса адреса перехода поступает с выходов этого регистра на выходе 20 блока 3 регистров и далее по .цепи 20-68 (фиг.1), 68-98 (фиг.5) на информационный вход параллельной записи регистра 98 (эпюра 173, фиг. 15). Одновременно единичный сигнал с выхода м.падшего разряда счетчика 124 поступает по цепи 124-63 (фиг.П) 63-66 (фиг.1), 66-100-98 (фиг. 5) на вход парал-- лельной записи регистра 98 и инфор.-. мация о старшем байте адреса перехода записывается в нем (эпюра 176, фиг.15)..

Одновременно с информационного вькода 30 блока 8 управления на

0

5

0

5

счетный вход 38 счетчика I2 поступает сигнал счета и производит инкремент его содержимого. С информа- ционного выхода счетчика 12 на адресный вход блока 9 постоянной памяти, поступает адрес пятого -байта коман- ды проверки перехода процессора (ар,- рее старшего байта перехода).

Тактовый импульс 177 (эпюра 40, фиг.15), поступающий по цепи 29-54 (фиг.1), 54-13i-l,.4 (фигЛ) на счетный вход в режиме суммирования счетчика 124, переводит этот счетчик из первого состояния во второе. Единичный сигнал состояние 178, эп ора 146, фиг.15 с выхода старшего разряда счетчика 124 поступает на выход 56 блока 19 анализа ветвлений и далее пО -цепи (фиг.1) 56-57 воснрини- мается как сигнал Конец цикла записи адреса перехода.

Одновременно сигнал, поступающий с информационного выхода 30 блока 8 управления, поступает на вход обращения блока 9 постоянной памяти н старший байт адреса перехода процессора с выхода этого блока поступает на информационный вход 24 блока 4 регистров и далее (фиг.З) па-инфор- мационньй вход параллельной записи регистра 92. Сигналы, поступающие с информационного выхода 30 блока 8 управления на входы записи 37 блока 4 регистров и 39 счетчика 12, производят запись соответственно старшего байта адреса перехода процессора D . регистр 92 блока 4 регистров и адреса перехода процессора в счетчик 12.

Таким образом, в результате выполнения данного шага алгоритма производится параллельное выполнение двух операций: запись адреса перехода процессора из блока 9 постоянной памяти в программный счетчик 12 процессора, после чего выполняется переход к шагу 2 алгоритма (фиг.12, оператор 14 Загрузка адреса перехода).

Шаг 15. Завершение линейного уча-- стка программы микроЭВМ командой безусловного вызова подпрограммы сопровождается выполнением команды ВНР .процессора. При этом выполняется процедура сравнещ я текущего адреса микроэвм и. адреса-копии процессора и проверка последовательного хода рабочей программы, описанная в цгаге 5 алгоритма. Если с выхода 56 блока 19

5

0

анализа ветвлений на вход 57 блока В управления поступает сигнал Конец цикла сравнения и Равенство текущего адреса микроЭВМ и адреса-копии процессора, свидетельствующий о том, что в результате сбоя или отказа, на шине адреса микроЭВМ вместо адреса вызываемой подпрограммы устанавливается инкрементированный адрес последней команды, предыдущего линейного участка, т.е. адрес команды, следующей за Командой безусловного вызова подпрограг мы, выполняется переход к шагу 6 алгоритма, в противном случае - к шагу 17 алгоритма (фиг. 12, оператор Последовательный ход).

Шаг 16. Завершение линейного участка программы микроэвм командой вызова подпрограммы по условию сопровождается выполнением команды ВПУ препроцессора. Выполняется,процедура проверки правильности- погледователь-- ного хода программы микроэвм, описан5 ная в шаге 5 алгоритма. Если с выхода 56 блока 19 анализа ветвлений на вход 57 блока 3 управления поступает сигнал Конец цикла сравнения и Равенство текущего адреса 1 {икроЭВМ

0 и адреса-к:опии процессора, сввде- тельств-ующий о. том, что в результате выполнения команды вызова подпрограммы по условию микроэвм перешла к выполнению следующей команды, т.е. начальной команды очередного линейного у шстка (условие передачи управления рабочей программой микроЭВМ не выполнялось), с информационного выхода 30 блока 8 управлен:ия на счет д ный вход в режима с п-ширования счетчика 12 серия из четырех импульсов и производит увеличение на четыре содержимого этого счетчика, С .информационного выхода 84 счетчис- ка 12 на адресный вход блока 9 постоянной памяти поступает адрес следующей команды пр оцессора и выполняется переход к шагу 2 алгоритма, в противном случае -.к шагу 17 алгоритg ма (фиг,12, оператор 16 Последовательный ход).

Шаг 17. Проверка правильности выполнения микроэвм передачи управления при выпо.лнении коман-ды вызова

с подпрограммы заключается в сравнении .текущего адреса микроЭВМ и ожидаемого адреса перехода, содержащегося во втором и третьем байтах команды про-, цессора, н вьтолняётся в соответствий

5

с описанием, приведенным в шаге 1 2 алгоритма. После окончания цикла проверки перехода выполняется переход к шагу 18 алгоритма (фиг.12, оператор 17 Проверка перехода).

Шаг 18. Результат проверки перехода с выхода 56 блока 19 анализа ветвлений поступает на вход 57 блока 8 управления.Если на этом входе уста-/ навливается сигнал Ошибка перехода соответствующий неравенству текущего адреса адреса передачи управления при вьшолнении команды вызова программы и ожидаемого адреса перехода выполняется переход к шагу 6 алгоритма, в противном случае к шагу 19 алгоритма (фиг.12, оператор 18 dшиб ка перехода).

Шаг 19. При выполнении микроэвм команд вызова подпрограмм формирование адреса-копии процессора выполняется путем записи в счетчик 10 адреса перехода после подтверящения правильности его выполнения микроЭВМ. Процедура загрузки адреса перехода в счетчик 10 описана в шаге 14 алгоритма. Одновременно выполняется запись в блок 4 регистров собственного адреса перехода процессора (четвер- того и пятого байтов команды проверки вызова подпрограммы). Эта процедура отличается от описанной в шаге 14 алгоритма тем, что сигнал, поступаю1щий с информационного выхода 30 -ц врата из подпрограммы, выполняется

блока 8 управления на вход 37 записи блока 4 регистров в момент поступления на информационный вход 24 блока 4 регистров старшего байта адреса перехода процессора, производит запись старшего байта адреса перехода процессора в регистр 92 блока 4 регистров, сигнал с информационного выхода 30 блока 8 управления на вход 39 записи счетчика 12 не поступает, а на счетный вход счетчика I2 поступает сигнал, производящий инкре мент содерзкимого этого счетчика. С инфор- : мационного выхода 84 счетчика 12 на информационный вход 85 коммутатора 14 поступает адрес команды процессора, .следующей за командой проверки вызова подпрограммы (адрес воз- врата процессора). Выполняется переход к шагу 20 алгоритма (фиг. 12, оператор Загрузка адреса перехода). Шаг 20. Загрузка состояния процессора в стек предусматривает выполнение процедуры, описанной в шаге 7

40

переход к шагу 6 алгоритма,.в проти ном случае - к шагу 23 алгоритма (фиг.12, оператор 21 Последовательный ход).

Шаг 22. Завершение линейного уча стка программы микроЭВМ командой возврата из подпрограммы по условию сопровождается выполнением команды ВБУ процессора. Вьтолняется процеду 45 рй сравнения текущего адреса микроЭ и адреса-копии процессора и проверк правильности последовательного хода рабочей программы, описанная в шаге 5 алгоритма. Если с выхода 56 блока 19 анализа ветвлений на вход 57 бло ка 8 управления поступает сигнал К нец цикла сравнения и Равенство текущего адреса микроЭВМ и адреса- копии процессора, свидетельствующи о том, что в результате выполнения команды возврата из подпрограммы по условию микроэвм перешла к выполнению следующей команды, т.е. начальной команды очередного линейного уч

50

55

алгоритма, после чего сигнал, поступающий с информационного выхода 30 блока 8 управления на вход 39 записи счетчика 12, производит параллельную запись адреса перехода, поступающего с выхода 82 блока 4 регистров на ин- формационньй вход 83 параллельной записи, в этот счетчик и вьтолняется переход к шагу 2 алгоритма (фиг.12, оператор Загрузка состояния процессора в стек).

Шаг 21. Завершение линейного участка программы микроэвм командой безусловного возврата из подпрограммы сопровождается вьшолнением команды ББУ процессора. Выполняется процедура сравнения текущего адреса микро- ЭВМ и адреса-копии процессора и проверка последовательного хода рабочей программы, описанная в шаге 5 алгоритма . Если с выхода 56 блока 19 анализа ветвлений на вход 57 блока 8 управления поступает сигнал Конец цикла сравнения и Равенство текущего адреса микроЭВМ и адреса-копии процессора, свидетельствующий о том, что в результате сбоя или отказа на шине адреса микроЭВМ вместо адреса возврата из подпрограммы устанавливается инкрементированнЕяй адрес последней команды предьщущего линейного участка, т.е.адрес команды, следующей эа командой безусловного возврата из подпрограммы, выполняется

переход к шагу 6 алгоритма,.в противном случае - к шагу 23 алгоритма (фиг.12, оператор 21 Последовательный ход).

Шаг 22. Завершение линейного учаг стка программы микроЭВМ командой возврата из подпрограммы по условию сопровождается выполнением команды ВБУ процессора. Вьтолняется процеду- рй сравнения текущего адреса микроЭВМ и адреса-копии процессора и проверка правильности последовательного хода рабочей программы, описанная в шаге 5 алгоритма. Если с выхода 56 блока 19 анализа ветвлений на вход 57 блока 8 управления поступает сигнал Конец цикла сравнения и Равенство текущего адреса микроЭВМ и адреса- копии процессора, свидетельствующий о том, что в результате выполнения команды возврата из подпрограммы по условию микроэвм перешла к выполнеию следующей команды, т.е. начальной команды очередного линейного уча

стка программы (условие возврата из подпрограммы микроЭВМ не выполии- лось), выполняется переход к шагу 2 алгоритма, в противном случае - к шагу 23 алгоритма (фиг.12, оператор После довательньй ход) ,

Шаг 23. Загрузка состояния процессора из стека предусматривает выпол нёние следующих операций: , ; а) инкремент счетчика I1 (указате I ля стека). С информационного выхода i 30 блока 8 управления поступает сиг- I нал на счетный вход 34 в режиме сум:мирования счетчика 11 и производит инкремент содержимого этопо счетчика Одновременно производится повторньй :запуск блока 19-анализа ветвлений в режиме записи текуи1его адреса в счет ;чик 10 адреса-копии и выполняется процедура загрузКи адреса возврата IB этот счетчик, описанная в шаге 14 I алгоритма;

I б) запись из стека младшего байта адреса возврата процессора в блок 4 -регистров, С выхода 30 (фиг.1) блока 8 управления на вход 35 управления ;блока 17 оперативной памяти поступаю

и количества импульсов синхронизации соответственно в регистр 16 комавд и счетчик I (эта операция имеет смысл в случае возврата микроЭБМ из подпро- 25 граммы обслуживания прерьгоания, так как в стеке сохраняется количество импульсов синхронизации незавершенно го линейного з астка) , Одновременно сигналом, поступающим с информацион:сигналы обращения и чтения. Одновре|менно с информационного выхода 71 30 ного (участка) вькода 30 блока 8 уп|счетчика 1I (указатель стека) на .ад- равления на вход 39 записи счетчика

|ресный вход 72 блока 17 оперативной

памяти поступает адрес ячейки памяти,

|содержащей информацию: о младшем бай|те адреса возврата процессора, эта s выхода 82 блока 4 .регистров

информация поступает с информационно- на информационный вход параллельной

ро входа-выхода 61 блока 17 оператив ой памяти на информационный вход 24

Ьлока.4 регистров и далее (фиг.З) на

Информационный вход параллельной заЬиси регистра 91 . Сигнал, постулаю(ций с информационного выхода 30

(фиг.1) блока 8 управления на вход 37

12, производится запись в этот счетчик информации об адресе возврата процессора, поступакицей. с информацио

записи счетчика 12, и выполняется переход к шагу 24 алгоритма (фиг.12, оператор 23 Загрузка состояния про

Загрузка адреса

4Q цессора из стека, возврата).

Шаг 24, . Вьшолнение команды вызова подпрограммы микроЭВМ сопровождается загрузкой в стек состояния прозаписи блока 4 регистров и далее (фиг.З) на. п араллельной записи регистра 91., .записьгоаат информацию о младшем байте адреса возврата процессора в этот регистр;

в)инкремент счетчика I1 (указателя стека);

г)запись из стека старшего байта адреса возврата процессора в блок 4 |зегистров. С выхода Зй (фиг.1) блока $ управления на вход 35 управления