Изобретение относится к вычислительной технике и предназначено для синхронизации с вычислительным процессом в мини и микроЭВМ при экспериментальном исследовании устойчивости ЭВМ к различным типам отказов и сбоев.

Целью изобретения является расширение функциональных возможностей путем организации новых режимов работы устройства, а именно возможности выделения отдельных участков программ по информации, возможности выделения заданного количества обращений к подпрограммам иди заданного количества срабатываний определенных участков программ, возможности программирования последовательности событий, появление которых в ЭВМ необходимо выделить в данном эксперименте, возможности программирования выделения совокупности событий, которые могут наступить в разные моменты времени, возможности синхронизации с последовательностью состояний в различных объектах ЭВМ, возможности подсчета количества тактовых импульсов в различных модулях ЭВМ, программируемого выделения дискретных сигналов или их последовательности.

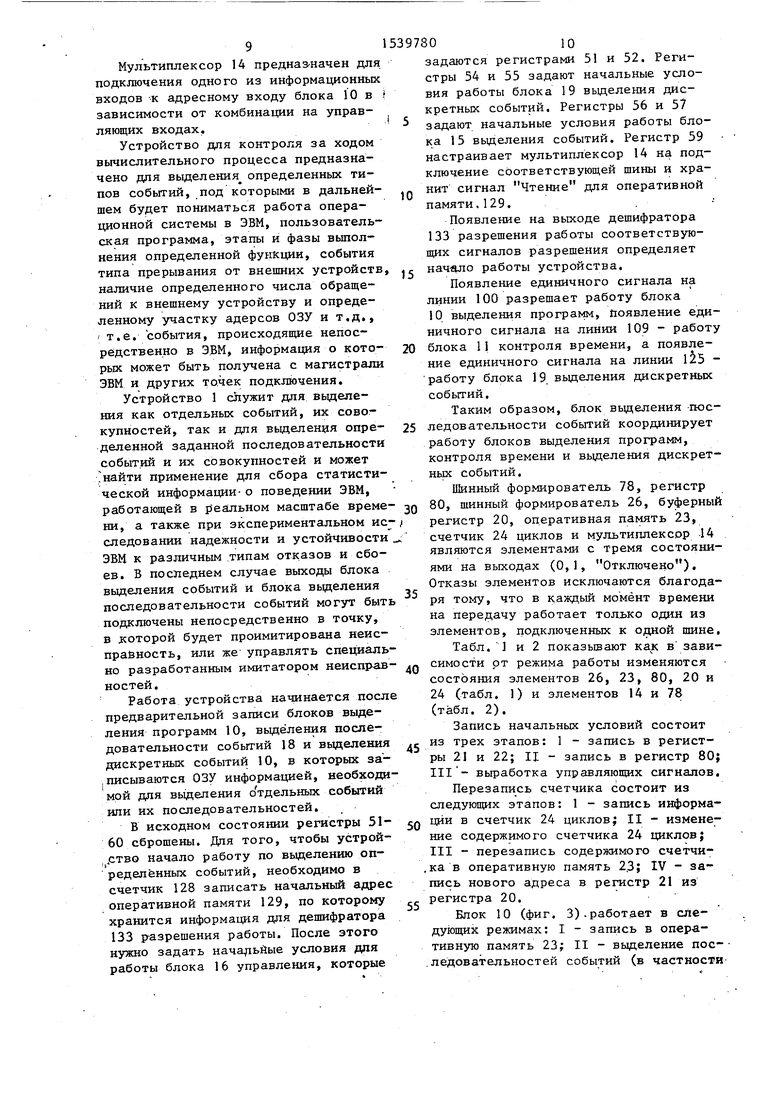

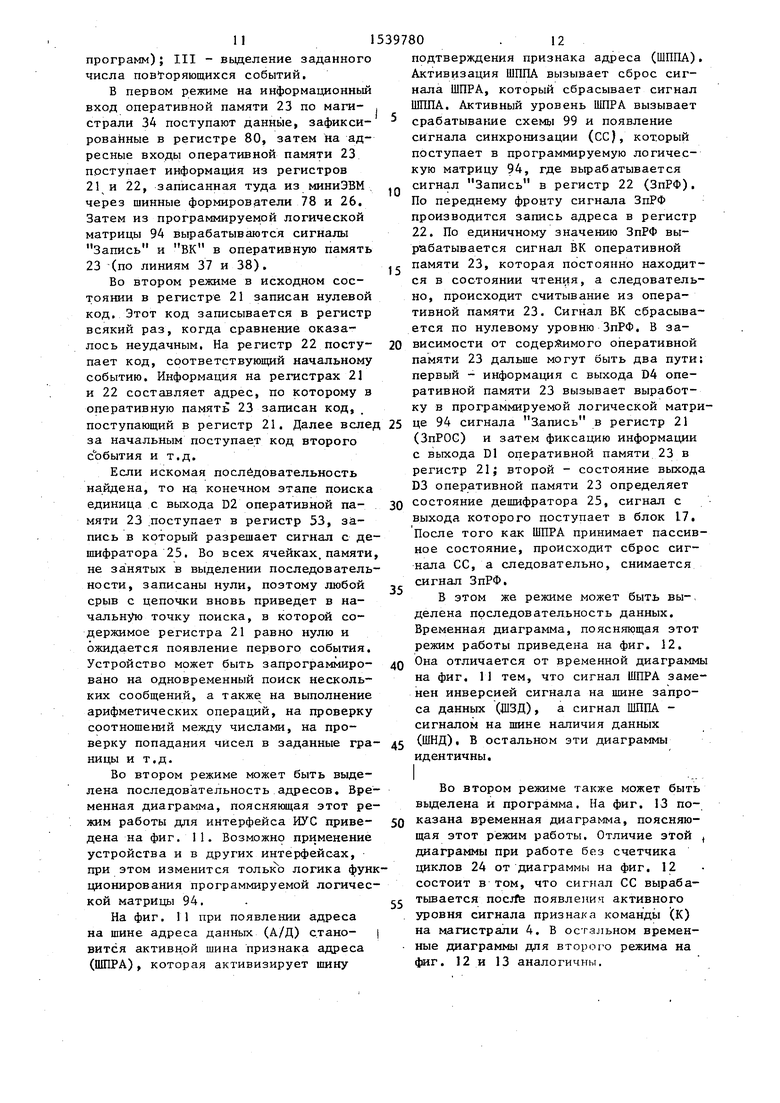

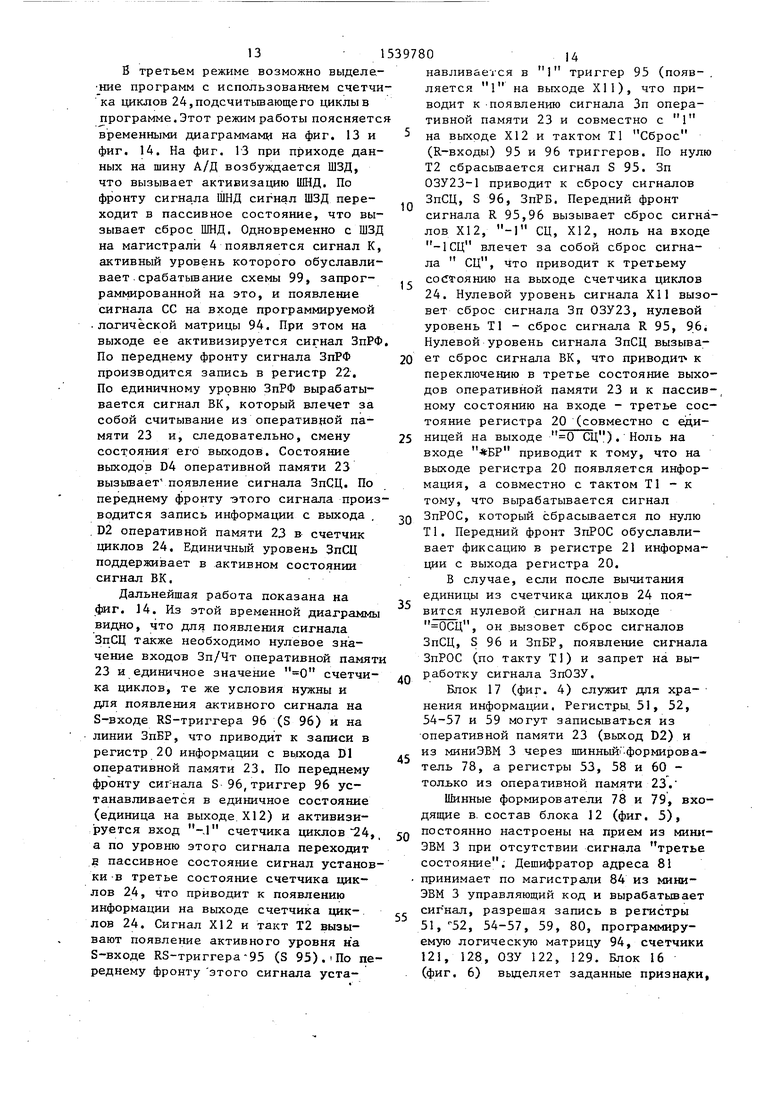

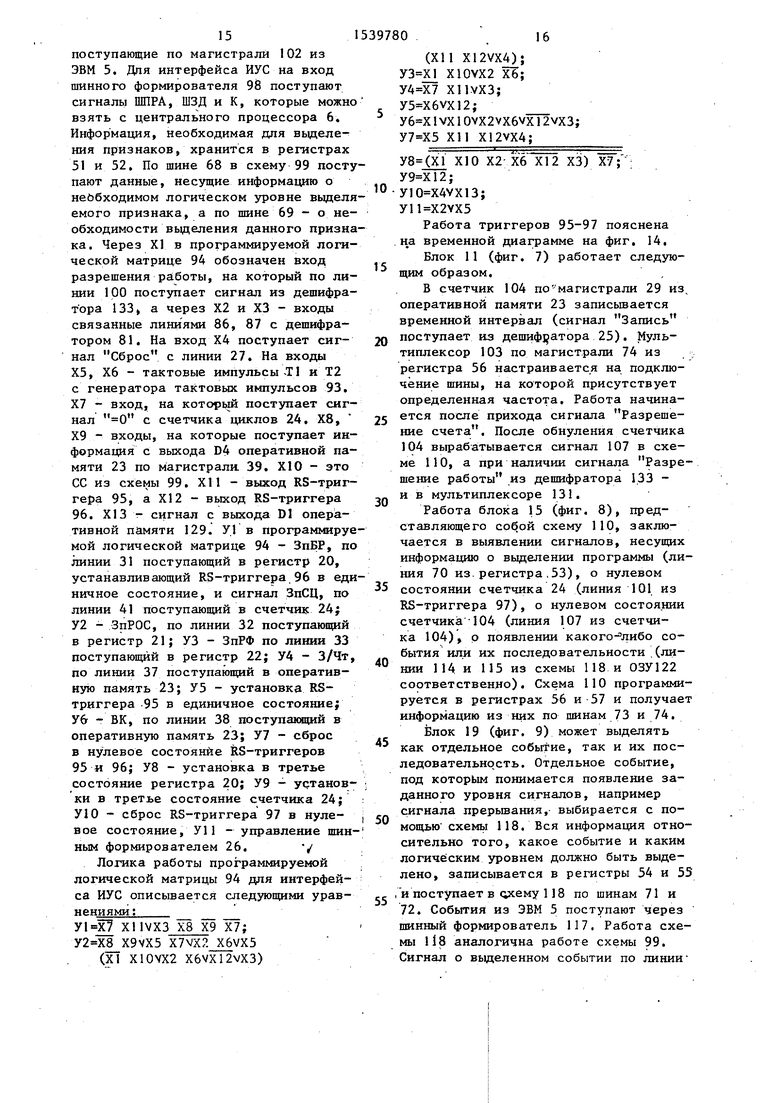

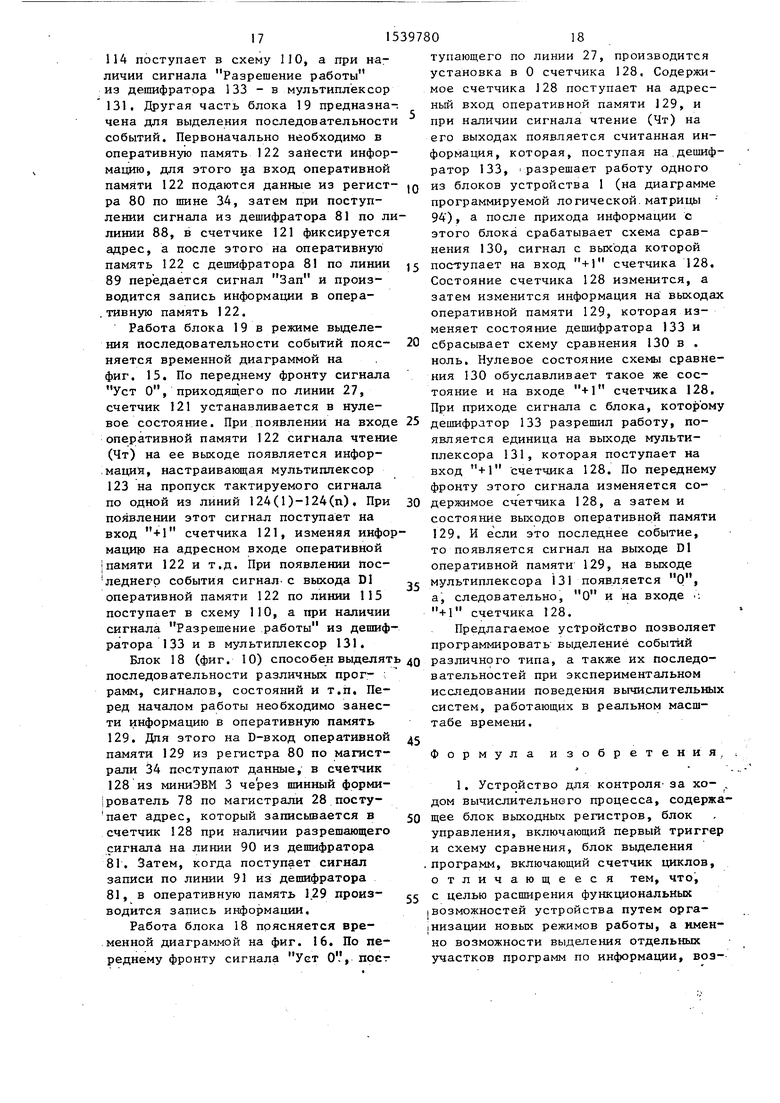

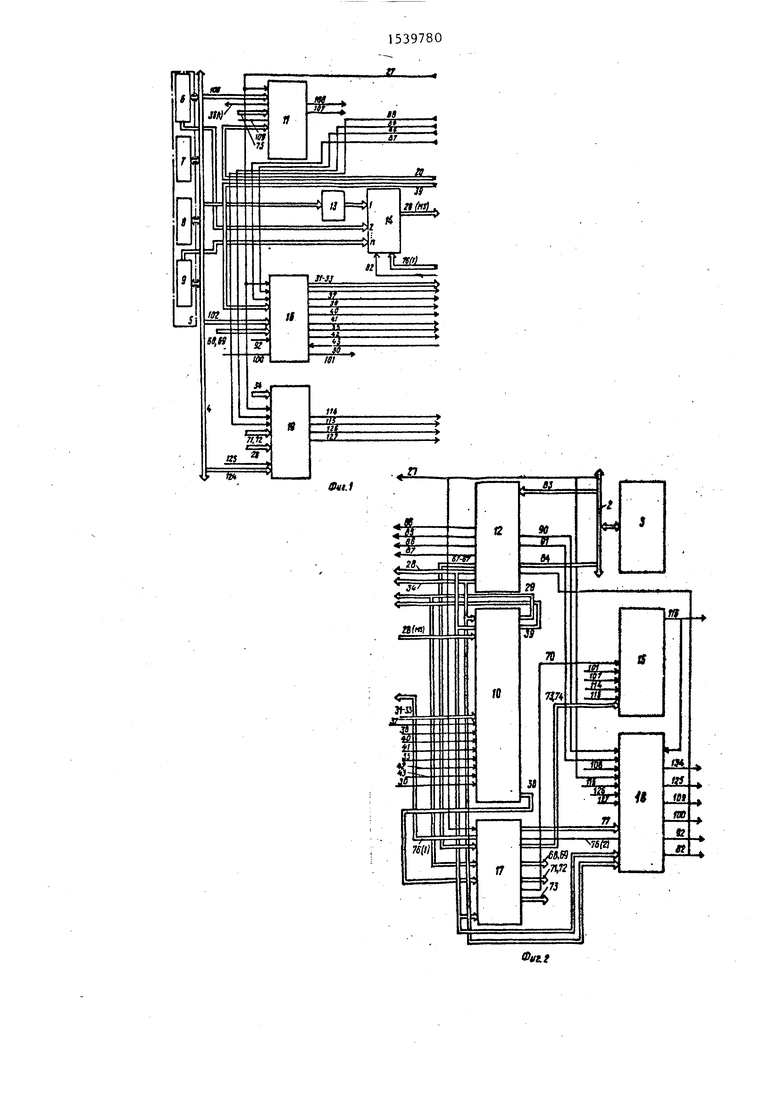

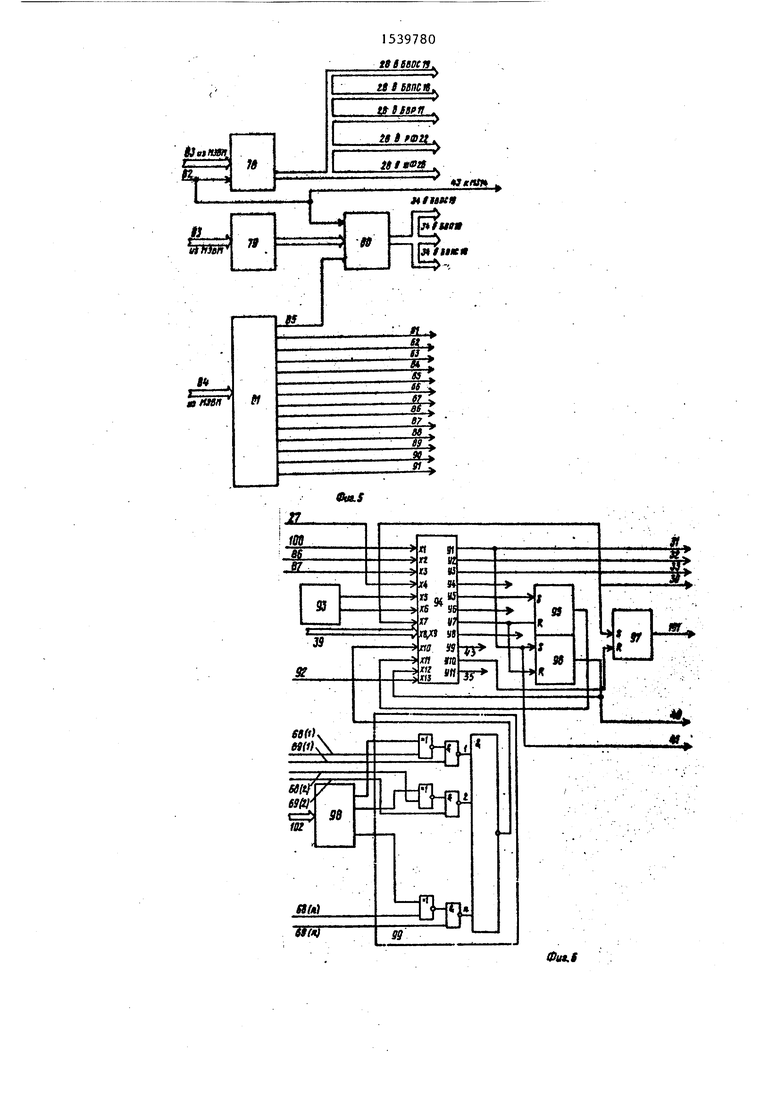

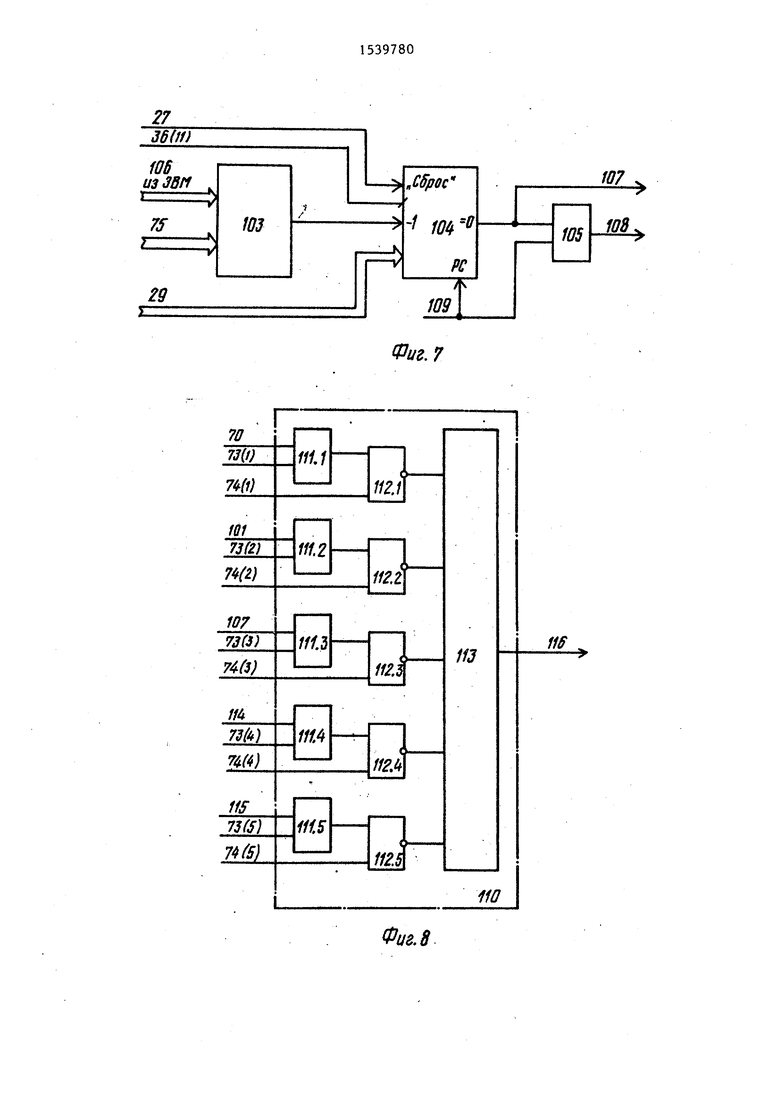

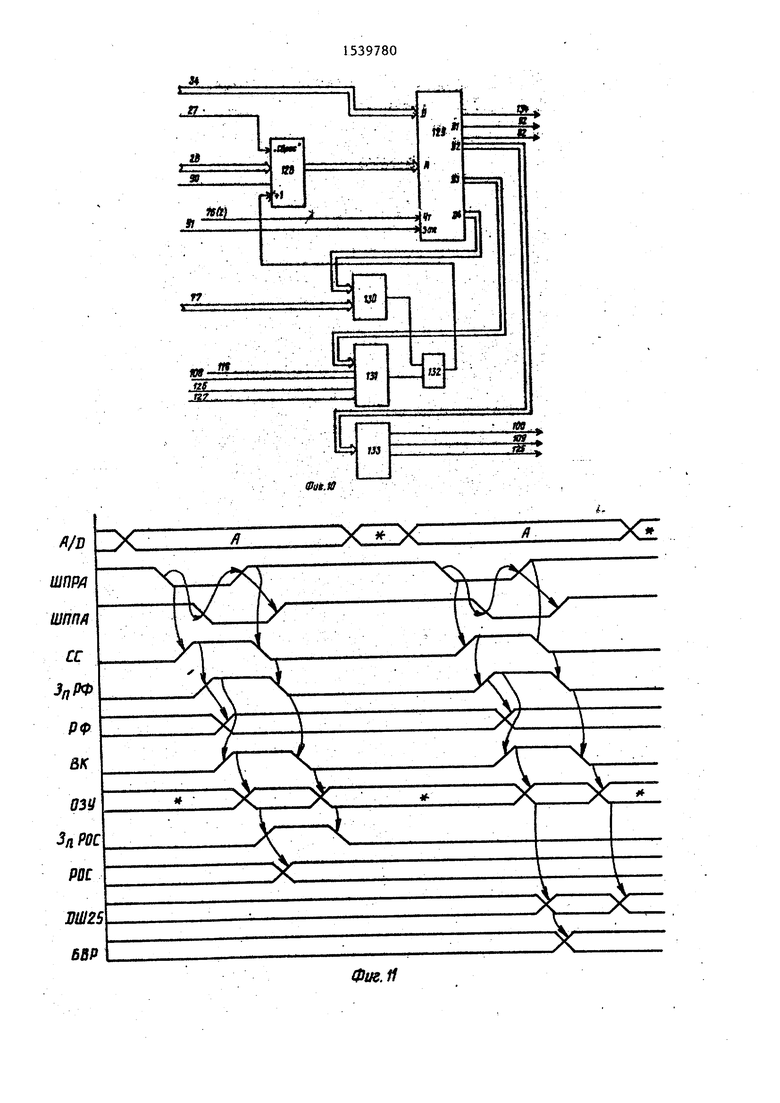

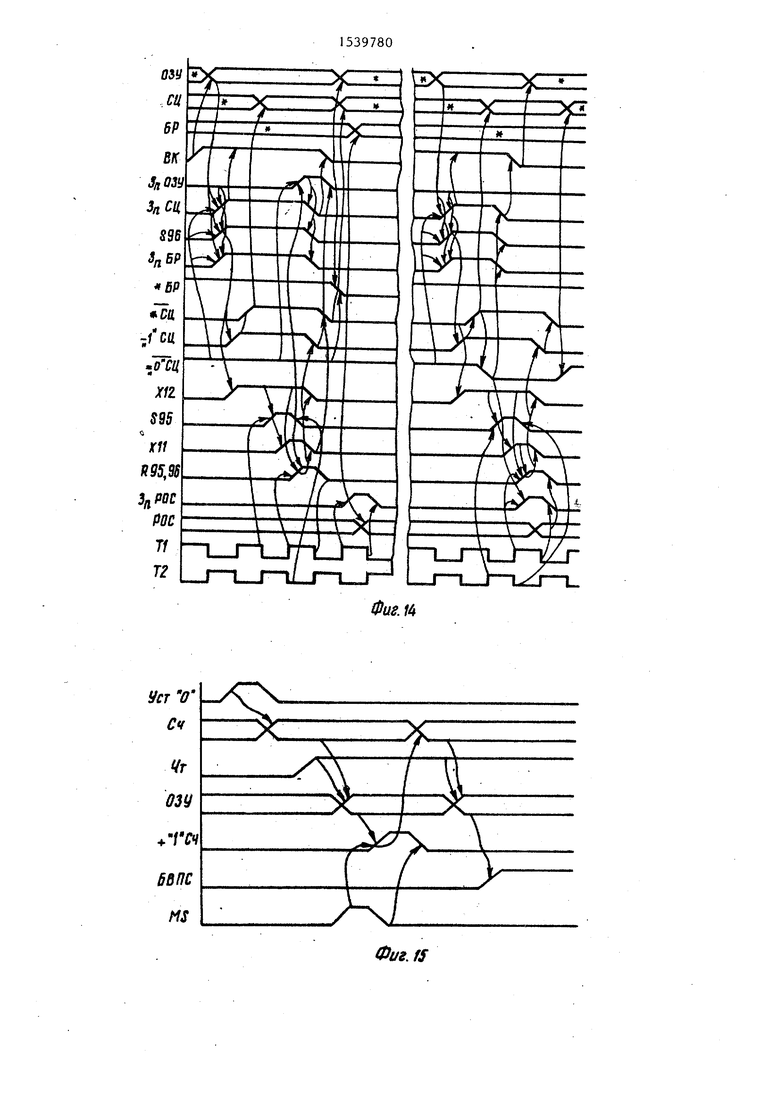

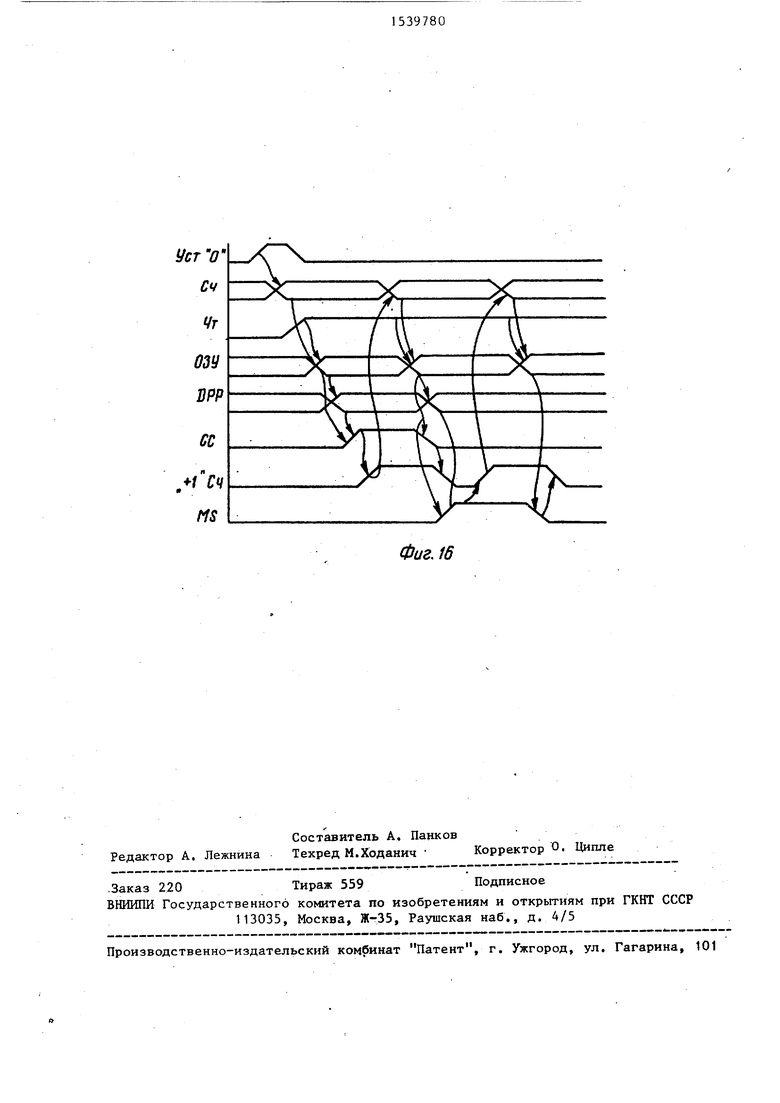

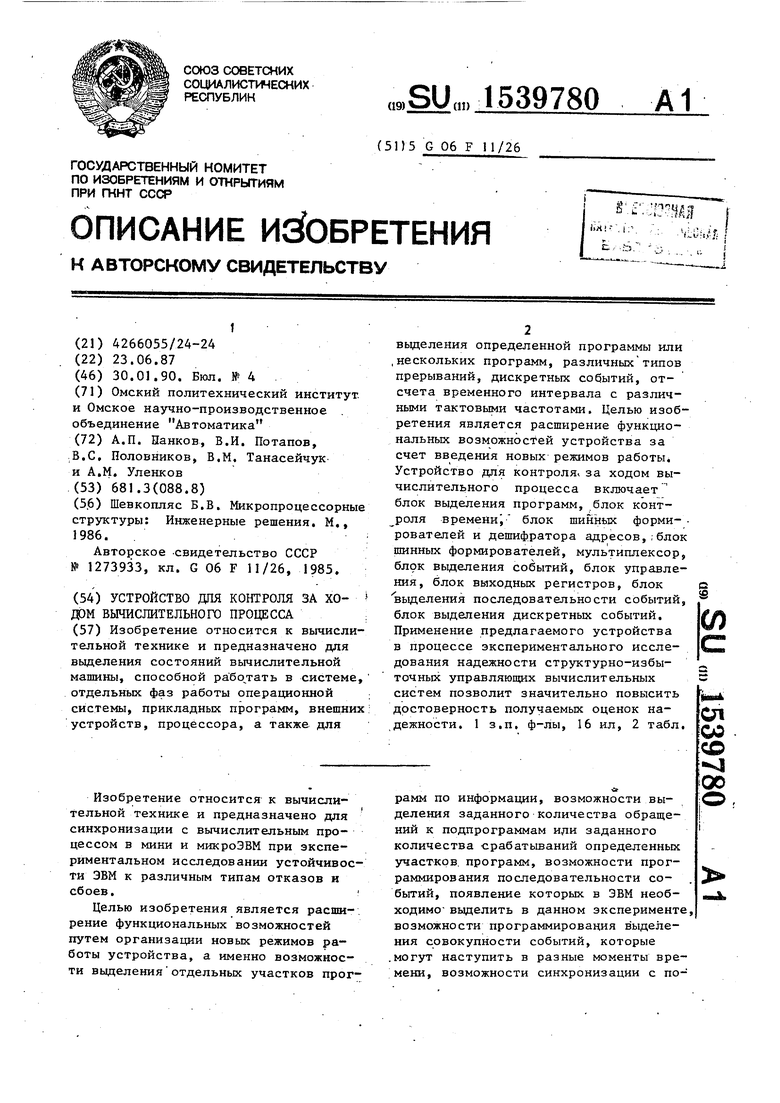

На фиг. 1 и 2 изображена схема устройства для контроля за ходом вычислительного процесса: на фиг. 3 - схема блока выделения программ; на фиг. 4 - схема блока выходных регистров; на фиг. 5 - схема блока шинных формирователей и дешифратора адресов; на фиг. 6 - схема блока управления; на фиг. 7 - схема блока контроля времени; на фиг. 8 - схема блока выделения событий; на фиг.9 - схема блока выделения дискретных событий; на фиг. 10 - схема блока выделения последовательности событий; на фиг. 11 - временные диаграммы выделения последовательности адресов; на фиг. 12 - временные диаграммы ВЦ- деления последовательности данных; на фиг. 13 - временные диаграммы выделения последовательности команд; на фиг. 14 - временные диаграммы выделения последовательности команд с использованием счетчика циклов; на фиг. 15 - временные диаграммы работы блока выделения дискретных событий; на фиг. 16 - временные диаграммы работы блока выделения последовательности событий

10

15

Устройство 1 для контроля за ходом ройства.

23, счетчика 24 циклов, д 25 и шинного формировател

Блок 10 в режиме начал новки производит запись в ную память 23 необходимой ции , а в режиме синхрониз ление необходимых програм вательностей состояний вы ной машины и т.п., а такж вляет управление блоком 1

На фиг. 3 позициями 27 чены входы и выходы блока линии соединений входов и блоков устройства, показа фиг. 1, 2, 4, 5, 6, 7, 9

Блок 17 выходных регис (фиг. 4) состоит из семи ИЛИ 44-50 и десяти регист На фиг. 4 позициями 61-77 входы и выходы блока 17, линии соединений входов и блоков устройства, привед фиг. 1, 2, 6, 7, 8, 9 и 1

Блок 12 шинных формиро дешифратора адресов (фиг. жит формирователи 78 и 79 80 и дешифратор 81 адреса позициями 82-84 обозначен ка 12, позиций 85 - первы шифратора адресов 81, а п 86-91 - выходы блока 12, позициями 82-84 и 86-91 н 2, 6, 9 и 10 обозначены л нений входов и выходов бл

„ 20

25

30

вычислительного процесса (фиг. 1 и 2) подключается к магистрали 2, входящей в состав миниЭВМ 3, и к магистрали 4, входящей в состав ЭВМ 5, которая содержит центральный процессор 6, оперативное запоминающее устройство 7, устройство 8 связи с объектом и внешнее устройство

Устройство 1 для контроля за ходом вычислительного процесса содержит блок 10 выделения программ, блок 11 контроля времени, блок 12 шинных формирователей и дешифратора адресов, блок 13 шинных формирователей, мультиплексор 14, блок 15 выделения событий, блок 16 управления, блок 17 выходных регистров, блок 18 выделения последовательности событий и блок 19 выделения дискретных событий.

40

45

50

Блок 16 управления (фи держит вход 92, генератор вых импульсов, программир ческую матрицу 94, три RS 95-97, шинный формировате граммируемую схему 99 сра фиг, 6 позициями 100-102 входы и выходы блока 16, позициями 92, 100, 101 и чены линии соединений вхо дов блоков устройства на 8 и 10.

Блок 11 контроля време состоит из мультиплексора чика 104 и элемента И 105

Блок 11 может работать записи в счетчик и счета. позициями 09. обознач

Блок 10 выделения программ (фиг.З) и выходы блока 11, вместе

-; 10

15

м ройства.

5397804

23, счетчика 24 циклов, дешифратора 25 и шинного формирователя 26,

Блок 10 в режиме начальной установки производит запись в оперативную память 23 необходимой информации , а в режиме синхронизации - выделение необходимых программ и последовательностей состояний вычислительной машины и т.п., а также осуществляет управление блоком 17.

На фиг. 3 позициями 27-43 обозначены входы и выходы блока 10, а также линии соединений входов и выходов блоков устройства, показанных на фиг. 1, 2, 4, 5, 6, 7, 9 и 10.

Блок 17 выходных регистров (фиг. 4) состоит из семи элементов ИЛИ 44-50 и десяти регистров 51-60. На фиг. 4 позициями 61-77 обозначены входы и выходы блока 17, а также линии соединений входов и выходов блоков устройства, приведенных на фиг. 1, 2, 6, 7, 8, 9 и 10.

Блок 12 шинных формирователей и дешифратора адресов (фиг. 5) содержит формирователи 78 и 79, регистр 80 и дешифратор 81 адреса. На фиг.5 позициями 82-84 обозначены входы блока 12, позиций 85 - первый выход дешифратора адресов 81, а позициями 86-91 - выходы блока 12, кроме того, позициями 82-84 и 86-91 на фиг. 1, 2, 6, 9 и 10 обозначены линии соединений входов и выходов блоков уст20

25

30

Блок 16 управления (фиг. 6) содержит вход 92, генератор 93, тактовых импульсов, программируемую логическую матрицу 94, три RS-триггера 95-97, шинный формирователь 98 и программируемую схему 99 сравнения. На фиг, 6 позициями 100-102 обозначены входы и выходы блока 16, кроме того, позициями 92, 100, 101 и 102 обозначены линии соединений входов и выходов блоков устройства на фиг. 1, 2, 8 и 10.

Блок 11 контроля времени (фиг. 7) состоит из мультиплексора 103, счетчика 104 и элемента И 105.

Блок 11 может работать в режимах записи в счетчик и счета. На фиг. 7 позициями 09. обозначены входы

и выходы блока 11, вместе

с тем эти

| название | год | авторы | номер документа |

|---|---|---|---|

| УСТРОЙСТВО ДЛЯ СОПРЯЖЕНИЯ ЭВМ С ТЕЛЕФОННЫМИ ЛИНИЯМИ СВЯЗИ | 1992 |

|

RU2006927C1 |

| Устройство для контроля неисправностей | 1987 |

|

SU1564626A1 |

| Многоканальное регистрирующее устройство | 1988 |

|

SU1698899A1 |

| ИМИТАТОР СИГНАЛОВ УПРАВЛЕНИЯ ПОЗИЦИОНИРОВАНИЕМ МАГНИТНЫХ ГОЛОВОК ОТНОСИТЕЛЬНО МАГНИТНЫХ ДИСКОВ | 1991 |

|

RU2017239C1 |

| КОНТРОЛЛЕР | 1991 |

|

RU2012043C1 |

| Измеритель аналоговых сигналов | 1988 |

|

SU1599869A1 |

| Устройство для сопряжения ЭВМ с периферийными устройствами | 1991 |

|

SU1837303A1 |

| Логический анализатор | 1985 |

|

SU1357958A1 |

| Система программного управления технологическими процессами | 1989 |

|

SU1688229A1 |

| Устройство для контроля доменной памяти | 1988 |

|

SU1501160A1 |

Изобретение относится к вычислительной технике и предназначено для выделения состояний вычислительной машины, способной работать в системе, отдельных фаз работы операционной системы, прикладных программ, внешних устройств, процессора, а также для выделения определенной программы или нескольких программ, различных типов прерываний, дискретных событий, отсчета временного интервала с различными тактовыми частотами. Целью изобретения является расширение функциональных возможностей устройства за счет введения новых режимов работы. Устройство для контроля за ходом вычислительного процесса включает блок выделения программ (БВП), блок контроля времени, блок шинных формирователей и дешифратора адресов, блок шинных формирователей, мультиплексор, блок выделения событий, блок управления, блок выходных регистров, блок выделения последовательности событий, блок выделения дискретных событий. Применение предлагаемого устройства в процессе экспериментального исследования надежности структурно-избыточных управляющих вычислительных систем позволит значительно повысить достоверность получаемых оценок надежности. 1 з.п.ф-лы, 16 ил, 2 табл.

состоит из буферного регистра 20, регистра 21 обратной связи, регистра- формирователя 22, оперативной памяти

ми же позициями обозначены линии соединений входов и выходов блоков устройства на фиг. 1, 2, 8, 10.

Блок 15 выделения событий фиг.8 представляет собой программируемую схему J10 сравнения, в состав которой входят пять элементов ИСКЛЮЧАЮЩЕЕ ИЛИ 111.1-111.5, пять элементов 2-И-НЕ 112.1-112.5 и элемент 5-И 113. На фиг. 8 позициями 114-116 обозначены входы и выходы блока 15, а также линии соединений входов и выходов блоков устройства, показанных на фиг. 1, 2, 9 и 10.

БлГок 19 выделения дискретных событий (фиг. 9) состоит из шинного формирователя 117, программируемой схемы 118 сравнения, двух элементов И 119 и 120, счетчика 121, оперативной памяти 122 и мультиплексора 123. На фиг. 9 позициями 124-127 обозна- чены входы и выходы блока 19, а также линии соединений входов и выходов блоков устройства, приведенных на фиг. 1, 2 и 10.

Блок 18 выделения последовательности событий (фиг. 10) содержит счетчик 128, оперативную память 129, схему 130 сравнения, мультиплексор 131, элемент ИЛИ 132 и дешифратор 133 разрешения работы. На фиг. 10 позицией 134 обозначен выход блока 18, а также линия соединения выхода блока 18 с блоками устройства для контроля за ходом вычислительного процесса (фиг. 1 и 2).

Блок 10 выделения программ предназначен для выделения отдельных участков программ и подпрограмм, выделения заданного количества обращений к подпрограммам или заданного количества срабатываний определенных участков программ, обращений к внешним устройствам и т.д.

Буферный регистр 20 предназначен для хранения нового адреса, вырабатываемого оперативной памятью 23 на время, необходимое для записи данных по старому адресу в эту память.

Регистр 21 обратной связи и регистр-формирователь 22 предназначены для хранения адреса при записи или чтении информации в оперативную память 23.

Оперативная память 23 предназначена для хранения информации, необходимой для синхронизации с вычислительным процессом.

Счетчик 24 циклов предназначен дл подсчета количества циклов, обращений к подпрограммам и т.п.

Дешифратор 25 предназначен для управления записью информации в блоки 1 7 и 11 .

Шинный формирователь 26 предназначен для подключения магистрали миниЭВМ 3 к информационному входу регистра 21.

Блок 17 выходных регистров пред- Q назначен для хранения информации в блоках 16, 15, 11, 18 и 19 и мультиплексоре 14.

Элементы ИЛИ 44-50 предназначены для выбора управляющего сигнала на 5 регистры 51, 52, 54-57 и 59.

Регистры 51 и 52 предназначены для хранения информации, поступающей в программируемую схему 99 сравнения; регистр 53 - для хранения информации 0 о том, что нужная программа выделана, поступающей в программируемую схему 110 сравнения; регистры 54 и 55 - для хранения информации, необходимой для функционирования программируемой схе- 5 мы 18 сравнения; регистры 56 и 57 - для хранения информации, поступающей в программируемую схему 110 сравнения; регистр 58 - для хранения информации, необходимой для управления 0 мультиплексором 103; регистр 59 - для хранения информации, необходимой для управления мультиплексором 14; peri гистр 60 - для хранения информации о том, какая программа выделена, по- 5 ступающей в схему 130 сравнения.

Блок 12 шинных формирователей и дешифратбра адреса предназначен для управления записью в различные элементы устройства 1, для контроля за 0 ходом вычислительного процесса, а также для связи с миниЭВМ 3.

Шинный формирователь 78 предназначен для подключения магистрали миниЭВМ 3 к информационным входам 5 регистров JZO, 21, 22, 51-60 и счетчиков 121 и 128, а шинный формирователь 79 - для подключения магистрали миниЭВМ 3 к. регистру 80.

Регистр 80 предназначен для хра- 0 нения информации, поступающей на информационные входы оперативных запоминающих устройств 23, 122 и .129.

Дешифратор 81 адреса предназначен 5 ,для преобразования информации из мини- ЭВМ 3 в управляющую информацию для записи в регистры 80, 51, 52, 54-57 и 59, программируемую логическую матрицу 94, счетчик 121, оператив

ную память 122, счетчик 128 и оперативную память 129.

Блок 16 управления предназначен для формирования управляющих сигналов в регистры- 21, 22, 20, оперативную память 23 и -счетчик 24 циклов.

Генератор 93 тактовых импульсов предназначен для выработки тактовых частот Т1 и Т2.

Программируемая логическая матрица 94 предназначена для выработки управляющих сигналрв в зависимости от комбинации сигналов на входе.

RS-триггер 95 предназначен для хранения сигнала, поступающего на десятый вход программируемой логической матрицы 94} RS-триггер 96 - для хранения сигнала, поступающего на одиннадцатый вход программируемой логической матрицы 94 и на вход -1 счетчика 24 циклов,. RS-триггер 97 - для хранения информации о том, что счетчик 24 циклов равен нулю.

Шинный формирователь 98 предназначен для связи магистрали ЭВМ с программируемой схемой 99 сравнения.

Программируемая схема 99 сравнени предназначена для выделения заранее запрограммированного сигнала.

Блок 11 контроля времени предназначен для отсчета временного интервала с различными тактовыми час.тотами.

Мультиплексор 103 Предназначен дл подключения к входу -1 счетчика 10 одного из информационных входов в зависимости от комбинации на управляющих входах.

Счетчик 104 предназначен для отсчета временного интервала (заранее записанного) с различными тактовыми частотами.

Элемент И 105 предназначен для пропуска сигнала -0 счетчика 104 в случае, если на втором входе элемента есть разрешающий сигнал из дешифратора 133 разрешения работы. Блок 15 выделения событий, представляет собой программируемую схему 110 сравнения и предназначен для выработки сигнала в случае выполнения заданных условий.

Блок 19 выделения дискретных событий предназначен для выделения необходимых сигналов или их последовательностей.

Шинный формирователь 117 предназначен для соединения магистрали ЭВМ

0

5

0

5

0

0

5

0

5

с программируемой схемой 118 сравнения.

Программируемая схема 118 сравнения предназначена для выделения заранее запрограммированного сигнала.

Элементы И 119 и 120 предназначены для пропуска сигналов с выходов схемы 118 и оперативной памяти 122 в случае, если на вторые входы элементов поступает разрешающий сигнал из дешифратора 133 разрешения работы.

Счетчик 121 предназначен для перебора по порядку адресов оперативной памяти 122.

Оперативная память 122 предназначена для хранения информации, необходимой для выделения последовательности однотипных событий. | Мультиплексор f23 предназначен для подключения одного из информационных входов к входу +1 счетчика 121 в зависимости от комбинации на управляющих входах.

Блок 18 выделения последовательности событий предназначен для выделения разнородных последовательностей событий.

Счетчик 128 предназначен для перебора по порядку адресов оперативной памяти 129.

Оперативная память 129 предназначена для хранения информации, необходимой для выделения последовательности событий.

Схема 130 сравнения предназначена для выработки сигнала в случае совпадения информации с четвертого выхода оперативной памяти 129 и с выхода регистра 58.

Мультиплексор 131 предназначен для пропуска сигнала с одного из информационных входов на второй вход элемента ИЛИ 132 при определенной комбинаций на управляющих входах.

Элемент ИЛИ 132 предназначен для выработки сигнала на вход +1 счет- чика 128 в случае наличия сигнала на выходе схемы 130 сравнения или мультиплексора 131.

Дешифратор 133 разрешения работы предназначен для/выработки сигналов разрешения работы в блоках 16, 19 и 11.

Шинный формирователь 13 предназначен для подключения магистрали ЭВМ к информационным входам мультиплексора 14.

9

Мультиплексор 14 предназначен для подключения одного из информационных входов к адресному входу блока 10 в зависимости от комбинации на управляющих входах.

Устройство для контроля за ходом вычислительного процесса предназначено для выделения определенных типов событий, под которыми в дальнейшем будет пониматься работа операционной системы в ЭВМ, пользовательская программа, этапы и фазы выполнения определенной функции, события типа прерывания от внешних устройств наличие определенного числа обращений к внешнему устройству и определенному участку адерсов ОЗУ и т.д., т.е. события, происходящие непосредственно в ЭВМ, информация о которых может быть получена с магистрали ЭВМ и других точек подключения.

Устройство 1 служит для выделения как отдельных событий, их совокупностей, так и для выделения определенной заданной последовательности событий и их совокупностей и может найти применение для сбора статистической информации о поведении ЭВМ, работающей в реальном масштабе времени, а также при экспериментальном ис следовании надежности и устойчивости ЭВМ к различным типам отказов и сбоев. В последнем случае выходы блока выделения событий и блока выделения последовательности событий могут быт подключены непосредственно в точку, в которой будет проимитирована неисправность, или же управлять специально разработанным имитатором неисправностей.

Работа устройства начинается посл предварительной записи блоков выделения программ 10, выделения последовательности событий 18 и выделения дискретных событий 10, в которых записываются ОЗУ информацией, необходи мой для выделения отдельных событий или их последовательностей.

В исходном состоянии регистры 51- 60 сброшены. Для того, чтобы устройство начало работу по выделению определенных событий, необходимо в счетчик 128 записать начальный адрес оперативной памяти 129, по которому хранится информация для дешифратора 133 разрешения работы. После этого нужно задать начальные условия для работы блока 16 управления, которые

10

15

20

39780ю

задаются регистрами 51 и 52. Регистры 54 и 55 задают начальные условия работы блока 19 выделения дискретных событий. Регистры 56 и 5 5 задают начальные условия работы блока 15 выделения событий. Регистр 59 настраивает мультиплексор 14 на подключение соответствующей шины и хранит сигнал Чтение для оперативной памяти,129.

Появление на выходе дешифратора 133 разрешения работы соответствующих сигналов разрешения определяет нач-ало работы устройства.

Появление единичного сигнала на линии 100 разрешает работу блока 10 выделения программ, появление единичного сигнала на линии 109 - работу блока 11 контроля времени, а появление единичного сигнала на линии 125 - работу блока 19 выделения дискретных событий.

Таким образом, блок выделения пос- 25 ледовательности событий координирует работу блоков выделения программ, контроля времени и выделения дискретных событий.

Шинный формирователь 78, регистр 30 80, шинный формирователь 26, буферный регистр 20, оперативная память 23, счетчик 24 циклов и мультиплексор 14 являются элементами с тремя состояниями на выходах (0,1, Отключено). Отказы элементов исключаются благодаря тому, что в каждый момент времени на передачу работает только один из элементов, подключенных к одной шине. Табл. 1 и 2 показывают как. в зависимости от режима работы изменяются состояния элементов 26, 23, 80, 20 и 24 (табл. 1) и элементов 14 и 78 (табл. 2).

Запись начальных условий состоит из трех этапов: 1 - запись в регистры 21 и 22; II - запись в регистр 80; III - выработка управляющих сигналов.

Перезапись счетчика состоит из следующих этапов: 1 - запись информа- 0 ции в счетчик 24 циклов; II - изменение содержимого счетчика 24 циклов; III - перезапись содержимого счетчи- .ка в оперативную память 23; IV - запись нового адреса в регистр 21 из регистра 20.

Блок 10 (фиг. 3).работает в следующих режимах: I - запись в опер-а- тивную память 23; II - выделение последовательностей событий (в частности

35

40

45

5

программ); III - выделение заданного числа повторяющихся событий.

В первом режиме на информационный вход оперативной памяти 23 по маги- , страли 34 поступают данные, зафиксированные в регистре 80, затем на адресные входы оперативной памяти 23 поступает информация из регистров 21 и 22, записанная туда из миниЭВМ через шинные формирователи 78 и 26. Затем из программируемой логической матрицы 94 вырабатываются сигналы Запись и ВК в оперативную память 23 (по линиям 37 и 38).

Во втором режиме в исходном состоянии в регистре 21 записан нулевой код. Этот код записывается в регистр всякий раз, когда сравнение оказалось неудачным. На регистр 22 поступает код, соответствующий начальному событию. Информация на регистрах 21 и 22 составляет адрес, по которому в оперативную память 23 записан код, поступающий в регистр 21. Далее вслед за начальным поступает код второго события и т.д.

Если искомая последовательность найдена, то на конечном этапе поиска единица с выхода D2 оперативной памяти 23 поступает в регистр 53, запись в который разрешает сигнал с дешифратора 25. Во всех ячейках,памяти, не занятых в выделении последовательности, записаны нули, поэтому любой срыв с цепочки вновь приведет в начальную точку поиска, в которой содержимое регистра 21 равно нулю и ожидается появление первого события. Устройство может быть запрограммировано на одновременный поиск нескольких сообщений, а также на выполнение арифметических операций, на проверку соотношений между числами, на проверку попадания чисел в заданные границы и т.д.

Во втором режиме может быть выделена последовательность адресов. Временная диаграмма, поясняющая этот режим работы для интерфейса ИУС приведена на фиг. И. Возможно применение устройства и в других интерфейсах, при этом изменится только логика функционирования программируемой логической матрицы 94.

На фиг. 11 при появлении адреса на шине адреса данных (А/Д) стано- | вится активной шина признака адреса (ШПРА), которая активизирует шину

5

0

подтверждения признака адреса (ШППА). Активизация ШППА вызывает сброс сигнала ШПРА, который сбрасывает сигнал ШППА. Активный уровень ШПРА вызывает срабатывание схемы 99 и появление сигнала синхронизации (СС), который поступает в программируемую логическую матрицу 94, где вырабатывается сигнал Запись в регистр 22 (ЗпРФ). По переднему фронту сигнала ЗпРФ производится запись адреса в регистр 22. По единичному значению ЗпРФ вырабатывается сигнал ВК оперативной памяти 23, которая постоянно находится в состоянии чтения, а следовательно, происходит считывание из оперативной памяти 23. Сигнал ВК сбрасывается по нулевому уровню ЗпРФ. В зависимости от содержимого оперативной памяти 23 дальше могут быть два пути; первый - информация с выхода D4 оперативной памяти 23 вызывает выработку в программируемой логической матрице 94 сигнала Запись в регистр 21 (ЗпРОС) и затем фиксацию информации с выхода D1 оперативной памяти 23 в регистр 21; второй - состояние выхода D3 оперативной памяти 23 определяет

о состояние дешифратора 25, сигнал с выхода которого поступает в блок 17. После того как ШПРА принимает пассивное состояние, происходит сброс сигнала СС, а следовательно, снимается сигнал ЗпРФ.

В этом же режиме может быть выделена последовательность данных. Временная диаграмма, поясняющая этот режим работы приведена на фиг. 12. Она отличается от временной диаграммы на фиг. 11 тем, что сигнал ШПРА заменен инверсией сигнала на шине запроса данных 0НЗД), а сигнал ШППА - сигналом на шине наличия данных

с (ШНД), В остальном эти диаграммы идентичны.

5

5

0

Во втором режиме также может быть выделена и программа. На фиг. 13 показана временная диаграмма, поясняющая этот режим работы. Отличие этой , диаграммы при работе без счетчика циклов 24 от диаграммы на фиг. 12 состоит в том, что сигнал СС вырабатывается nocrfe появления активного уровня сигнала признака команды (К) на магистрали 4. В остальном временные диаграммы для второго режима на фиг. 12 и 13 аналогичны.

В третьем режиме возможно выделение программ с использованием счетчика циклов 24,подсчитывающего циклы в программе. Этот режим работы поясняете временными диаграммами на фиг. 13 и фиг. 14. На фиг. 13 при приходе данных на шину А/Д возбуждается ШЗД, что вызывает активизацию ШНД. По фронту сигнала ШНД сигнал ШЗД переходит в пассивное состояние, что вызывает сброс ШНД. Одновременно с ШЗД на магистрали 4 появляется сигнал К, активный уровень которого обуславливает срабатывание схемы 99, запрограммированной на это, и появление сигнала СС на входе программируемой логической матрицы 94. При этом на выходе ее активизируется сигнал ЗпРФ По переднему фронту сигнала ЗпРФ производится запись в регистр 22. По единичному уровню ЗпРФ вырабатывается сигнал ВК, который влечет за собой считывание из оперативной памяти 23 и, следовательно, смену состояния его выходов. Состояние выходов D4 оперативной памяти 23 вызывает появление сигнала ЗпСЦ. По переднему фронту этого сигнала производится запись информации с выхода . D2 оперативной памяти 23 в счетчик циклов 24. Единичный уровень ЗпСЦ поддерживает в активном состоянии сигнал ВК.

Дальнейшая работа показана на фиг. 14. Из этой временной диаграммы видно, что для появления сигнала ЗпСЦ также необходимо нулевое значение входов Зп/Чт оперативной памяти 23 и единичное значение 0 счетчика циклов, те же условия нужны и для появления активного сигнала на S-входе RS-триггера 96 (S 96) и на линии ЗпБР, что приводит к записи в регистр 20 информации с выхода D1 оперативной памяти 23. По переднему фронту сигнала S 96,триггер 96 устанавливается в единичное состояние (единица на выходе XI2) и активизируется вход -1 счетчика циклов 24,, а по уровню этого сигнала переходит Е пассивное состояние сигнал установки в третье состояние счетчика циклов 24, что приводит к появлению информации на выходе счетчика циклов 24. Сигнал XI2 и такт Т2 вызывают появление активного уровня на S-входе RS-триггера-95 (S 95).По переднему фронту этого сигнала уста0

5

0

навливаелся в 1 триггер 95 (появляется 1 на выходе XII), что приводит к появлению сигнала Зп оперативной памяти 23 и совместно с 1 на выходе XI2 и тактом Т1 Сброс (R-входы) 95 и 96 триггеров. По нулю Т2 сбрасывается сигнал S 95. Зп ОЗУ23-1 приводит к сбросу сигналов ЗпСЦ, S 96, ЗпРБ. Передний фронт сигнала R 95,96 вызывает сброс сигналов Х12, -1 СЦ, Х12, ноль на входе -1СЦ влечет за собой сброс сигнала СЦ, что приводит к третьему состоянию на выходе счетчика циклов 24. Нулевой уровень сигнала XII вызовет сброс сигнала Зп ОЗУ23, нулевой уровень 11 - сброс сигнала R 95, 96. Нулевой уровень сигнала ЗпСЦ вызывает сброс сигнала ВК, что приводит- к переключению в третье состояние выходов оперативной памяти 23 и к пассивному состоянию на входе - третье состояние регистра 20 (совместно с еди- 5 ницей на выходе 0 СЦ). Ноль на входе БР приводит к тому, что на выходе регистра 20 появляется информация, а совместно с тактом Т1 - к тому, что вырабатывается сигнал ЗпРОС, который сбрасывается по нулю Т1. Передний фронт ЗпРОС обуславливает фиксацию в регистре 21 информации с выхода регистра 20.

В случае, если после вычитания единицы из счетчика циклов 24 появится нулевой сигнал на выходе ОСЦ, он вызовет сброс сигналов ЗпСЦ, S 96 и ЗпБР, появление сигнала ЗпРОС (по такту Т1) и запрет на выработку сигнала ЗпОЗУ.

Блок 17 (фиг. 4) служит для хранения информации. Регистры 51, 52, 54-57 и 59 могут записываться из оперативной памяти 23 (выход D2) и из миниЭВМ 3 через шинный формирователь 78, а регистры 53, 58 и 60 - только из оперативной памяти 23.

Шинные формирователи 78 и 79, входящие в состав блока 12 (фиг. 5), постоянно настроены на прием из мини- ЭВМ 3 при отсутствии сигнала третье состояние. Дешифратор адреса 81 принимает по магистрали 84 из мини- ЭВМ 3 управляющий код и вырабатывает сигнал, разрешая запись в регистры 51, 52, 54-57, 59, 80, программируемую логическую матрицу 94, счетчики 121, 128, ОЗУ 122, 129. Блок 16 (фиг. 6) выделяет заданные признаки,

0

5

0

5

0

5

151

поступающие по магистрали 102 из ЭВМ 5. Для интерфейса ИУС на вход шинного формирователя 98 поступают сигналы ШПРА, ШЗД и К, которые можно взять с центрального процессора 6. Информация, необходимая для выделения признаков, хранится в регистрах 51 и 52. По шине 68 в схему 99 поступают данные, несущие информацию о необходимом логическом уровне выделяемого признака, а по шине 69 - о необходимости выделения данного признака. Через XI в программируемой логической матрице 94 обозначен вход разрешения работы, на который по линии 100 поступает сигнал из дешифратора 133, а через Х2 и ХЗ - входы связанные линиями 86, 87 с дешифратором 81. На вход Х4 поступает сигнал Сброс с линии 27. На входы Х5, Х6 - тактовые импульсы-Т и Т2 с генератора тактовых импульсов 93. Х7 - вход, на который поступает сиг-

нал 0 с счетчика циклов 24. Х8, Х9 - входы, на которые поступает информация с выхода D4 оперативной памяти 23 по магистрали 39. XIО - это СС из схемы 99. XII - выход RS-триг- гера 95, а XI2 - выход RS-триггера 96. XI3 - сигнал с выхода D1 оперативной памяти 129. У1 в программируемой логической матрице 94 - ЗпБР, по линии 31 поступающий в регистр 20, устанавливающий RS-триггера 96 в единичное состояние, и сигнал ЗпСЦ, по линии 41 поступающий в счетчик 24; У2 - ЗпРОС, по линии 32 поступающий в регистр 21; УЗ - ЗпРФ по линии 33 поступающий в регистр 22; У4 - 3/Чт, по линии 37 поступающий в оперативную память 23; У5 - установка RS- триггера 95 в единичное состояние; У6 - ВК, по линии 38 поступающий в оперативную память 23; У7 - сброс в нулевое состояние RS-триггеров 95 и 96; У8 - установка в третье состояние регистра 20; У9 - установки в третье состояние счетчика 24; У10 - сброс RS-триггера 97 в нулевое состояние, У11 - управление шинным формирователем 26. /

Логика работы программируемой логической матрицы 94 для интерфейса ИУС описывается следующими уравнениями;

X11VX3 Х8 Х9 Х7; У2 Х8 Х9УХ5 X7VX2 X6VX5

(XI X10VX2 X6VX12VX3)

0

16

(XII X12VX4); X10VX2 Х6; X11VX3;

y5 X6VX12;

y6 X VX10VX2VX6VX12VX3; Xll X12VX4;

15

30

35

40

45

50

55

У8(Х1 XIО Х2 Х6 XI2 ХЗ) Х7;

10 У10 Х4УХ13; УП Х2УХ5

Работа триггеров 95-97 пояснена на временной диаграмме на фиг. 14.

Блок 11 (фиг. 7) работает следующим образом.

В счетчик 104 по магистрали 29 из оперативной памяти 23 записьюается временной интервал (сигнал Запись 2Q поступает аз дешифратора 25). Мультиплексор 103 по магистрали 74 из регистра 56 настраивается на подключение шины, на которой присутствует определенная частота. Работа начина- 25 ется после прихода сигнала Разрешение счета. После обнуления счетчика 104 вырабатывается сигнал 107 в схеме 110, а при наличии сигнала Разрешение работы из дешифратора 133 - и в мультиплексоре 131.

Работа блока 15 (фиг. 8), представляющего собой схему 110, заключается в выявлении сигналов, несущих информацию о выделении программы (линия 70 из регистра 53), о нулевом состоянии счетчика 24 (линия 101 из RS-триггера 97), о нулевом состоянии счетчика 104 (линия 107 из счетчика 104), о появлении какого-°либо события или их последовательности (линии 114 и 115 из схемы 118 и ОЗУ122 соответственно). Схема 110 программируется в регистрах 56 и 57 и получает информацию из них по шинам 73 и 74.

Блок 19 (фиг. 9) может выделять как отдельное событие, так и их последовательность. Отдельное событие, под которым понимается появление заданного уровня сигналов, например сигнала прерывания, выбирается с помощью схемы 118. Вся информация относительно того, какое событие и каким логическим уровнем должно быть выделено, записывается в регистры 54 и 55

и поступает в (усему 118 по шинам 71 и 72. События из ЭВМ 5 поступают через шинный формирователь 117. Работа схемы 118 аналогична работе схемы 99. Сигнал о выделенном событии по линии

17

114 поступает в схему 110, а при наличии сигнала Разрешение работы из дешифратора 133 - в мультиплексор 131. Другая часть блока 19 предназначена для выделения последовательности событий. Первоначально необходимо в оперативную память 122 занести информацию, для этого на вход оперативной памяти 122 подаются данные из регистра 80 по шине 34, затем при поступлении сигнала из дешифратора 81 по ли линии 88, в счетчике 121 фиксируется адрес, а после этого на оперативную память 122 с дешифратора 81 по линии 89 передается сигнал Зап и производится запись информации в опера- .тивную память 122.

Работа блока 19 в режиме выделения последовательности событий поясняется временной диаграммой на фиг. 15. По переднему фронту сигнала Уст 0, приходящего по линии 27, счетчик 121 устанавливается в нуле30

35

вое состояние. При появлении на входе 25 дешифратор 133 разрешил работу, пооперативней памяти 122 сигнала чтение (Чт) на ее выходе появляется информация, настраивающая мультиплексор 123 на пропуск тактируемого сигнала по одной из линий 124(1)-124(п). При появлении этот сигнал поступает на вход +1 счетчика 121, изменяя информацию на адресном входе оперативной Iпамяти 122 и т.д. При появлении пос- леднего события сигнал с выхода D1 оперативной памяти 122 по линии 115 поступает в схему 110, а при наличии сигнала Разрешение работы из дешифратора 133 и в мультиплексор 131.

Блок 18 (фиг. 10) способен выделять до различного типа, последовательности различных программ, сигналов, состояний и т.п. Перед началом работы необходимо занести информацию в оперативную память 129. Для этого на D-вход оперативной памяти 129 из регистра 80 по магистрали 34 поступают данные, в счетчик 128 из миниЭВМ 3 через шинный формирователь 78 по магистрали 28 посту- пает адрес, который записывается в счетчик 128 при наличии разрешающего сигнала на линии 90 из дешифратора 81. Затем, когда поступает сигнал записи по линии 91 из дешифратора 81, в оперативную память 1.29 производится запись информации.

Работа блока 18 поясняется временной диаграммой на фиг. 16. По переднему фронту сигнала Уст 0, пост

45

является единица на выходе мультиплексора 131, которая поступает на вход +1 счетчика 128. По переднему фронту этого сигнала изменяется содержимое счетчика 128, а затем и состояние выходов оперативной памяти 129. И если это последнее событие, то появляется сигнал на выходе D1 оперативной памяти 129, на выходе мультиплексора 131 появляется О, а, следовательно, О и на входе . +1 счетчика 128.

Предлагаемое устройство позволяет программировать выделение событий

а также их последовательностей при экспериментальном исследовании поведения вычислительны систем, работающих в реальном масштабе времени.

Формула

изобретения

50

55

978018

тупающего по линии 27,

производится

установка в 0 счетчика 128. Содержимое счетчика 128 поступает на адресный вход оперативной памяти 129, и при наличии сигнала чтение (Чт) на его выходах появляется считанная информация, которая, поступая на дешифратор 133, разрешает работу одного

Ю из блоков устройства 1 (на диаграмме программируемой логической матрицы 94) а после прихода информации с этого блока срабатывает схема сравнения 130, сигнал с выхода которой

J5 поступает на вход +1 счетчика 128. Состояние счетчика 128 изменится, а затем изменится информация на выходах оперативной памяти 129, которая изменяет состояние дешифратора 133 и

20 сбрасывает схему сравнения 130 в .

ноль. Нулевое состояние схемы сравнения 130 обуславливает такое же состояние и на входе +1 счетчика 128. При приходе сигнала с блока, которому

дешифратор 133 разрешил работу, поразличного типа,

является единица на выходе мультиплексора 131, которая поступает на вход +1 счетчика 128. По переднему фронту этого сигнала изменяется содержимое счетчика 128, а затем и состояние выходов оперативной памяти 129. И если это последнее событие, то появляется сигнал на выходе D1 оперативной памяти 129, на выходе мультиплексора 131 появляется О, а, следовательно, О и на входе . +1 счетчика 128.

Предлагаемое устройство позволяет программировать выделение событий

а также их последовательностей при экспериментальном исследовании поведения вычислительных систем, работающих в реальном масштабе времени.

Формула

изобретения

различного типа,

четвертым, пятым, шестым и седьмым выходами блока управления, управляющий выход блока выделения программ соединен с синхровходом блока контроля времени и первым входом управления записью блока выходных регистров, первый информационный выход блока выделения программ соединен с вторым информационным входом блока выходных регистров и первым информационным входом блока контроля времени, второй информационный выход бло- ка выделения программ соединен с первым информационным входом блока упп- равления, второй информационный вход которого соединен с третьим информационным выходом блока выделения программ, второй информационный вход блока контроля времени является входом устройства для подключения к шин управления интерфейса исследуемой ЭВМ, адресный вход блока контроля времени соединен с первым выходом блока выходных регистров, разрешающий вход блока контроля времени соединен с первым выходом блока выделения последовательности событий, первый выход блока контроля времени соединен с первым информационным входом блока выделения событий, второй выход блока контроля времени соединен с третьим информационным входом блока выделения последовательности событий, первый и второй информационные входы блока шинных формирователей и дешифратора адресов являются соответственно первьм и вторым входами адреса/данных устройства разрешающие входы блока шинных формирователей и дешифратора адресов и мультиплексора соединены с вторым выходом блока выделения последовательности событий, первый и второй входы управления записью блока выделения дискретных событий соединены соответственно с первым и вторым управляющими выходами блока шинных формирователей и дешифратора адресов третий и четвертый управляющие выходы которого соединены соответственно с третьим и четвертым информационными входами блока управления, пятый уп- равляющий выход блока шинных формирователей и дешифратора адресов соединен с вторым входом управления записью блока выходных регистров, шестой и седьмой управляющие выходы блока шинных формирователей и дешифратора адресов соединены соответственно с первым и вторым входами управления записью блока выделения последовательности событий, информационный вход блока шинных формирователей является входом устройства для подключения к шине адреса/данных интерфейса исследуемой.ЭВМ, выход блока шинных формирователей соединен с первым информационным входом мультиплексора, с второго по n-й информационные входы мультиплексора являются входами устройства для подключения к соответствующим магистралям исследуемой ЭВМ, адресный вход мультиплексора соединен с вторым выходом блока выходных регистров, второй информационный вход блока выделения событий соединен с восьмым выходом блока управления, третий выход блока выходных регистров соединен с третьим информационным входом блока выделения событий, входы задания уровня сигналов и разрешения сравнения которого соединены соответственно с четвертым и пятым выходами блока выходных регистров, четвертый и пятый информационные входы блока выделения событий соединены соответственно с первым и вторым выходами блока выделения дискретных событий, выход блока выделения событий является выходом Событие выделено устройства и соединен с четвертым информационным входом блока выделения последовательности событий, пятый информационный вход блока управления является входом устройства для подключения к шине управления интерфейса исследуемой ЭВМ, шестой информационный вход блока управления соединен с шестым выходом блока выходных регистров, седьмой и восьмой информационные входы блока управления соединены с третьим и чет- вертым выходами блока выделения последовательности событий, седьмой и восьмой выходы блока выходных регистров соединены соответственно с входами задания уровня сигналов и разрешения сравнения блока выделения дискретных нЕобытий, девятый и десятый выходы блока выходных регистров соединены соответственно с пятым информационным входом и входом управления чтением блока выделения последовательности событий, третий и четвертый выходы блока выделения дискретных событий соединены соответственно с

0

5

0

5

0

5

0

5

0

5

шестым и седьмым информационными входами блока выделения последовательности событий, пятый выход которого соединен с разрешающим входом блока выделения дискретных событий, третий информационный вход которого является входом устройства для подключения к шине управления интерфейса исследуемой ЭВМ, шестой выход блока выделения последовательности событий явля ется информационным выходом устройства, причем блок выделения программ содержит буферный регистр, регистр обратной связи, регистр-формирователь, оперативную память, дешифратор и шинный формирователь, причем входы сброса бз ферного регистра, регистра обратной связи и регистра-формирователя подключены к входу первоначальной установки блока выделения программ, информационный вход буферного регистра соединен с первым выходом оперативной памяти и выходом шинного формирователя, входы записи буферного регистра, регистра обратной связи и регистра-формирователя подключены к группе входов управления записью блока выделения программ, вход разрешения буферного регистра соединен с первым разрешающим входом блока выделения программ, выход буферного регистра соединен с информационным входом регистра обратной связи, первым выходом оперативной памяти и выходом шинного формирователя, информационный выход регистра обратной связи подключен к первому адресному входу оперативной памяти, информационный вход регистра-формирователя соединен с вторым информационным входом блока выделения программ, выход регистра- формирователя подключен к второму адресному входу оперативной памяти, / первый информационный вход оперативной памяти соединен с первым выходом этой же оперативной памяти, с выходом шин-1 ного формирователя и первым информационным входом блока выделения программ, второй информационный вход оперативной памяти подключен к информационному выходу счетчика циклов и первому информационному входу блока выделения программ, третий информационный вход оперативной памяти сое- дине с вторым выходом этой же оперативной памяти и первым информационным входом блока выделения программ, четвертый информационный вход оперативной памяти подключен к третьему выход этой же оперативной памяти и первому информационному входу блока выделения программ, вход записи-чтения оперативной памяти подключен к первому - входу управления записью блока выделения программ, вход выбора кристалла оперативной памяти - к входу выбора кристалла блока выделения программ, четвертый выход оперативной памяти соединен с информационным входом счетчика циклов и первым информационным выходом блока выделения программ, второй выход оперативной памяти подключен к входу дешифратора, третий выход оперативной памяти соединен с вторым информационным выходом блока выделения программ, вход записи счетчика циклов подключен к второму входу управления записью блока выделения программ, вход разрешения счетчика циклов - к второму входу раз-, решения блока выделения программ, выход обнуления счетчика циклов соединен с третьим информационным выходом блока выделения программ, выход дешифратора подключен к управляющему выходу блока выделения программ, информационный вход шинного формирователя соединен с вторым информационным входом блока выделения пррграмм, вычитающий вход счетчика циклов и управляющий вход шинного формирователя подключены соответственно к входам счета циклов и управления приемом информации блока выделения программ, причем блок шинных формирователей и дешифратора адресов содержит первый и второй шинные формирователи, регистр и дешифратор адреса, причем информационные входы шинных формирователей подключены к первому информационному входу блока шинных формирователей и дешифратора адресов, управляющий вход первого шинного формирователя и вход разрешения регистра соединены с разрешающим входом блока шинных формирователей и дешифратора адресов, информационный выход первого шинного формирователя соединен с вторым информационным выходом блока шинных формирователей и дешифратора адресов, информационный выход второго шинного формирователя подключен к информационному входу регистра, вход записи которого соединен с первым выходом дешифратора адресов, выход регистра подключен к первому информационному

5

5

выходу блока шинных формирователей и дешифратора адресов, информационный вход дешифратора адресов соединен с вторым информационным входом блока шинных формирователей и дешифратора адресов, выходы дешифратора адресов, начиная с второго, образуют с первого по седьмой управляющие выходы блока шинных формирователей и дешифратора адресов, причем блок контроля времени содержит мультиплексор, счетчик и элемент И, информационный вход мультиплексора подключен к второму информационному входу, блока контроля времени, адресный вход мультиплексора соединен с адресным входом блока контроля времени, вБкод мультиплексора подключен к вычитающему входу счетчика вход сброса счетчика соединен с входом управления первоначальной установкой блока контроля времени, вход записи счетчика соединен с синхровходом блока контроля времени, информационный вход счетчика подключен к первому информационному входу блока контроля времени, вход разрешения счетчика соединен с разрешающим входом блока контроля времени, выход обнуления счетчика соединен с первым входом элемента И и первым выходом блока контроля времени, второй вход,элемента И подключен к разрешающему входу блока контроля времени, выход элемента И соединен с вторым выходом блока контроля времени, причем блок выделения дискретных событий содержит шинный формирователь, схему сравнения, два элемента И, счетчик, оперативную память и мультиплексор, причем информационный вход шинного формирователя подключен к третьему информационному входу блока выделения

с дискретных событий, выходы шинного формирователя соединены с первой группой информационных входов схемы сравнения, вторая группа информационных входов которой подключена

0 к входу задания уровня сигналов блока выделения дискретных событий, группа разрешающих входов схемы сравнения соединена с входом разре- . шения сравнения блока выделения дисс кретных событий, выход схемы сравнения подключен к первому выходу блока выделения дискретных событий и первому входу первого элемента И, второй вход первого и первый вход второго

0

5

0

элементов И соединены с разрешающим входом блока выделения дискретных событий, выход первого элемента И подключен к третьему выходу блока выделения дискретных событий, второй вход второго элемента И соединен с первым вых одом оперативной памяти, выход второго элемента И подключен к четвертому выходу блока выделения дискретных событий, информационный вход счетчика соединен с вторым информационным входом блока выделения дискретных событий, вход сброса счетчика подключен к входу управления первоначальной установкой блока выделения дискретных событий, вход записи счетчика соединен с первым входом управления записью блока выделения дискретных событий, счетный вход счетчика подключен к выходу мультиплексора в блоке выделения дискретных событий, информационный выход счетчика соединен с адресным входом оперативной памяти в этом же блоке, информационный вход оперативной памяти подключен к первому информационному входу блока выделения дискретных событий, вход записи оперативной памяти соединен с вторым входом управления записью блока выделения дискретных событий, вход чтения оперативной памяти подключен к разрешающему входу блока выделения дискретных событий, первый выход оперативной памяти подключен к второму выходу блока выделения дискретных событий, второй выход оперативной памяти соединен с адрес- ным-входом мультиплексора, информационные входы мультиплексора подключены к третьему информационному входу

блока выделения дискретных событий, причем блок выделения последовательности событий содержит счетчик, оперативную память, схему сравнения, мультиплексор, элемент ИЛИ и дешифратор разрешения работы, причем вход

сброса счетчика подключен к входу управления первоначальной установкой блока выделения последовательности событий,-информационный вход счетчика соединен с вторым информационным входом блока выделения последовательности событий, вход записи счетчика подключен к первому входу управления записью блока выделения последовательности событий, счетный вход счетчика соединен с выходом элемента ИЛИ, информационный выход счетчика

0

5

0

подключен к адресному входу оперативной памяти этого же блока, информа- ционный вход оперативной памяти соединен с первым информационным входом блока выделения, последовательности событий, вход записи оперативной памяти соединен с вторым входом управления записью блока выделения последовательности событий, вход чтения оперативной памяти соединен с входом управления чтением блока выделения последовательности событий, первый, второй и третий выходы оперативной памяти являются соответственно шестым, третьим и вторым выходами блока выделения последовательности событий, четвертый выход оперативной памяти соединен с входом дешифратора разрешения работы, пятый выход оперативной памяти подключен к адресному входу мультиплексора в этом же блоке, шестой выход оперативной памяти подключен к первому информационному входу схемы сравнения, второй информационный вход схемы сравнения соединен с пятым информационным входом блока выделения последовательности событий, выход схемы сравнения подключен к Q первому входу элемента ИЛИ, первый, второй, третий и четвертый информационные входы мультиплексора соединены соответственно с четвертым, третьим, шестым и седьмым информационными входами блока выделения последовательности событий, выход мультиплексора подключен к второму входу элемента ИЛИ, первый, второй и третий выходы дешифратора разрешения работы соединены соответственно с четвертым, первым и пятым выходами блока выделения последовательности событий.

5

5

0

ческой матрицы соединены с выводами первого и второго RS-триггеров, двенадцатый , вход программируемой логической матрицы подключен к седьмому информационному входу блока управления, первый, второй и третий выходы программируемой логической матрицы образуют группу выходов блока управления, четвертый выход программируемой логической матрицы соединен с первым выходом блока управления, пятый выход программируемой логической матрицы соединен с S-входом первого RS-триг- гера, шестой выход программируемой логической матрицы подключен к третьему выходу блока управления, седьмой выход программируемой логической матрицы соединен с R-входами первого и второго RS-триггеров, восьмой выход программируемой логической матрицы подключен к шестому выходу блока управления, девятый выход программируемой логической матрицы подключен к седьмому выходу блока управления, десятый выход программируемой логической матрицы соединен с R-входом третьего RS-триггера, одиннадцатый выход программируемой логической матрицы подключен к пятому выходу блока управления, первый выход прог. граммируемой логической матрицы соединен с вторым выходом блока управления, и S-входом второго RS-триггера, выход второго RS-триггера соединен с четвертым выходом блока управления, S-вход третьего RS-триггера подключен к второму информационному входу блока

разрешающих входов которой с с шестым информационным вход управления.

15

20

25

30

Таблиц

35

40

45

Примечание. # - элемент

в третье янии; + - элемент

группа информационных входов

управления, выход третьего RS-триггера соединен с восьмым выходом блока управления, информационный вход шинного формирователя соединен с пятым информационным входом блока управления, выходы шинного формирователя подключены к первой группе информационных входов схемы сравнения, вторая

и группа

разрешающих входов которой соединены с шестым информационным входом блока управления.

Таблица 2

Примечание. # - элемент находится

в третьем состоянии;+ - элемент включен.

Uhtt.t

1539780 t8B66oen

Фиг. 8

71(1)

Фиг. 9

6BP

Фие.И

БШ25 6ВР

Фиг. 12

Фиг. 13

Фиг. 14

Фиг. 15

Уст О

Фиг. 16

| Шевкопляс Б.В | |||

| Микропроцессорные структуры: Инженерные решения | |||

| М., 1986 | |||

| Устройство для имитации неисправностей | 1985 |

|

SU1273933A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1990-01-30—Публикация

1987-06-23—Подача