Изобретение относится к импульсной технике и может быть использовано в аппаратуре обработки цифровой информации, в электронных хрони- заторах ц измерителях времени.

Целью изобретения является расширение функциональных возможностей и повьшение надежности формирователя.

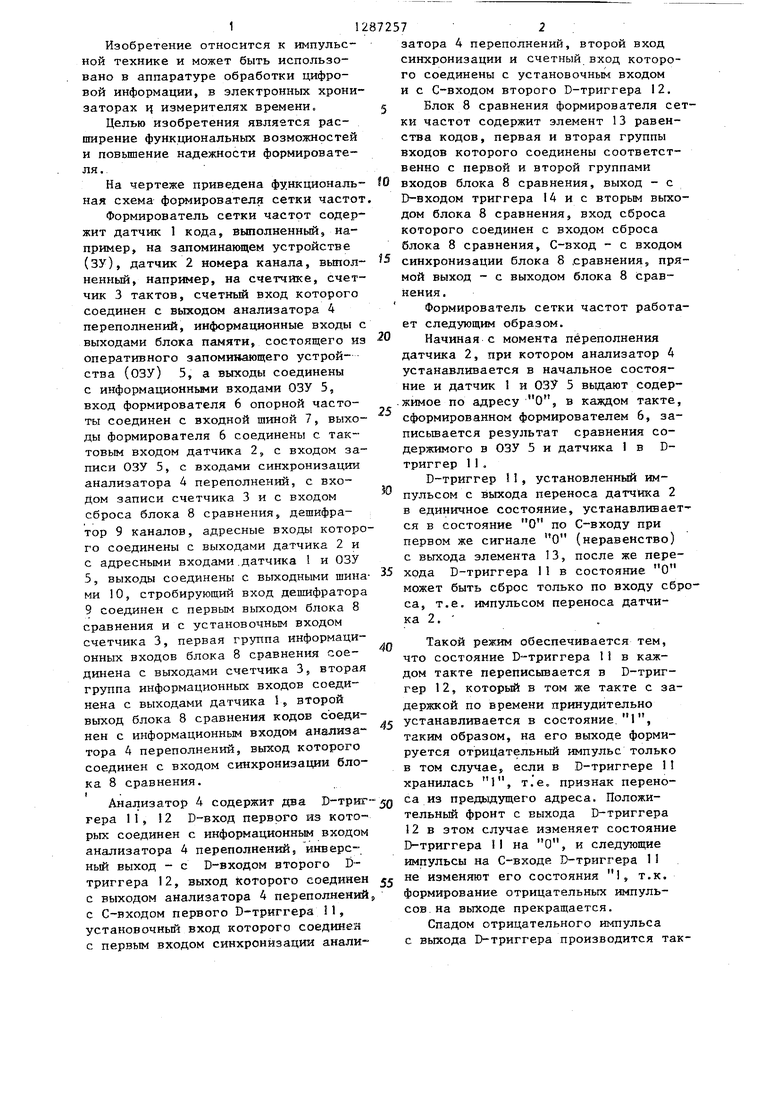

На чертеже приведена функциональная схема формирователя сетки частот

Формирователь сетки частот содержит датчик 1 кода, вьшолненный, например, на запоминающем устройстве (ЗУ), датчик 2 номера канала, вьтол- ненный, например, на счетчике, счетчик 3 тактов, счетный вход которого соединен с выходом анализатора 4 переполнений, информационные входы с выходами блока памяти, состоящего из оперативного запоминающего устрой- ства (ОЗУ) 5, а выходы соединены с информационньми входами ОЗУ 5, вход формирователя 6 опорной частоты соединен с входной шиной 7, выходы формирователя 6 соединены с тактовым входом датчика 2, с входом записи ОЗУ 5, с входами синхронизации анализатора 4 переполнений, с входом записи счетчика 3 и с входом сброса блока 8 сравнения, дешифратор 9 каналов, адресные входы которого соединены с выходами датчика 2 и с адресными входами.датчика 1 и ОЗУ 5, выходы соединены с выходными шинами 10, стробирующий вход дешифратора 9 соединен с первым выходом блока 8 сравнения и с установочным входом счетчика 3, первая группа информационных входов блока 8 сравнения соединена с выходами счетчика 3, вторая группа информационных входов соединена с выходами датчика 1, второй выход блока 8 сравнения кодов соединен с информационным входом анализатора 4 переполнений, выход которого соединен с входом синхронизации блока 8 сравнения.

Анализатор 4 содержит два Б-триг гера 11, 12 D-вход первого из кото™ рых соединен с информационным входом анализатора 4 переполнений, инверсный выход - с D-входом второго D- триггера 12, выход которого соединен с выходом анализатора 4 переполнений с С-входом первого D-триггера 1, установочньй вход которого соединен с первым входом синхронизации анали

затора 4 переполнений, второй вход синхронизации и счетный вход которого соединены с установочным входом и с С-входом второго D-триггера 12,

Блок 8 сравнения формирователя сетки частот содержит элемент 13 равенства кодов, первая и вторая группы входов которого соединены соответственно с первой и второй группами

входов блока 8 сравнения, выход - с D-входом триггера 14 и с вторым выходом блока 8 сравнения, вход сброса которого соединен с входом сброса блока 8 сравнения, С-вход - с входом

синхронизации блока 8 .сравнения, прямой выход - с выходом блока 8 сравнения .

Формирователь сетки частот работает следующим образом,

Начиная с момента переполнения датчика 2, при котором анализатор 4 устанавливается в начальное состояние и датчик 1 и ОЗУ 5 вьщают содер- .жимое по адресу О, в каждом такте, сформированном формирователем 6, за- письшается результат сравнения содержимого в ОЗУ 5 и датчика 1 в D- триггер 1I о

D-триггер 11, установленный импульсом с выхода переноса датчика 2 в единичное состояние, устанавливает- ся в состояние О по С-входу при первом же сигнале О (неравенство) с выхода элемента 13, после же перехода D-триггера 11 в состояние О может быть сброс только по входу сброса, т,е, импульсом переноса датчика 2.

Такой режим обеспечивается тем, что состояние Б триггера 11 в каждом такте переписывается в D-триггер 12, который в том же такте с задержкой по времени принудительно

устанавливается в состояние., таким образом, на его выходе формируется отрицательный импульс только в том случае, если в D-триггере 11 хранилась 1, ч .е, признак переноса из предьщущего адреса. Положительный фронт с выхода D-триггера 12 в этом случае изменяет состояние D-триггера 11 на О, и следующие импульсы на С-входе D-триггера 11

не изменяют его состояния 1, т,к. формирование отрицательных импульсов, на выходе прекращается.

Спадом отрицательного импульса с выхода D-триггера производится также фиксация признака переноса из данного адреса в D-триггер 14 и изменение состояния счетчика 3 на единицу, следовательно, содержимого ОЗУ 5 по данному адресу. Таким образом , при равенстве кодов в ОЗУ 5 и датчике 1 в данном адресе и наличии признака переноса из предьщущего адреса (импульса с выхода D-тригге- ра 12) D-триггер 14 устанавливается по С-входу в единицу и сбрасьгоа- ется по входу сброса. Положительный импульс с выхода D-триггера 14, переданный на С-вход дешифратора 9, появляется на выходной шине 10, имеющей номер, соответствующий данному адресу, а также сбрасьшает счетчик 3 и тем самым обеспечивает запись в ОЗУ 5 О по данному адресу.

Отсюда следует, что на шинах 10 дешифратора 9 последовательности импульсов с частотой следования импульсов, понижающейся с увеличением номера шины с относительным коэффициентом кратности, определяемьм содержимым датчика 1 по адресу, соответствующему номеру шины 10.

Необходимо отметить, что последовательности импульсов на шинах 10 будут сдвинуты друг относительно друга. Частота следования импульсов на шине по соответствующему адресу i может быть определена по формуле

F; Р/(2-А.Д Kj),

где А - коэффициент пересчета счетчика 2;

i - текущий адрес (,1,...,А К:- коэффициент в ЗУ-1 по адресу j 5

F - входная частота (на шине 7) Формула изобретения

Формирователь сетки частот, содержащий счетчик тактов, вход запиор М. Циткина 7725/57

Составитель В. Чижов Техред М.Ходанич

Кор Под

Тираж 899 ВНИИПИ Государственного комитета СССР

по делам изобретений и открытий 113035, Москва, Ж-35, Раушская наб., д. 4/5

Производственно-полиграфическое предприятие, г. Ужгород, ул. Проектная, 4

872574

си которого сое/1инен с первым выходом формирователя опорной частоты, установочный вход соединен с первым выходом блока сравнения, первая груп5 па входов которого соединена с выходами счетчика тактов, вторая группа входов блока сравнения подключена к выходам датчика кода, выходы датчика номера канала соединены с адресными

О входами дешифратора каналов, отличающийся тем, что, с целью расширения функциональных возможностей и повышения надежности формирователя, в него дополнительно вве 5 дены блок памяти, анализатор переполнений, а датчик номера канала выполнен в виде счетчика адреса, выходы которого соединены с адресными входами датчика кода и блока памяти,

20 выходы которого подключены к информационным входам счетчика тактов, выходы которого соединены с информаци- - онными входами памяти, счетный вход счетчика тактов соединен с выходом

анализатора переполнений и входом синхронизации блока сравнения, вход сброса которого соединен с первым выходом формирователя опорной частоты и счетным входом анализатора перепол30 нений, первый выход блока сравнения подключен к стробирующему входу дешифратора каналов, второй выход подключен к информационному входу анализатора, переполнений, первый вход син35 хронизации которого соединен с выходом переноса датчика номера каналов, второй вход синхронизации анализатора переполнений соединен с йторым выходом формирователя, опорной частоты,

40 третий выход которого подключен к ; тактовому входу датчика номера канала и входу записи блока памяти.

Корректоров. Бутяга Подписное

| название | год | авторы | номер документа |

|---|---|---|---|

| Генератор последовательности импульсов | 1984 |

|

SU1309275A1 |

| Делитель частоты следования импульсов | 1983 |

|

SU1177907A1 |

| Логический анализатор | 1984 |

|

SU1259267A1 |

| Генератор серии задержанных импульсов | 1985 |

|

SU1372598A1 |

| Частотомер-периодомер | 1985 |

|

SU1337800A1 |

| Формирователь сетки частот | 1988 |

|

SU1656674A1 |

| Логический анализатор | 1986 |

|

SU1432527A1 |

| Интегрирующий частотомер | 1985 |

|

SU1308921A1 |

| Устройство автоматизированной подготовки программ для станков с ЧПУ | 1986 |

|

SU1354160A1 |

| Устройство для контроля функционирования логических блоков | 1987 |

|

SU1432528A2 |

Изобретение может быть исполь- ювано в аппаратуре обработки цифровой информации, в электронных хро- низаторах и измерителях времени. Целью изобретения является расширение функциональных возможностей и повьшение надежности формирователя. Для достижения цели в него введены блок 5 памяти, анализатор 4 переполнений, а датчик 2 номера канала выполнен в виде счетчика адреса. Формирователь также содержит формирователь 6 опорной частоты, да.тчик 2 номера канала, счетчик 3 тактов, блок 8 сравнения, дешифратор 9 адреса, датчик 1 кода. Данный формирователь сетки частот позволяет формировать последовательности импульсов с частотой следования импульсов, понижающейся с увеличением номера выхода с относительным коэффициентом кратности. В описании приведена также формула частоты следования импульсов на выходе, соответствующей адресу Датчика 1. 1 ил. (Л с 1C 00 ю сд

| Многоканальный генератор импульсов | 1978 |

|

SU765991A1 |

| Переносная печь для варки пищи и отопления в окопах, походных помещениях и т.п. | 1921 |

|

SU3A1 |

Авторы

Даты

1987-01-30—Публикация

1985-04-05—Подача