(54) УСТЮЙСТВО ДЛЯ СОПРЯЖЕНИЯ АНАЛОГОВОЙ И ЦИФЮВОЙ ВЫЧИСЛИТЕЛЬНЫХ МАШИН

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1982 |

|

SU1053119A1 |

| Устройство для моделирования синусно-косинусного трансформаторного датчика угла | 1990 |

|

SU1778766A1 |

| Цифровой процессор спектрометрических импульсов | 1989 |

|

SU1610445A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для сопряжения магнитофона с ЦВМ | 1987 |

|

SU1427374A1 |

| Электронный измеритель мощности и энергии | 1988 |

|

SU1638653A1 |

| Цифровой фильтр | 1988 |

|

SU1569957A1 |

| Устройство для вычисления массы нефти и нефтепродуктов в резервуарах | 1983 |

|

SU1117653A1 |

| Многоканальный фотометр | 1987 |

|

SU1492224A1 |

Изобретение относится к области вычисйнгельнои техники и может быть использовано преимущественно в аналого-цифровых кокшяек сах (АЦК) и Гибридных выш{слительш 1х системах. Из вестно устройство, содержащее аналогсюьга процессор, устройство преобразования и сопряжения, в которое входят аналого-цифрсяые (АЦП), щсфроаналоговые преобразовате}{и }АП и коммутаторы 1. Недостатком его является низкая точность получаемых результатов моделирования, обусЛЕЯленная постояиством масштабных коэффициентов. При решении задач масштабирование аналого вых и цифровых переменных осуществляют таким образом, чтобы они из(«юнялис1 в максимально допустимых диапазонах, так как толь-: ко в зтом случае достгается наибольшая точность моделирования. С другой стороны, задание максим|ально допустимого диапазона машинных переменных в ряде случаев Приводит к переполнению разрядной сетки цифровой вы числительной машины (ЦВМ) npi вычислении мгновенных значений промежуточных переменных. В известном устройстве зта комплексная проблема решается выбором соответствующих значеш1й масштабнь1х множителей и заданием |{еизмештх значений коэффициентов передачн в ояера1ШО1шых блоках. Это заведомо приводал к понижению точности моделирования. Действительно, чем меньше значение анапогсяой Авшинной переменной, т1гм ниже точность вычислений в ЦВМ, так как ЦВМ будет работать с кодами чисел, значащие цифры которых рас11оложень1 лишь в младших разрядах разрядной сетки. В аою окредь, уменьшение пналазоиа Нзмевення цифровой мшлинной перемерной при |%изменности масштабных множителей приводит к уменьшена то шости моделирования. Изложенная трудность Может быть преодолена возможностью автоматического изменения масштабных множителей в ходе вычислительного процесса. Наиболее близким по технической сущносга k изобретению является (жстема, содержащая аналог(жую вычислительную машину (АВМ),

ВМ, устройство преобразования и сопряжения масштабный блок 2}.

Она также обладает невысокой точностью оделирования из-за постоянства масштабных ножителей.3

Целью изобретения является расширение фунциональных возможностей за счет автоматичесого изменения масштабных множителей в хое вычислений/

Поставленная цель достигается тем, что в Ю стройство, содержащее АЦП, вход которого одключен к выходу АВМ, первый выход соединен с информационным входом ЦВМ, информационный выход которой через последовательно соединенные ЦАП, коммутаторы и блок ре- 15 зисторов подключен к входу АВМ, управляющие вхоДьг коммутаторов подключены соответственно к выходам регистра, введень вычитающий сЧетчнк, генератор импульсов, схема сравнения, два элемента И, регистр сдвига, группа 20 злементов НЕ, два триггера, злемент задержки, одновибратор и блок анализа, включающий регистр сдвига, элементы И, НЕ, счетчик и одновибратор, причем первьгй выход генератора имс льссш соединен с первыми входами элемен- 25 тов И, выход первого элемента И соединен с первым входом ВЬ1ЧИтающего счггшка, второй вход которого соеданен с выходом ЦВМ, выхйд второго эяемента И Подключен к первому входу регистра сдвига, выход вычитающего 30 счетчика соедаНен с входом схемы сравнения, выход которой соединен с вторыми-входами первого и второто элементов И, с входами первого и второго триггеров и с управляющим входом ЦВМ, вьрсод первого т|Н1ггера соединен 35 с входом одаовибратора, первый выход которого через элемент дадёржки соединен с вторым входом регистра сдвига, выхода которого и в1о{юй выход одаовибратора через группу элементов НЕ подключены к входам регистра, 40 выход второго триггера соединен, с третьим входом регистра сдвига, первый Вход регастра сдвига к Вход одновибратора блока анашза соединены соответствешю с первым и вторым выходами АЦП, выход penictpa сдвига через 45 зйёмекг НЕ подключен к. первому входу зяешта И, второй и третий которого соещнемы срответственно с выходом одновибратора н с вторым выходом генераторт импудаCQB, выход злемента И соедаНеН с вторымso

входом perHCtp сдвига и с первым входом счётчика, аыход которого пощопочен к входу ilB:M, вЮ1)ой вход и третий вход регистра сдаига соединены с вЬ1ходом схемы сравшния.55

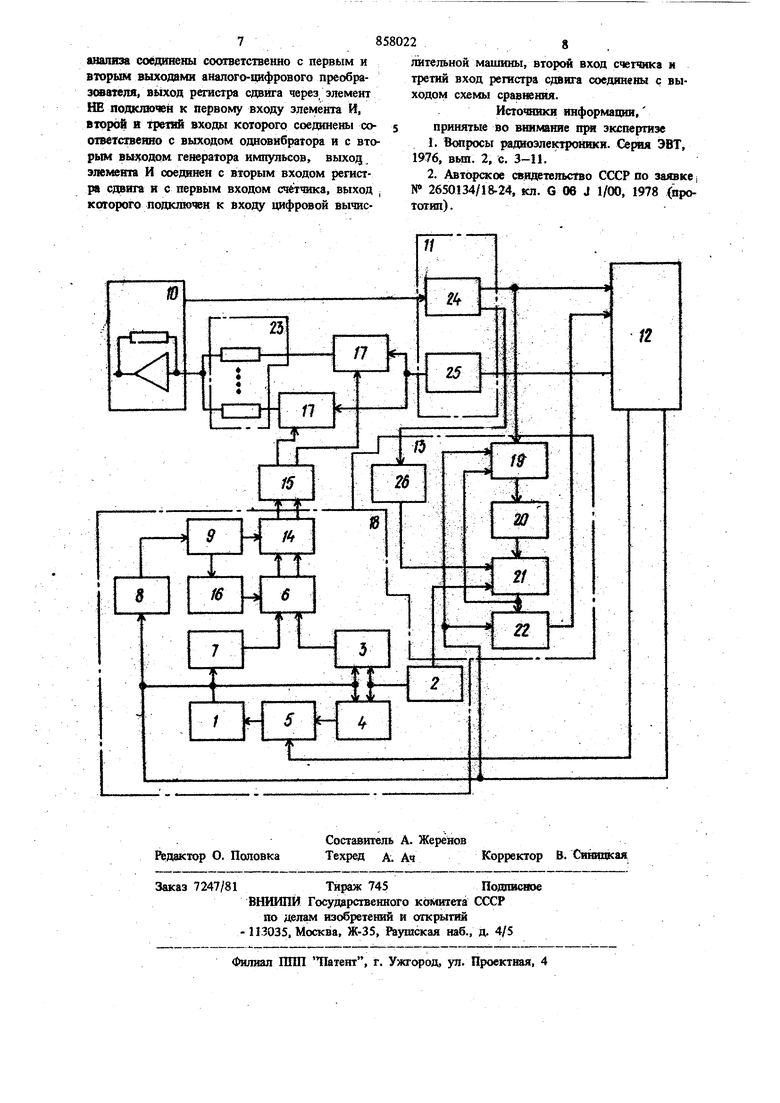

Иа чертея« ирейставяена схема устройства. Устройство соде|гасят схему 1 сравнения, генератор 2 импульсов, элелюнты И 3 н 4, вычитающий счетчик 5, регистр 6сдаига, триггеры 7 н 8, одновибратор 9, АВМ 10, устройство 11 сопряжения, ЦВМ 12, блок 13 анализа, группу эдаментов НЕ 14, регистр 15, злемекг 16 задержки, коммутаторы 17, блок 18 логики, регистр 19 сдвига, злемент НЕ 20, элемент И 21, «четчик 22, блок 23 резисторов, АЩ1 24, ЦАЙ 25, одновибратор 26.

В Исходном состоянии сигнал с выхода схеivQ i 1 сравнения равен нулю, поэтому импульсы с генератора 2 импульсов через элементы И 3 и 4 не поступают нд вход вычитающего счетчика 5 и регистра 6 сдвига. В регистре 6 сдвига в средаем разряде записана едкншга. Т{ш-гер 7 и триггер 8 шисодятся в еданнчном состояшга. Сигналом с выхода чиггера 7 сдвигающий регистр 6 подготовлен для сдвига единицы вправо. Сигнал на выходе одновибратора 9 равен нулю. Сигнал готовности с выхода схемы 1 равен нулю, что говорит о готовности к работе 18 логики. В блоке 13 анализа сигнал на выхода одновибратора 26 равен нулю. Импульсы с генератора 2 не поступают, наВХОД счетчика 22.

Ашлоговые сигналы с АВМ 0 поступают на АЦП 24, а с него 1щфровой код подается в ЦВМ 12 и блок 13 анализа. Выходной код АЦП записывается в perHcip 19 сдвига. Если В первом разряде поеяе знакового в сдвигающем регистре 19 записгн нуль, то на выходе элемента 20 %Дет единичный епатлял. По сигналу Конец иреобразования АЦП запускается одновибратор 26 и импуш сы с генератора 2 начинают пос тхать на регистр 19 и счетчик 22 до тех пор, йока в Первом разряде после знакового не будет единшщ. В этом на Выходе элемента ВД 20 б)одет нулевой сигнал и иМпульсы с генератора 2 не будут поступать иа счетчик 22.ирегисф 19. Сдвиг кода В ре гистре 19 происхедат влево. Количество нмпульсов в счегтаке 22 будет равно количеству сдангов. Код, за1шсайЕ1ш ш в i irafke, является вьь ходаой величиВ(й &1ока ;13 анализа. Время работы одаов ратора вы ре1ся , чтобы можно Шшоосуцдествшъ Количество сдвигст, равное разрядаости АШ-Шс11пи с ЦВМ 12 происходит ottpQC А1Щ 24-е однОВ{к;мешю блока 13 анзл11за, с выхош К(я6|юго сштывается код, раяншй количеству Нулей до яёрвой значащей is старишх ра:;рящахкош1} считанного с АЦП Этот код зш оШшв1ся в фикснроваНной ячейке памяти ЦбМ 12. Кроме зтсяго, в ЦВМ 12 п нсходит caiEfflGT c KtaiBtOTQ с МЩ кода влево до тех пор, пока ве{1вШ1 звафоцая дафра Не нрш(ится в crapfueM , т«. происходит сдвиг Кода влево на кош ество раз1рядов, равное коду, сштанному с жа 13 анализа. Бслв при обработ е ннфорт шцяш е АШ1 возникает переполнение разрядной сетки ЦВМ то по сигаалу переполнения результат вычисления сдвигается вправо на один разряд, а количество сдвигов запоминается в другой фиксированной ячейке. памяти. После отработки алго ритма ЦВМ 12 выдает сигнал в виде цифрового кода на ЦАП 25. Затем из фиксированной ячейки памяти ЦВМ 12 выдает код, равный количеству запомненны сдвигов впртво, на вычитаюищй счегшк 5 блока Г8 логики. Сигнал на выходе схемы 1 срав нения становится равным единице и подается на входы элементов ИЗ и 4, а также на счетчик 22 и регистр 19, тем самым сбрасьшая их в нуль. Импульсы с генератора 2 через эле мен ты И 3 и 4. начинают поступать на вычитающий счетчик 5 и регистр 6. Единица в регистре 6 сдвигается впршо на столько разрядов, сколько единиц записано в вычитающий счетчик 5. По обнулению счетчика 5 сигнал на выходе схемы 1 сравнения становится равным нулю. (Ьшульсы с генератбра 2 прекращают поступат в счетчик 5 и регистр 6. .Триггеры 7 и 8 устанавливаются в нулевое состояние, при этом сигнал с выхода триггера 7 Подготавливает регистр 6 для сдвига влево. Кроме того, нулевой сигнал на выходе схемы 1 сравнения является сигналом готовности. По которому ЦВМ 12 выдает в счетчик 5 код, равный количеству сдвигов влево. Сигнал на выходе схемы I сравнения снова становится равным единице и постз пает на элементы И 3 и 4. Импульсы с генератора 2 поступают в счетздк 5 и регистр 6. Единица в регистре 6 начинает сдвигаться влево. :При обнулении счетчика 5 сигнал на выходе схемы 1 сравнения вновь становится рав( нулю. Импульсы с генератора 2 прекращают поступать в счетчрк 5 и регистр 6. ТриггерЬ 7 и.8 устанавливаются в единичное состояние. Сигналом с выхода триггера 7 регистр 6 подготавливается для сдвига единицы вправо, а передний фронт иМпульса триггера 8 запускает одновибратор 9. CiBrHan с одновибратора 9 открь1вает элеиленты НЕ 14 и происходит перезапись единиць с регастра 6 в регистр 15. Кроме того, сигнал с Шогибратора 9, пройди элемент 16 задер ски, устанавливает регистр 6 в исходное состояние, . единшог в среднем разряде. Сетнал с ;регистра 15 поступает на коммутаторы 17.: В 3 ависимости от того, в каком разряде нсажется единща в регистре 15, будет открыт соответствующий коммутатор 17. Сигнал с выхода ПШ через открытый коммутатор 17 HoctjiiaeT на вход АВМ 10; Резисторы в блоке 23 пойобраны.таким образом, что коэффициент будет изменяться при открытии соответствую ющего коммутатора 17 пропорционально разности количества сдвигов в ЦВМ 12 вправо и влево, т.е. будет осуществляться автоматическое масштабирование. Устройство работает с кодами, находящимися во всех разрядах разрядной сетки ЦВМ. Даже при малых значениях маппшных перемеИных в АВМ им будут соответствовать , находящиеся в старщих разрядах разрядной сетки ЦВМ. При этом, если в ЦВМ количество сдвигов влево больше, чем количество сдвигов вправо, то коэффициент передачи операционного блока, входящего в АВМ, уменьщается, и наоборот. Формула изобретения Устройство Для сопряжения аналоговой и цифровой выедслительных машин, содержащее аналого-цифровой преобразователь, вход которого пojtцcлючeн к выходу аналоговой вычислительной машины, первый выход соединен с информационным входом цифровой вычислительной машины, информационный выход которой через последовательно соединенные цифроаналоговый преобразователь, коммутаторы и блок резисторов подключен к входу аналоговой вычислительной -машины, управляющие входы комМутаторов подключеШ) соответственно к выходам регистра, о тличающееся тем, ;что, с целью расширения функциональных возможностей за счет автомагического изменения масштабных множителей, в него введены вы читающий счетчик, генератор импульсов, схема сравнения, два. элемента И, регистр сдвига, группа элементов НЕ, два триггера, элемент задержки, одновибратор, блок анализа, включающий регистр сдвига, элементы И, НЕ, счетчик и одновибратор, причем первый выход генератора импульсов соёдашен с первыми входами элементов И, выход первого зпемента И соединен с Первь1м входом вычитающего счетчика, второй вход которого соеданен с выходом щфровой вычислительной мацшны, выход второго элемента И подключен к первому входу регистра сдвига выход вычитающего счетчика соединен с входом cxeNOd сравнения, выход которой соединен с вторыми входами первого и второго элементов И, с входами первого и второго триггеров И с управляющим входом цифровой вычислительной машины, выход первого триггера сое данен с входом ошовибратора, первый выход которого черег элемент задержки соеди1«н с Вторым входом регистра сдвига, выходы которого и второй выход одаювибратора через , элементов НЕ подключены к входам регистра, выход второго триггера соединен с третьим входом регистра сдвига, первый вход periabipa сдаига и вход одновибратора блока анализа соёдитны соответственно с первым и вторым выходакш аналого-1щфрового преобраЗОватедя, выход регистра сдвига через элемент НЕ подключен к первому входу элемента И, второй и третяй входы которого соединены соотаетственно с выходом одновибратора и с вто рым выходом генератора импульсов, выхо элемента И соединен с вторым входом регистре сдвига и с первым входом счбтчика, выход которого подключен к входу цифровой вычистательной машины, второй вход счетчика и третий вход регистра сдвига соединены с выходом схемы сравнения. Источники информапии, принятые во внимание ni« экспертизе 1.Вотросы радаоэдектроники. Серия ЭВТ, 1976, вып. 2, с, 3-11, 2.Авторосое (жидетеяьство СССР по заявке , N 2650134/18-24, Кл. G 06 J 1/00, 1978 (прототип).

Авторы

Даты

1981-08-23—Публикация

1979-11-05—Подача