ройства, выход первого триггера соединен с -нулевым входом третьего триггера, вторыми, входами второго и третего элементов ИЛИ, первым входом четвертого элемента ИЛИ и является установочным, выходом устройства для подключения аналоговой вычислительной машины, выход третьего триггера соединен с вторым входом первого элемента И, выход четвертого элемента ИЛИ соединен с установочным входом второго счетчика, а второй вход с выходом второй схемы сравнения, первый и второй входы которой соединены соответственно с выходами второго счетчика и второго регистра, второй выход второго счетчика через третий узел подключения к шине соединен с адресной шиной блока памяти и с адресным входом цифро-аналогового преобразователя, информационный вход которого через четвертый узел подключения к шине соединен с выходной шиной данных блока памяти, а 1зыход является информационным выходом для подключения аналоговой вычислительной машины, выход счетчика адреса через пятый узел подключения к шине, управляющим входом соединенный с выходом первого элемента ИЛИ., соединен с ашресной шиной блока памяти, выход третьего элемента ИЛИ соединен с установочным входом счетчика адреса и с первым входом пятого элемента ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а выход подключен к шине прерывания цифровой вычислительной машины, выход первого регистра соединен с вторым входом первой схемы сравнения, выход третьего элемента И соединен с управляющими входами первого и второго узлов подключения к шине, входная и выходная шины данных блока памяти соответственно через шестой-и седьмой узлы подключения к шине управляющими входами, соединенные соответственно с шинами Запись и Чтение блока памяти, соединен с входной и выходной шинами данных устройства.

| название | год | авторы | номер документа |

|---|---|---|---|

| Аналого-цифровая вычислительная система и аналоговая вычислительная машина (ее варианты) | 1983 |

|

SU1259300A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1221666A1 |

| Устройство для обмена информацией между аналоговой и цифровой вычислительными машинами | 1990 |

|

SU1755372A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1983 |

|

SU1257673A1 |

| Устройство для связи аналоговой и цифровых вычислительных машин | 1983 |

|

SU1140135A1 |

| Устройство для обмена информацией между цифровой и аналоговой вычислительными машинами | 1986 |

|

SU1348844A1 |

| Устройство для сопряжения ЦВМ с магнитофоном | 1985 |

|

SU1317445A1 |

| Устройство для сопряжения цифровой и аналоговой вычислительных машин | 1983 |

|

SU1128273A1 |

| Устройство для межмашинного обмена | 1985 |

|

SU1298756A1 |

| Устройство для сопряжения абонентов с ЦВМ | 1985 |

|

SU1278863A1 |

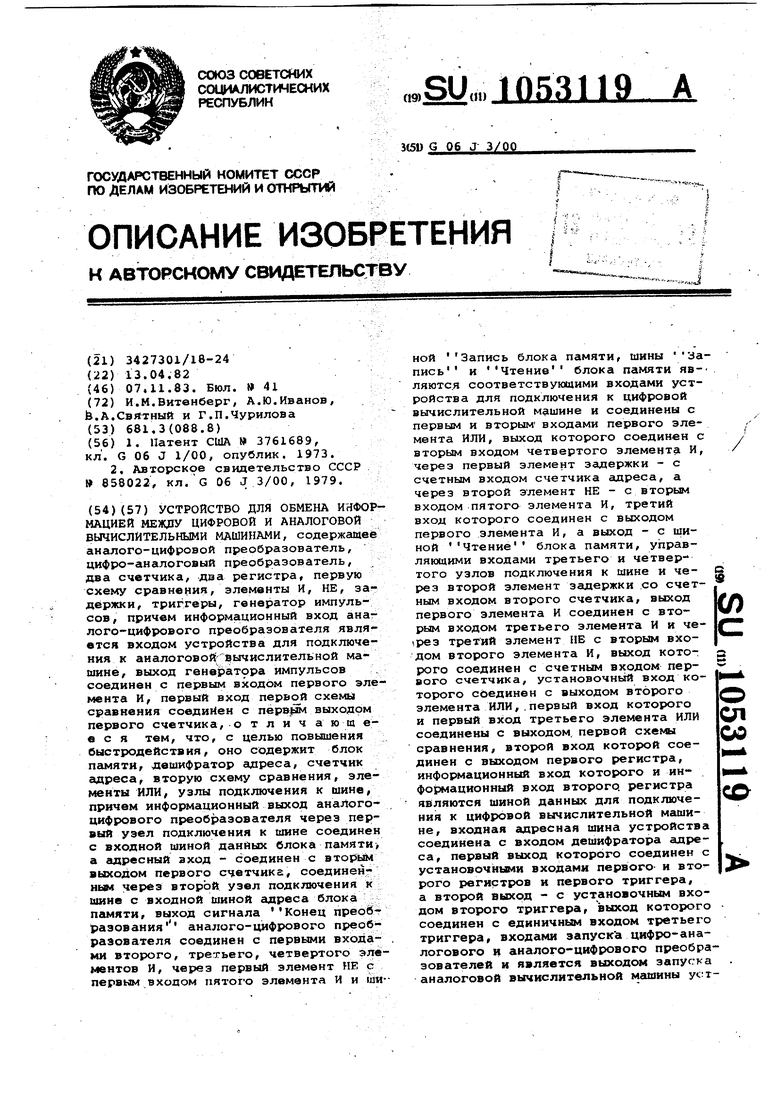

УСТРОЙСТВО ДЛЯ ОБМЕНА ИНФОРМАЦИЕЙ МЕЖДУ ЦИФРОВОЙ И АНАЛОГОВОЙ ВЫЧИСЛИТЕЛЬНЫМИ МАШИНАМИ, содержащее аналого-цифровой преобразователь, цифро-аналоговый преобразователь, два счетчика, -два регистра, первую схему сравнения, элементы И, НЕ, задержки, триггеры, генератор импульсов , причем информационный вход анатлого-цифрового преобразователя является входом устройства для подключения к аналоговой;Вычислительной машине, выход генерат9ра импульсов соединен с первым входом первого элемента И, первый вход первой схемы сравнения соедийен с nepBjwi выходрм первого счетчика,-о т л и ч а ющ ее с я тем, что, с целью повьлшения быстродействия, оно содержит блок ПЕ1МЯТИ, дешифратор адреса, счетчик адреса, вторую схему сравнения, элементы ИЛИ, узлы подключения к шине, причем информационный выход аналогоцифрового преобразователя через первый узел подключения к шине соединен с входной шиной данйых блока памяти, а адресный вход - соединен с вторым выходом первого счетчика, соединеняьал через второй узел подключения к шине с входной шиной адреса блока пгиляти, выход сигнала Конец преобразования аналого-цифрового преобразователя соединен с первыми входа- . ми второго, третьего, четвертого элементов И, через первый элемент НЕ с первым входом пятого элемента И и ши-Запись блока памяти, шины Заной пись Чтение блока памяти яви ляются соответствующими входами устройства для подключения к цифровой вычислительной машине и соединены с первым и вторым входами первого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемента И, через первый элемент задержки - с счетным входом счетчика адреса, а через второй элемент НЕ - с вторым входом пятого элемента И, третий вход которого соединен с выходом первого элемента И, а выход - с шиной Чтение блока памяти, управляющими входами третьего и четвер- того узлов подключения к шине и через второй элемент задержки со счетным входом второго счетчика, выход первого элемента И соединен с вторым входом третьего элемента И и че(рез третий элемент НЕ с вторым входом второго элемента И, выход которого соединен с счетным входом первого счетчика, установочньД вход которого соединен с выходом втбрюго элемента ИЛИ,.первый вход которого СП и первый вход третьего элемента ИЛИ оо соединены с выходом, первой схемы сравнения, второй вход которой соединен с выходом первого регистра, информационный вход которого и информационный вход второго, регистра CD ябляются шиной данных для подключения к цифровой вычислительной машине, входная адресная шина устройства соединена с входом дешифратора адреса, первый выход которого соединен с установочными входами первого- и второго регистров и первого триггера, а второй выход - с установочным входом второго триггера, выход которого соединен с единичным входом третьего триггера, входами эапуска цифро-аналогового и аналого-цифрового преобразователей и является выходом запуска аналоговой вычислительной машины ус; т

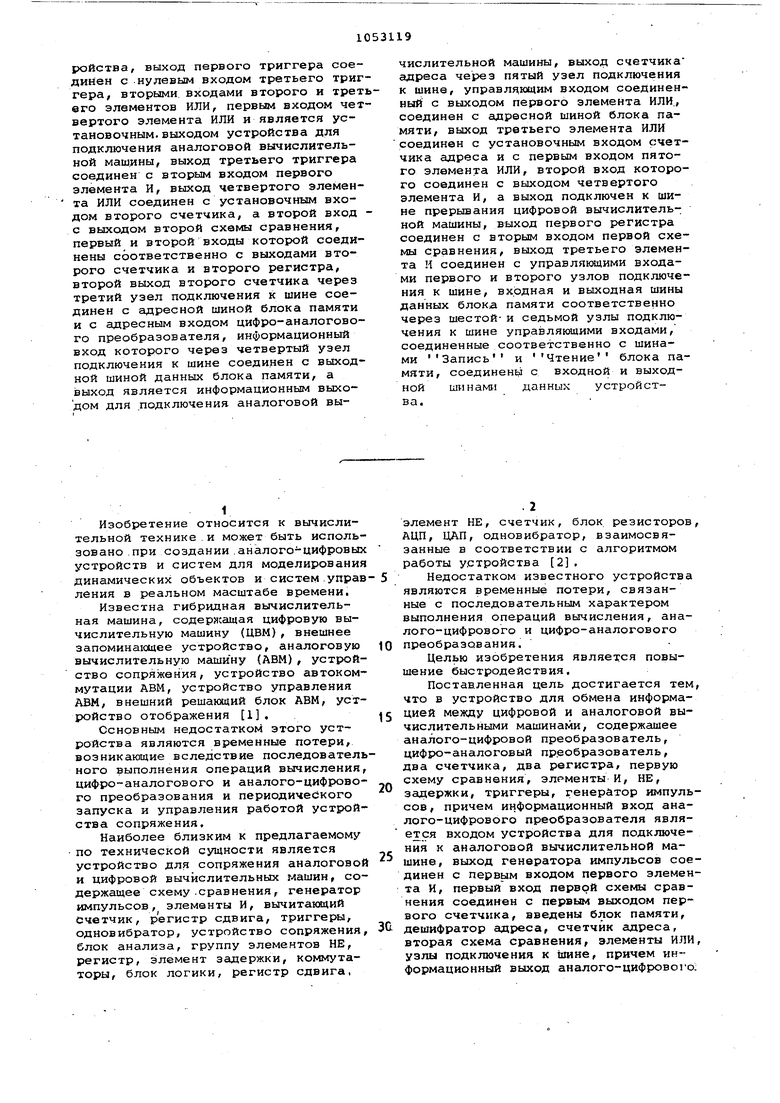

Изобретение относится к вычислительной технике . и может быть исполь зовано .при создании.аналого-цифровых устройств и систем для моделировани динамических объектов и систем управ ления в реальном масштабе времени. Известна гибридная вычислительная машина, содержащая цифровую вычислительную машину (ЦВМ), внешнее запоминающее устройство, аналоговую вычислительную машину (АВМ) , устройство сопряжения, устройство автокоммутации АВМ, устройство управления АВМ, внешний решающий блок АВМ, устройство отображения 1, Основным недостатком этого уст ройства являются временные потери, возникающие вследствие последователь ного выполнения операций вычисления цифро-аналогового и аналого-цифрового преобразования и периодического запуска и управления работой устройства сопряжения. Наиболее близким к предлагаемому по технической сущности является устройство для сопряжения аналоговой и цифровой вычислительных машин, содержащее схему .сравнения, генератор импульсов, элементы И, вычитаквдий Счетчик, регистр сдвига, триггеры, одновибратор, устройство сопряжения блок анализа, группу элементов НЕ, регистр, элемент задержки, коммутаторы, блок логики, регистр сдвига, элемент НЕ, счетчик, блок резисторов, АЦП, ЦАП, одновибратор, взаимосвязанные в соответствии с алгоритмом работы устройства 2. Недостатком известного устройства являются временные потери, связанные с последовательным характером выполнения операций вычисления, аналого-цифрового и цифро-аналогового преобразования. Целью изобретения является повышение быстродействия. Поставленная цель достигается тем, что в устройство для обмена информацией между цифровой и аналоговой вычислительными машинами, содержсшее аналого-цифровой преобразователь, цифро-аналоговый пр.еобразователь, два счетчика, два регистра, первую схему сравнения, элементы И, НЕ, задержки, триггеры, генерйтор импульсов , причем информационный вход аналого-цифрового преобразователя является входом устройства для подключения к аналоговой вычислительной машине, выход генератора импульсов соединен с первым входом первого элемента И, первый вход первой схемы сравнения соединен с первым выходом первого счетчика, введены блок памяти, дешифратор адреса, счетчик адреса, вторая схема сравнения, элементы ИЛИ, узлы подк.пючения к шине, причем информационный выход аналого-цифрового:

преобразователя через первый узел подключения к шине соединен с вход вой шиной данных блока памяти, а ад ресныйвкод - с вторым выходом первого счетчика, соединенным через второй узел подключения к шине с входной шиной адреса блока памяти, выход сигнала Конец преобразования аналого-цифрового преобразователя соединен с первыми входами второго, третьего, четвертого элементов И, через.первый элемент НЕ с первым входом пятого элемента И, и шиной Запись блока памяти, шины Запись и Чтение блока памяти являются : соответствующими входами устройства для подключения к цифровой вычислительной машине и соединены снервым и вторым входами первого элемента ИЛИ, выход которого соединен с вторым входом четвертого элемеата И, через первый элемент задержки - со счетным входом счетчика адреса, а через второй элемент НЕ - с вторым входом пятого элемента И, третий вход которого соединен с выходом перBorq элемента И, а выход - с шиной Чтение блока памяти, управляющими входами третьего и четвертого узлов подключения к шине и через второй элемент задержки со счетным входом второго счетчика, выход пер вого элемента И соединен с вторым входом третьего элемента И и через третий элемент НЕ с вторым входом второго элемента И, выход которого соединен со счетным входом первого счетчика, установочный вход которого соедИнен с выходом второго элемента ИЛИ, первый вход которого ,и первый вход третьего элемента ИЛИ соединены с выходом первой схемы сравнения, второй вход которой соединен с выходом первого регистра, , информационный которого и информационный вход второго регистра явлЯ(отся шиной данных для подключения к цифрювой вычислительной машине входная адресная шина устройства соединена с входом дешифратора адреса, первый выход которого соединен с установочными входами первого и второго регистров и первого триггера, а второй выход - с установочным входом второго триггера, выход которого соединен с единичным входом третьего триггера, входами запуска цифро-аналогового и аналого-цифрового преобразователей и является выходом запуска аналоговой вычислительной машины устройства, выход первого триггера соединен с нулевым входом третьего триггера, вторыми входами вторюгоИ третьего элементов ИЛИ, первым входом четвертого элемента ИЛИ и является установочным выходом устройства для подключения аналоговой вычислительной машины, выход

третьего триггера соединен с вторым входом первого элемента И, выход чет- , вертого элемента ИЛИ соединен с установочньвл входом второго счетчика, а второй вход г с выходом второй схемы сравнения, первый и второй входы котор1 й соединены соответственно с выходами второго счетчика и второго регистра, второй выход второго счетчика через третий узел подключения

0 к шине соединен с адресной шиной блока памяти и с адресным входом цифроаналогового преобразователя, информационньй вход которого через четвертый узел подключения к шине соединен с выходной шиной данный блока памяти,

5 а выход.является информационным выходом .для подключения аналоговой вычислительной машины, выход счетчика. адреса через1пятый узел подключен к шине, упрс ля1свдим входом соединенный

0 с выходом первого элемента ИЛИ, соединен с адреснойШИНОЙ блока памяти, выход третьего элемента ИЛИ соединен с установочным входом счетчика адреса и с первым входом пятого элемента

5 ИЛИ, второй вход которого соединен с выходом четвертого элемента И, а .выход подключен к шине прерывания цифровой вычислительной машины,выход первого регистра соединен с вторым

0 входом первой схемы сравнения, выход третьего элемента И соединен с управляющими входами первого и второго узлов подключения к шине, входная и выходная шины данных блока памяти со5ответственно через шестой и седьмой узлы подключения к шине управляющими входами, соединенные соответственЧтение

Запись

но с шинами

блока памяти, соединены с входной и выходной шинами данных устройства.

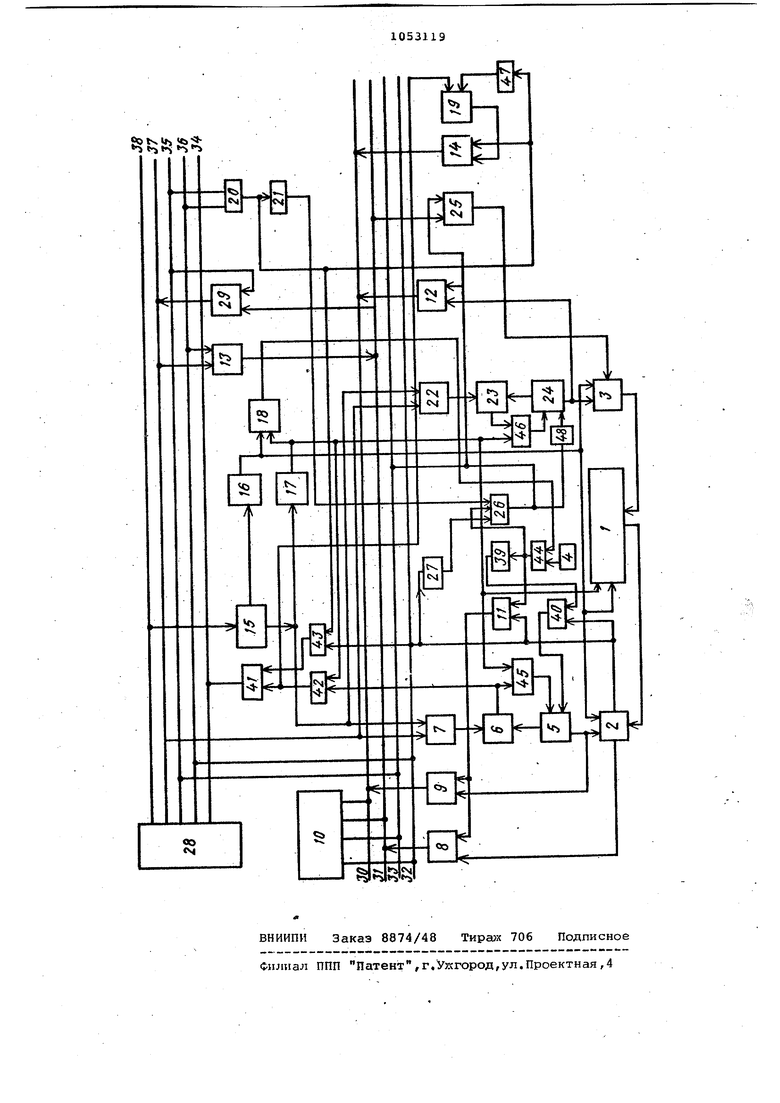

На чертеже представлена блок-схема устройства.

Устройство содержит АВМ 1, аналого-цифровой преобразователь (АЦП) 2, цифро-аналоговый преобразователь

(ЦДП) 3 генератор 4 тактовых импульсов , первый счетчик 5, первую схему 6 сравнения, первый регистр 7, первый Узел 8 подключения к шине, второй узел 9 подключения к шине, блок 10 памяти, третий элемент И 11, третий узел 12 подключения к шине, седьмой узел 13 подключения к шине, четвертый узел 14 подключения к шине, дешифратор 15 адреса, первый триггер 16, второй триггер 17, третий триггер 18, счетчик 19 адреса, первый элемент ИЛИ 20, второй элемент НЕ 21, второй регистр 22, вторую схему 23 сравнения, второй счетчик 24, шестой узел 25 подключения к шине, второй элемент И 26, первый элемент НЕ 27, цифровую вьачислительную машину 28

(ЦВМ), пятый узел 29 подключения к. шине, адресную шину 30, шину 31 данных, входы Запись 32 и Чтение 33 блока памяти, выходы Пре Чтение рьшание пись 36 ЦВМ шины 37 данных и адр са 38 ЦВМ, третий элемент НЕ 39, тр тий элемент И 40, четвертый элемент ИЛИ 41, третий элемент ИЛИ 42, четверфый элемент И 43, пятый элемент И 44, второй элемент ИЛИ 45, пятый элемент ИЛИ 46, первый элемент 47 задержки, второй элемент 48 задержк Устройство работает следующим об разом. На этапе подготовки исходная зада ча разделяется одним из известных способбв на две части, одна из которых предназначена для решения на ана логовой (АВМ 1), а другая - на цифро ,вой части устройства (ЦВМ 28). Связь между переменными в решаемой задаче осуществляется по каналам 3 и АЦП 2, Пусть при решении задачи в АВИ 1 передаются переменные Y,, Yj,.. Yju, из ЦВМ 28, а из АВМ 1 в ЦВМ 28 переменные Х, Х, ., Х. В ЦВМ 28 заводится программа цифровой части задачи, в которой определено количество кансшов цифро-аналогового преобразования М, а также программа обработки прерьшаний, под управлением которой производится обмен информацией межцу памятью 10 и ЦВМ 28. В соответствии с этим первые N ячеек ЦВМ 28 отводятся для хранения резуль татов преобразования с первого по М-й канал АЦП 2, а последующие М+1N+M ячеек ЦВМ 28 отводятся для хране ния данных, предназначенныхдля выдачи с первого по М канал ЦАП 3. Программа аналоговой части задачи вводится в АВМ 1. В начале программы решения задачи по команде ЦВМ 28 в регистры 7 и 22 записьшаются конеч ные адреса обмена, равные значению начального адреса, увеличенному на величину М для каналов ЦАП и .на величину )J для каналов АЦП.По команде цифровой пасти задачи установить исходное положение дешифратором 15 вырабатывается сигнал Исходное положение, устанавливающий триггер 17 в единичное состояние. Сигнал с выхода триггера 17 поступая на второй вход элемента ИЛИ 45, вызывает поступление с его выхода единичного сигнала на вход счетчика 5, устанавливая его в -начальное состояние (начальный адрес аналого-цифрового преобразования), и на второй вход АВМ 1, устанавливая его в режим Исходное положение. Единичный сигнал с выхода триггера 17, поступая на первый вход элемента ИЛИ ,46, вызывает поступление с его выхода единичного сигнала на вход счетчика 24, устанавливая его в начальное состояние (начальный ад.Dec цифро-аналогового преобразова ния) . Единичный сигнал с выхода триггера 17, поступая на второй вхЪд элемента ИЛИ 42, вызывает подачу единичного сигнала с вьгхода- элемента ИЛИ 42 на вход счетчика 19, устанавливая его в начальное состояние (начальный адрес обмена блока 10 с ЦВМ 28). Сигнал с выхода триггера 17, поступив на -второй вход элемента ИЛИ 42, вызывает поступление единичного сигнала с выхода элемента ИЛИ 41 на вход прерывания ЦВМ 28. При этом в ЦВМ 28 управление передается программе обработки прерываний. При обмене информацией на первом эха.пе производ-ится чтение переменных Х|, Xj-,..., Х( из -блока 10 в ЦВМ 28, а на втором этапе - запись переменных V;, , V,,.,, ЦВМ 28 в блок 10. На первом этапе при выполнении команды Чтение в ЦВМ 28 программой обработки прерываний сигнал с выхода чтение 35 ЦВМ 28 вызывает поступление единичного сигнала с выхода элемента ИЛИ 20 на вход элемента 47 задержки и второй вход узла 14 и ;разрешает поступление начального адpeca счетчика 19 на адресную шину блока 10. По сигналу Чтение ЦВМ 28j поступающему на вход Чтение блока 10, информация из ячейки, соответствующей первому каналу преобразователя 2, поступает на шину 31 данных блока 10 и через узел 29 на шину 37 ЦВМ 28. Информация с шины дaнныk заносится в ЦВМ 28 по адресу, соответствующему переменной Х|. При выполнении следующей команды Чтение единичный сигнал с выхода элемента 47 задержки увеличивает содержимое счетчика 19 на единицу, что приводит к чтению инфор- мации из ячейки, соответствующей второму каналу преобразователя 2, и записи ее.в ЦВМ 28 по адресу, соответствующему переменной Хл. Чтение остальных (N-2) переменных блока 10 в ЦВМ 28 выполняется аналогично. После того/ как все N переменных введены в ЦВМ 28, программа обработки прерываний начинает запись переменных Y, ,,..., f в блок 10. При этом сигнал с выхода Запись . ЦВМ 28 вызывает поступление единичного сигнала с выхода элемента ИЛИ 20.на вход элемента 47 задержки и второй вход узла 14 и разрешает поступление адреса переменной Vf из счетчика 19 на адресную шину 30 блока 10. По сигналу Запись ЦВМ 28, поступающему на вход Запись 32 блока 10, информация из ячейки, соответствующей переменной.ЦВМ 28, поступает иа шину 37 данных ЦВМ 28 и через узел 13 на шину 31 данных блока 10. Информация с шины 31 данных записывается в блок 10 по адресу, соответствующему первому каналу преобра-, эователя 3. При выполнении следующей кол1анды Запись единичный сигнал с выхода элемента 47 задержки уведичивает содержимое счетчика 19 на 9дн ницу, что приводит к записи информации в ячейку, соответствукяцую второму каналу преобразователя 3, из яче.й ки ЦВМ 28, адрес которой соответству ет переменной Vj.. Запись остальнш: (М-2) переменных ЦВМ 28 в бло 10:вы полняется аналогично. После того, как все М переменных введены в блок 10, программа обработки прерываний осуществляет передачу управления в программу решения задачи моделирования. Таким образом, исходные данные рассчитанные исходя из начальных условий, будут выданы в АВМ 1 через преобразователь 3, а величины X,j, Kq,, ,, , Х){, введенные первый раз в ЦВМ 28 при решении задачи, не исполь зуются . По команде Пуск из программы решения задачи ЦВМ 28 сигналом с дешифратора 15 устанавливается в единичное состояние триггер 16, При поступлении единичного сигнала с выхода триггера 16 на третий вход АВМ 1, происходит его установка в режим Пуск и начинается решение задачи в аналоговой части устройства. При поступлении единичного сигнала с выхода триггера 16 на второй вход шреобразователя 2 осуществляется , его запуск на циклическую работу. При этом в преобразователе 2 выполняется опрос и преобразование непрерывных сигналов, поступающих из АВМ 1, начиная с начального адреса (находится в счетчике 5) и по конечный адрес (находится в регистре 7), . Преобразователь 2 преобразует анало говый сигнал АВМ 1 в дискретную фор му и подает его на первый вход узла 8, вырабатывая при зтом сигнал нец преобразования, который поступает на первый вход элемента. И 11 и вход Запись 32 блока 10, Элемент И 11 с приходом разрешающего сигнала с выхода элемента И 4 вырабатывает сигнал, при поступлении которого на вторые входы узлов 8 и 9 разрешается запись информации с выхода узла 8 в блок 10 по адресу, . установленному в узле 9 с второго вы хода счетчика 5.- Элемент И 40 с поступлением на первый вход сигнала Конец преобразования.и разрешаю шего сигнсша с выхода генератора 4 выра6аты;вает сигнал, который поступает на второй вход счетчика 5, вы зывая увеличение его содержимого ва единицу. После установления новохЧЗ текущего адреса в счетчике 5 возможны несколько вариантов функционирования устройства. BcjiH содержимое счетчика 5 не больше содержимого регистра 7/ то схема 6 не вырабатывает управляющих сигналов и преобразователь 2 переходит к преобразованию сигнала со следующего канала АВМ I. Если содержимое счетчика 5 , больше содержимого регистра 7, схема 6 вырабатывает управляющий сигнал, который устанавливает счетчик5 в начальное состояние. Преобразователь 2 переходит к преобразованию сигналов, начиная с начального адреса, что обеспечивает циклическое преобразование непрерывных сигналов преобразователем 2 и запись информации в блок 10. Управляющий сигнал с выхода схеN&1 6 также поступает на первый вход элемента ИЛИ 42, что вызывает поступление единичного сигнала с выхода элемента ИЛИ 41 на вход прерывания ЦВМ 28 и на первый вход счетчика 19/ устанавливая его в исходное состояние (начальный адрес информации блока 10 для обмена с ЦВМ 28). В ЦВМ 28 при поступлении сигнала прерывания управление передается программе обработки прерываний, которая производит обмен информацией между блоком 10 и ЦВМ 28 так же, как и при выполнении команды Исходное положение с ЦВМ 28. Одновременно с этим, при поступлении единичного сигнала с выхода триггера 16 на второй вход преобразователя 3,осуществляется запуск преобразователя 3 на циклическую работу. Преобразователь 3 преобразует дискретную информацию, считываемую из последовательных ячеек блока 10, в непрерывные сигналы и вьщает их в АВМ 1. В случае, если не .производится запись преобра-зованной преобразовай-елем 2 информации в блок 10, а также отсутствует обмен переменными Х, ..f XN Y{ Ла f..YMмежду блоком 10 и .ЦВМ 2.8, на выходах элементов НЕ 27 и 21 устанавливаются единичные сигналы. Разрешающий сигнал с выхода генератора 4.вызывает, поступление .единичного сигнала с выхода элемента И .44 на-.второй вход элемента И. 26. Сигнал с выхода .элемента И 26 вызывает поступ ение единичногосигнала на вход Чтение 33 блока 10, на вход элемента 48 задержки и на второй вход узла 25. По этому сигналу, поступающему на второй вход узл 12, разрешается вьадача узлом 12 адреса переменной, соответствующей первому каналу преобразователя 3 из счетчика 24 на адресную шину 30 блока 10. Информация из ячейки блока 10, соответствукнцей переменной передаваемой по первому каналу преобразователя 3, поступает на шину 31 данных блока 10 и на первый вход узла 25, откуда затем поступает ва третий вход преобразователя 3..При поступлении следующего разрешающего сигнала с генератора 4 единичный сигнал с выхода элемента 48 задержки увеличивает содержимое счетчика 24 на единицу, что приводит к

чтению информации из ячейки, соответствующей второму каналу преобразователя 3. Увеличение содержимого счетчика 24 происходит до тех пор, пока оно не станет больше содержимого регистра 22., В .этомСлучае схема 23 вырабатьшает единичный сигнал, который, поступив на первый вход счетчика 24, устанавливает его в начальное состояние. При появлении очередного сигнала с выхода генератора 4 снова происходит чтение информации из ячейки, соответствующей первому каналу преобразователя 3. Таким образом обеспе ивается циклическая работа преобразователя 3,

В устройстве операции цифро-аналогового преобразования не выполняются в случае, если производится обмен информацией между блоком 10 и ЦВМ 28, В этом случае единичные сигналы с выходов Чтение 35 или Запись ЦВМ 28, поступив соответственно на первый или второй вход элемента ИЛИ 20, вызывают появление сигнала нулевого уровня на выходе элемента И 26 независимо от управляющих сигналов на первом и.втором его входах. Сигнал с выхода элемента И 26, поступив на вторые входы узлов 12 и 25, запрещает чтение информации с блока 10 в преобразователь 3. По этому же сигналу во время обмена информацией между блоком . 10 и ЦВМ 28 содержимое счетчика 24 не увеличивается. После окончания обмена между блоком 10 и ЦВМ. 28 цифро-аналоговое преобразование продолжается. Работа преобразователя 3 приостанавливается также при записи .преобразованной преобразователем 2 информации в блок 10. В этом случае

запрещающий сигнал на выходе элемента И 26 появляется вследствие поступления инвертированного элементом НЕ 27 единичного сигнала Конец

преобразования

с первого выхода

преобразователя 27, Сигнал Конец преобразования, поступив на первый .вход .элемента И 43 в случае наличия единичного сигнала на втором ;его входе (свидетельствующего, что производится обмен информацией между блоком 10 и ЦВМ 28), вызывает поступление единичного сигнала на второй вход элемента ИЛИ 41 и на вход Прерывание ЦВМ 28, По сиг5 налу прерывания ЦВМ 28 начинает

выполнять программу обработки прерываний, которая, определив, что происходит обмен информацией мезвду блоком 10 и ЦВМ 28,организует эгщержку

0 в обмене очередной информацией на время записи информации из. преобразователя 2 в блок 10. Сигнал Конец преобразования не вызывает прерывания работы ЦВМ 28, если.обмен ин5 формацией между блоком 10 и ЦВМ 28 не происходит (с выходов Чтение 35 и Запись 36 ЦВМ 28 поступают сигналы нулевого уровня на второй вход элемента И 43, запрещая прохожQ дение единичного сигнала Конец преобразования на выход элемента И 43),

В устройстве достигается большее g быстродействие за счет параллельной 5 организации вычислений, цифро-аналогового и аналого-цифрового преобразования. Это обеспечивает расширение класса решаемых задач устройством иобеспечивает упрощение систем прог0 раммирования цифровой части.

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Патент США 3761689, кл | |||

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Приспособление для склейки фанер в стыках | 1924 |

|

SU1973A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство для сопряжения аналоговой и цифровой вычислительных машин | 1979 |

|

SU858022A1 |

Авторы

Даты

1983-11-07—Публикация

1982-04-13—Подача