1

Изобретение относится к вычислительной технике и может быть использовано в оптикоэлектронных системах параллельной (картинной) обработки информации для выполнения арифг тическях и логических операций над двумя массивами двоичных позиционных чисел, записанных на двух числовых картинах в виде матриц.

Известны матричные сумматоры для выполнения арифметических и логических операций.

Одно из известных устройств содержит световоды,. плоскопараллельный инвертирующий преобразователь, источники света и дешифратор, выполненный на световодах Щ.

Другое известное устройство содержит входные и дополнительные управляе ивле транспаранты, выполненные в виде матрицы элементов ИЛИ-НЕ, выходной управляющий транспарант, выполненный в виде матрицы элементов ИЛИ, и блок сдвига, входы которого связаны с выходом одного из дополнительных управляе «лх транспарантов, а выходы блока сдвига связаны с входами одного из входных транспарантов 2 J.

Недостатки указанных устройств увеличение времени выполнения арифметических операция над массивами чисел или количества необходимого оборудования. Некоторые из этих устройств не позволяют также эффективно использовать все информационное поле матрицы. Устройства без цепей переноса, расчетнные на выполнение арифметических операций над числами, записанными в специальных непозиционных .или избыточных системах счисления (сок, знако-разрядное представление и др.), требуют перевода сива чисел из обычной позиционной i специальные CHCTeNEJ счисления. Это также ведет к снижению общей производительности системы

Наиболее близок; к предлагаемому

изобретению комбинационный оптикоэлектронный матричный сумматор, построенный на логических матричных элементах НБ и ИЛИ и ИЛИ-НЕ, которые заполнены на оптически управляемых транспарантах в виде матриц элементов НЕ и ИЛИ и ИЛИ-НЕ. Двумерный оптически: сигнал, несущий информацию массива чисел поразрядно в виде подматриц сигналов, подается последовательно на две входные матричные

шины, разряд за разрядом, начиная с младшего. На третью входную матричную шину подается двумерный оптический сигнал подматрицы переноса, вьчрабатываемый в предыдущем такте D. Недостаток этого сумматора - низкая производительность из-за малого быстродействия, а также его сложность.

Цель изобретения - увеличение быстродействия и упрощение сумматора,

Поставленная цель достигается тем что в комбинационный матричный сумматор, содержащий матричные блоки элементов НЕ и ИЛИ и ИЛИ-НЕ,-первые и вторые входы первого матричного блока элементов ИЛИ-НЕ связаны с соответствующим входами сумматора и входами соответственно первого и второго матричных блоков элементов НЕ, выходы которых связаны с первым и вторым входами второго матричного блока элемента ИЛИ-НЕ, введён матричный блок сдвига, причем вьлход первого матричного блока элементов ИЛИ-НЕ связан с первым выходом первого матричного блока эле1уюнтов ИЛИ, выход второго матричного блока элементов ИЛИ-НЕ-связан с вторым входом пер- . вого матричного блока элементов ИЛИ и с первым входом третьего матричног блока элементов ИЛИ-НЕ, второй выход которого связан с выходом матричного блока сдвига, выход которого связан с первыми входами четвертого и пятог матричнь;1Х блоков элементов ИЛИ-НЕ, выход первого матричного блока элементов ИЛИ связан с первым входом шестого матричного блока элементов ИЛИ-НЕ и с вторым входом четвертого матричного блока элементов ИЛИ-НЕ, выход которого является выходом переноса сумматора и связан с вторым вйодом третьего матричного блока элементов ИЛИ-НЕ и вторыми входами пятого и шестого матричных блоков элементов ИЛИ-НЕ, выходы которых связаны с соответствующими входами второго матричного блока элементов ИЛИ, выход которого является выходом суммы сумматора,

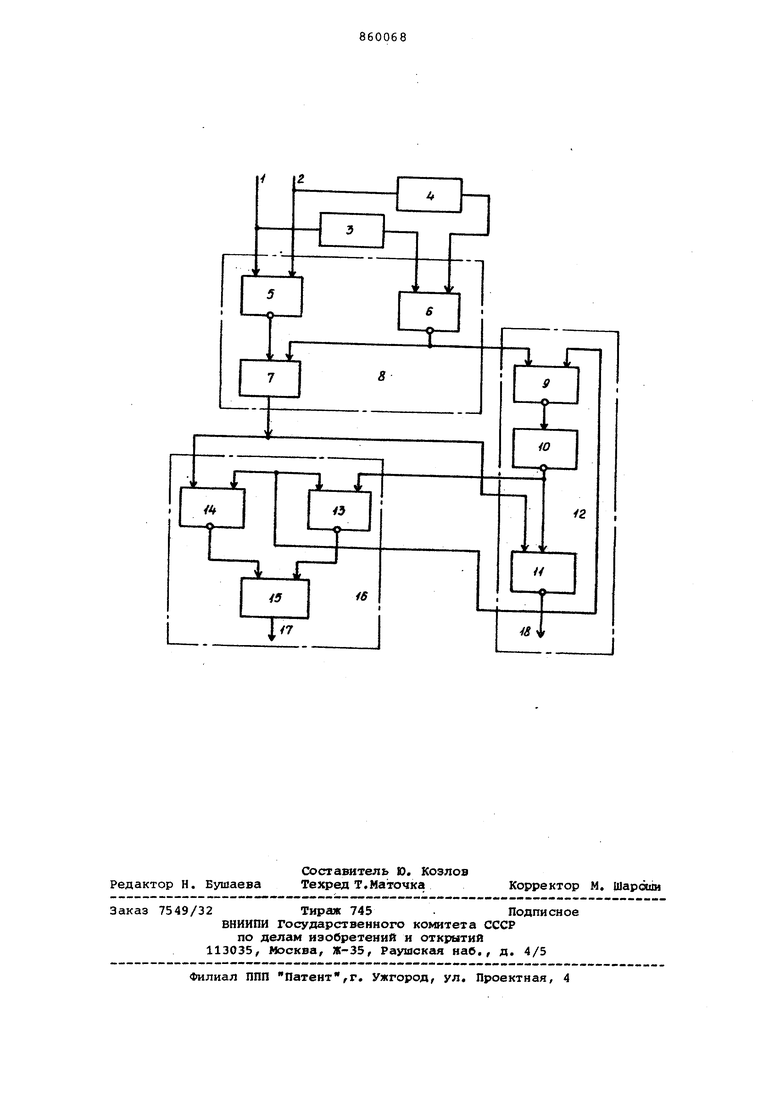

На чертеже приведена принципиальная схема предлагаемого комбинационного матричного сумматора.

Сумматор содержит матричные входы 1 и 2, первый 3 и второй 4 матричные блоки элементов НЕ, первый 5 и второ 6 матричные блоки элементов ИЛИ-НЕ и первый 7 матричный блок элементов ИЛ И, $1 образующие первый матричный блок равнозначности 8, третий матричный блок элементов ИЛИ-НЕ 9, матричный блок 10 сдвига и четвертый матричный блок 11 элементов ИЛИ-НЕ , образующие матричный блок 12 переноса, пятый 13 и шестой 14 матричные блоки элементов ИЛИ-НЕ и второй 15 матричный блок элементов ИЛИ, образуквдие второй матричный блок 16 равнозначнисти, выход которого является выходом суммы сумматора 17,

На чертеже цифрой 18 обозначен выход переноса сумматора.

Для реализации оптикоэлектронной картинной обработки информации матричные блоки элементов НЕ и ИЛИ и ИЛИ-НЕ могут быть, в частности, выполнены на активных оптически управляемых транспарантах,

Масси вы чисел в числовых картинах и которые являются входной информацией сумматора, представлены в поцизионной двоичной системе счисления в дополнительном или обратном коде таким образом, что для каждого числа для записи отводится одна строка в матрице, т,е, общее количество строк в матрице (числовой картине) определяет общее количество чисел в массиве чисел.

Устройство работает следующим образом.

Две числовые картины, соответствующие двум массивам чисел, в виде матрицы сигналов подаются на матричные входы 1 и 2 сумматора и на матричные блоки 3 и 4 элементов НЕ, Первый матричный блок 8 равнозначности при помощи первого 5 и второго 6 матричных блоков элементов ИЛИ-НЕ, матричного блока 7 элементов ИЛИ вьарабатывает две матрицы выходных сигналов первая из которых снимается с в{дхода матричного блока 7 элементов Ш1И а вторая с выхода второго матричного блока 6 элементов ИЛИ-НЕ..

}

iZ, {аТ;, )N (S

IK

IK

biV

V a

iK

IK

(

IK)}

ь

IK

Матрицы сигналов , PiV5 О ступают соответственно на вхвды четвертого 11 и третьего 9 матрлчных- блоков элементов ИЛИ-НЕ паргшлельного (сквоз-ного) формирования матрицы переноса в блоке 12 ,в результате происходит управление выработкой матрицы сигналов переноса,Матричный блок 10 . сдвига сдвигает матрицы сигналов т4 Р к инвертируется третьим матричным .блоком 9 элементов ИЛИ-НЕ на один раз-; ряд в сторону старшего разряда, т,е, происходит сдвиг картины на один столбец влево,если каждое число записано на одной строке.Матрица сигналов , поданная на один вход четвертого матричного блока 11 элементов ИЛИ-НЕ, управляет прохождением, сигналов переноса в ставшие разряды с помощью цепи обратной связи с выхода четвертого матричного блока 11 элементов ИЛИ-НЕ на второй вход третьего матричного блока 9 элементов ИЛИ-НЕ и далее на вход матрично5 г е5лока 10 сдвига. Матрица переноса

С формируется в соответствии с вы-л ражением

C,V5 4-r..K Z,V,, ) V ...

V(Pn, V Z.j.KV ,1У ...Уг,к)). Матрицы сигналов поступают на входы второго матричного блока 16 равнозначности, на матричных выход иг 17 которого формируется окончательная матрица сумкы

i«5 mfKV(e,vvZ,-K))v(C,-Jb

- C.V V Ч- C V Махрица суммы снимается с выхода 17 сумматора только после формирования матрицы переноса выходе матричного блока 10 сдвига, если число столбцов в числовой картине (матрице) равно суммарному времени одного срабатывания третьего 9 и четвертого 11 матричных блоков элементов ИЛИ-НЕ.

формула изобретения

Комбинационный матричный сумматор, содержащий матричные блоки элементов НЕ и ИЛИ и ИЛИ-НЕ, первый и второй входы первого матричного блока элементов ИЛИ-НЕ связаны с соответствукицими входами сумматора и входанш соответственно первого и второго матричных блоков элементов НЕ, выходы которых связаны с первым и втоyaiA входеши второго матричного блока элементов ИЛИ-НЕ, отличающийся тем, что, с целью увеличения быстродействия и упрощения сумматора, в него введен матричный блок

сдвига, причем выход первого матричного блока элементов ИЛИ-НЕ связан с первым выходом первого матричного блока элементов ИЛИ, выход второго матричного блока элементов ИЛИ-НЕ связан с вуорьал входом первого матричного блока элементов ИЛИ и с первым входом третьего матричного блока элементов ИЛИ-НЕ, второй выход которого связан с матричного блока сдвига, выход которого связан с первыми входами четвертого и пятого матричных блоков элементов ИЛИ-НЕ первого матричного блока элементов ИЛИ связан с первым входом шестого матричного блока элементов ИЛИ-НЕ и с вторым входом четвертого матричного блока элементов ИЛИ-НЕ, выход которого является выходом переноса сумматора и связан с вторым входом третьего матричного блока элементов ИЛИ-НЕ и вторыми входами пятого и шестого матричных блоков элементов ИЛИ-НЕ, выходы которых связаны с входами второго матричного блока элементов ИЛИ, выход которого является выходом суммы -сумматора.

Источешки информации, Ьривятые во вынимание при экспертизе

1. Авторское свидетельство СССР 590739, кл. G 06 F 7/56, 1976.

.2, Авторское свидетельство СССР по заявке 2687554/18-24, кл, 6 06 F 7/56, 1978.

3. Свидаинский к.к. Элементная база опти юских ЦвМ. - Электронная пр01«вш1е11ность, 1973, 4, с. 61, рис. 6 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для формирования переноса матричного сумматора | 1979 |

|

SU860069A1 |

| УСТРОЙСТВО ДЛЯ ПЕРЕМНОЖЕНИЯ ЧИСЛОВЫХ МАТРИЦ | 1991 |

|

RU2022334C1 |

| Оптоэлектронное модульное устройство для параллельного сложения оптических цифровых картин в системе остаточных классов | 1990 |

|

SU1751783A1 |

| УСТРОЙСТВО ДЛЯ УМНОЖЕНИЯ МАТРИЦ КАРТИН-ИЗОБРАЖЕНИЙ | 1991 |

|

RU2018916C1 |

| Устройство для умножения квадратных матриц картин-изображений | 1989 |

|

SU1781679A1 |

| Матричное устройство для деления | 1985 |

|

SU1247863A1 |

| Устройство для умножения | 1988 |

|

SU1578711A1 |

| Устройство для умножения | 1988 |

|

SU1670685A1 |

| Устройство для считывания информации | 1973 |

|

SU462189A1 |

| Универсальное суммирующее устройство | 1990 |

|

SU1786484A1 |

Авторы

Даты

1981-08-30—Публикация

1979-08-09—Подача