Изобретение относится к автоматике и вычислительной технике и может быть использовано для контроля и диагностики неисправностей распределительных устройств при их изготовлении, эксплуатации и ремонте.

Цель изобретения - повышение точности контроля.

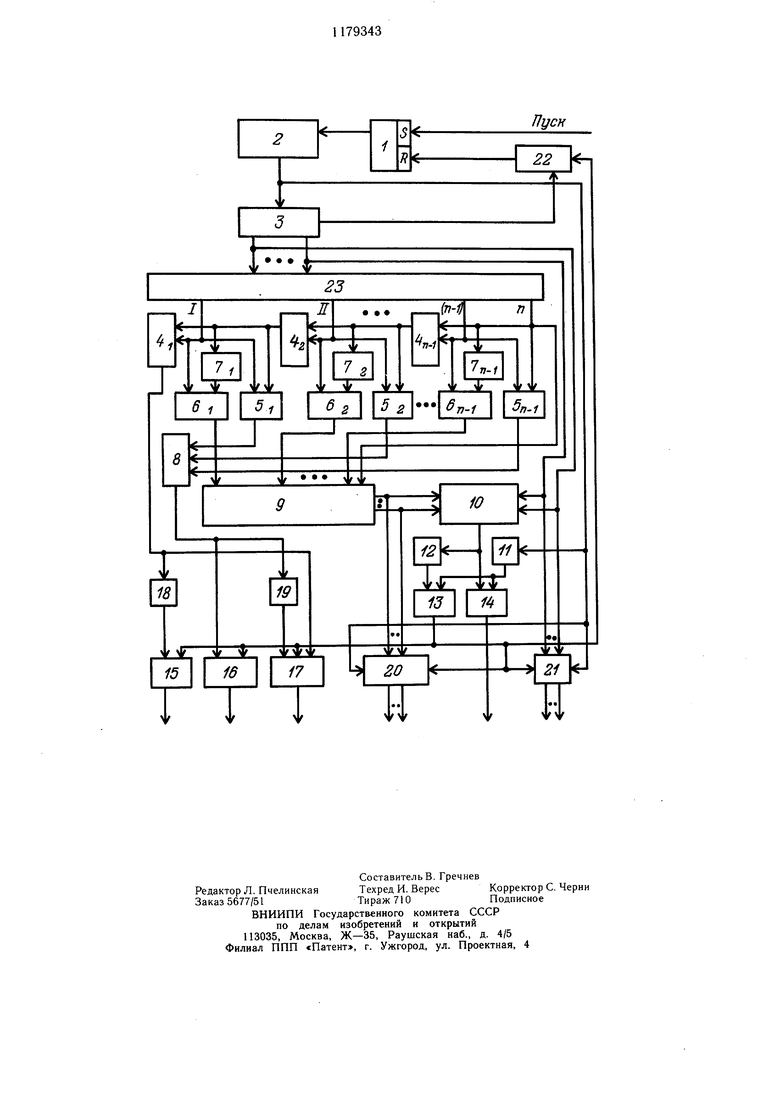

На чертеже приведена структурная схема устройства для контроля дешифратора.

Устройство содержит триггер 1, генератор 2 импульсов, счетчик 3, группу 4 элементов ИЛИ, первую группу 5 элементов И, вторую группу б элементов И, группу 7 элементов НЕ, первый элемент ИЛИ 8, шифратор 9, блок 10 сравнения, элемент 11 задержки, второй элемент НЕ 12, первый 13, второй 14, третий 15, четвертый 16 и пятый 17 элементы И, третий 18 и первый 19 элементы НЕ, второй 20 и первый 21 регистры, а также второй элемент ИЛИ 22. На чертеже показан контролируемый Дешифратор 23, который в предлагаемое устройство не входит.

Устройство работает следуюшим образом.

Перед началом работы счетчик 3 устанавливается в нулевое состояние. По импульсному сигналу «Пуск, поступаюш,ему на вход запуска устройства, устанавливается в единичное состояние триггер 1, который включает генератор 2 импульсов. Генератор 2 тактовыми импульсами последовательно заполняет счетчик 3, состояния которого декодируются дешифратором 23. При этом выходы дешифратора 23 последовательно возбуждаются, каждому выходу дешифратора соответствует определенное состояние счетчика 3, т. е. двоичный код на его информационном выходе, который подается на второй вход блока 10 сравнения и информационный вход регистра 21. Кроме того, в каждом такте импульс генератора 2 обнуляет регистры 20 и 2 и подается на вход элемента 11 задержки для последующего считывания состояний элементов И 13 и 14. При исправной работе дешифратора 23 в каждом такте всегда возбужден только один его выход, например, в (п-1)-м такте возбужден выход (п-1)-й. Сигнал с (п-1)го выхода дешифратора 23 через последовательную цепь элементов ИЛИ группы 4 подается на вход элемента И 17 и через элемент НЕ 18 закрывает элемент И 15. При этом сигнал на выходе каждого из элементов ИЛИ группы 4 через соответствующие элементы НЕ группы 7 закрывает предыдущие элементы И группы 6. Так как на последующем л-м выходе дешифратора 23 сигнал также отсутствует, то на выходе (и-1)-го элемента НЕ группы 7 формируется сигнал, разрешающий открывание (п-1) -го элемента И группы 6. Поэтому сигналом с (п-1)-го выхода дешифратора 23 открывается (п-1)-и элемент И второй группы 6, с выхода которого выдается сигнал

на вход шифратора 9. На выходе шифратора 9 формируется двоичный код, который подается на первый вход блока 10 сравнения. При совпадении кодов шифратора 9 и счетчика 3 на выходе блока 10 сравнения формируется сигнал исправности, который через элемент НЕ 12 закрывает элемент И 13 и подготавливает к открыванию элемент И 14. С выхода элемента 11 задержки в каждом такте выдается считывающий импульс, который открывает элемент И 14. Время задержки 11 элемента превышает суммарное время переходных процессов в счетчике 3, дешифраторе 23, элементах ИЛИ группы 4, -элементах И первой 5 и второй 6 групп, шифраторе 9 и блоке 10 сравнения. На выходе элемента И 14 формируется сигнал исправности, который поступает на выход исправности устройства. Далее процесс контроля дешифратора 23 повторяется в последующих тактах

0 работы генератора 2 и счетчика 3. После заполнения счетчика 3 на его выходе переполнения формируется сигнал, который через элемент ИЛИ 22 устанавливает в нулевое состояние триггер 1 и генератор 2 импульсов отключается. Повторный запуск устройства осуществляется новой подачей сигнала «Пуск на вход запуска устройства.

В случае неисправности дешифратора типа «Обрыв в данном также отсутствуют сигналы на всех выходах дешифратора 23, включая проверяемый выход, все элементы И первой 5 и второй 6 групп закрыты и на выходах элементов ИЛИ группы 4 сигналы отсутствуют. При этом через элемент НЕ 18 подготовлен к открыванию элемент И 15. На выходе шифратора 9 код

не формируется,т. е. совпадения кодов на входах блока 10 сравнения не происходит и на его выходе сигнал совпадения не формируется. Поэтому элемент И 14 закрыт, элемент И 13 подготовлен к открыванию сигналом с выхода элемента НЕ 12. Импульс считывания с выхода элемента 11 задержки открывает элемент И 13, на выходе которого формируется сигнал ошибки. Этот сигнал открывает элемент И 15, с выхода которого выдается сигнал на выход обрыва устройства. Кроме того, этот сигнал разрешает запись кода с выхода шифратора 9 в регистр 20 и кода с выхода счетчика 3 в регистр 21, а также через элемент ИЛИ 22 обнуляет триггер 1 и отключает генератор 2 импульсов. Таким образом, при неисправности в дешифраторе 23 работа устройства прерывается, в регистре 21 устанавливается код проверяемой цепи, по которой произошел обрыв в дешифраторе 23.

В случае неисправности дешифратора 23

5 типа «Ошибка соединения сигнал фор.мируется не на данном его выходе, а на любом другом выходе дешифратора 23, например

в (п-1)-м такте сигнал формируется вместо (п-1)-го выхода на п-м выходе. В этом случае по цепям, описанным выше, формируется сигнал на выходе первого элемента ИЛИ группы 4, который закрывает через элемент НЕ 18 элемент И 15 и подготавливает к открыванию элемент И 17. Так как на выходах дешифратора 23 имеется только один сигнал на п-м выходе, элементы И первой группы 5 закрыты и сигнал с выхода элемента НЕ 19 также подготавливает к открыванию элемент И 17. Сигнал с п-го выхода дешифратора 23 подается на шифратор 9, при этом коды на выходах шифратора 9 и счетчика 3 не совпадают. Блок 10 сравнения не формирует сигнал исправности, и аналогично описанному с выхода элемента И 13 считывается сигнал ошибки, который останавливает генератор 2, открывает элемент И 17 и разрешает запись кодов шифратора 9 и счетчика 3 в регистры 20 и 21 соответственно. Таким образом, с выхода элемента И 17 выдается сигнал на выход ошибки соединения устройства, в регистре 21 записан код проверяемого (п-1)-го выхода дешифратора 23, в регистре 20 - код неправильно выбранного п-го выхода дешифратора 23.

В случае неисправности дешифратора типа «Короткое замыкание сигнал формируется на двух и более выходах дешифратора 23, например в (п-1)-м такте на (п-1)-м и п-м выходах дешифратора 23. В этом случае формируется сигнал на выходе первого элемента ИЛИ группы 4 и совпадают сигналы на входах (и-1)-го элемента И группы 5, который открывает первый элемент ИЛИ 8 и подготавливает к открыванию элемент И 16. При этом сигнал на п-м выходе дешифратора 23 имеет приоритет над всеми сигналами на всех предыдущих его выходах, так как этот сигнал

через (п-1)-й элемент НЕ группы 7 закрывает (п-1)-й элемент И второй группы 6 и через последовательную цепь предыдущих элементов ИЛИ группы 4 и соответствующие элементы НЕ группы 7 закрывает все элементы второй группы 6. Таким образом,

при наличии нескольких сигналов на выходах дешифратора 23 на входы шифратора 9 поступает сигнал только с одного выхода дешифратора 23, имеющего приоритет над другими его выходами. В данном случае коды на входах блока 10 сравнения не

5 совпадают, на выходе элемента И 13 формируется сигнал ошибки, который открывает элемент И 16 и разрешает запись кодов в регистры 20 и 21. При этом с выхода элемента И 16 выдается сигнал на

0 выход короткого замыкания устройства, в регистре 21 записывается код проверяемого (п-1)-го выхода дешифратора, в регистре 20 - код п-го выхода, который замыкается на проверяемый (п-1)-й выход дешифратора 23. Аналогично работает устройство

5 при любых других комбинациях неисправных выходов дешифратора 23. Так как при всякой неисправности дешифратора работа устройства прерывается для документирования оператором признаков неисправности, то для продолжения его работы необходимо снова подать сигнал «Пуск на вход триггера 1. При этом работа устройства продолжается с состояния счетчика, модифицированного на -|-1 относительно его состояния, в котором возникла остановка по неисправности.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство для проверки электрических межразъемных соединений | 1985 |

|

SU1394181A1 |

| Программируемый коммутатор | 1985 |

|

SU1287277A1 |

| Устройство для управления реконфигурацией резервированной вычислительной системы | 1991 |

|

SU1837296A1 |

| Устройство для преобразования кодов | 1983 |

|

SU1131033A1 |

| Устройство для регистрации неисправных блоков | 1985 |

|

SU1260959A1 |

| Микропрограммное устройство управления | 1983 |

|

SU1164706A1 |

| Устройство для фиксации сбоев | 1979 |

|

SU860074A1 |

| Устройство поиска неисправных блоков и элементов | 1989 |

|

SU1709351A1 |

| Устройство для программногоупРАВлЕНия Об'ЕКТАМи | 1978 |

|

SU807219A1 |

| Устройство сопряжения с магистралью последовательного интерфейса | 1983 |

|

SU1275417A1 |

УСТРОЙСТВО ДЛЯ КОНТРОЛЯ ДЕШИФРАТОРА, содержащее счетчик, генератор импульсов, первую группу элементов И, первый элемент НЕ, два элемента ИЛИ и первый элемент И, причем информационный выход счетчика соединен с адресным входом контролируемого дешифратора, вход первого элемента НЕ соединен с выходом первого элемента ИЛИ, входы которого соединены с выходами соответствующих элементов И первой группы, первый вход каждого г-го элемента И первой группы соединен с г-м выходом контролируемого дешифратора (l.i:4,(n-1), где п - количество выходов контролируемого дешифратора), отличающееся тем, что, с целью повышения точности контроля, в него введены группа элементов НЕ, группа элементов ИЛИ, вторая группа элементов И, два элемента НЕ, четыре элемента И, элемент задержки, два регистра, блок сравнения, шифратор и триггер, причем прямой выход триггера соединен с входом запуска генератора импульсов, выход которого соединен со счетным входом счетчика, входом элемента задержки и входами сброса первого и второго регистров, выходы которых являются выходом контролируемого кода и выходом выбранного кода устройства соответственно, второй вход каждого /-го элемента И первой группы объединен с первым входом /-ГО элемента И второй группы и первым входом г-го элемента ИЛИ группы, выход каждого /-го элемента ИЛИ группы

| Устройство для контроля информации по модулю три | 1976 |

|

SU634282A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

| Устройство для контроля дешифратора | 1979 |

|

SU886001A1 |

| Приспособление для точного наложения листов бумаги при снятии оттисков | 1922 |

|

SU6A1 |

Авторы

Даты

1985-09-15—Публикация

1984-03-30—Подача