1

Изобретение относится к вычислительной технике и может быть использовано в различных устройствах автоматики и вычислительной техники.

Известно множительное устройство, содержащее интегратор, вход которого соединен с первым входом устройства, а выход соединен с первь м входом компаратора, второй вход которого соединен с вторым входов устройства, а выход компаратора подключен к входу интегратора и к управляющему входу фазочувствительного выпрямителя, вход которого подключен к выходу интегратора, а выход - к выходу устройства, причем дополнительно оно содержит фильтр и сумматор, вход фильтра подключен к выходу интегратора, а выход - к первому входу сумматора, выход которого соединен с вторым входом компаратора, второй вход сумматора соединен с вторым входом устройства 1.

Указанное устройство характеризуется сложностью схемного решения, а также недостаточной точностью и небольшим диапазоном входных сигналов за счет нелинейности на выходам интеграторов.

Наиболее близким по технической сущности к предлагаемому является множительное устройство, содержащее основной и вспомогательный RC-интеграторы, входы которых через ключевые элементы подключены к входу устройства, а выходы подключены соответственно к квантующему устройству и входу компаратора, второй вход ком10паратора соединен со входом устройства, а выход - со входом квантователя, выход квантователя подключен к входу сглаживающего фильтра, выход которого является выходом устрой15ства 2 .

Это множительное устройство отличается низкой точностью за счет нелинейности выходных характеристик интегрирующих цепей, а также малым

20 диапазоном входных сигналов.

Цель изобретения - повышение точности и расширение диапазона изменения входных сигналов множительного устройства.

25

Поставленная цель достигается тем, что в множительное устройство, содержащее основной и вспомогательный интеграторы, компаратор,.первый вход которого подключен к эыходу вспомогательного интегратора, а второй

вход является входом первого сомножителя устройсва, введены первь:й и второй запоминающие блоки, последот вательно соединенные делитель частоты, дифференцирующий элемент и инвертор, первый, второй и третий ключевые элементы, причем вход первого запоминающего блока является входом второго сомножителя устройства, а вход второго запоминающего блока подключен к выходу делителя частоты,

выходы первого и второго запоминающих блоков соответственно подключены ко входам основного и вспомогательного интеграторов, выХоды которых через первый и второй ключевые элементы соответственно подключены к шине нулевого потенциала, управляющие входы первого и второго ключевых элементов объединены и подключены к выходу инвертора, выход основного интегратора через третий ключевой элемент подключен к выходу устройства, управляющий вход третьего ключевого элемента подключен к выходу компаратора.

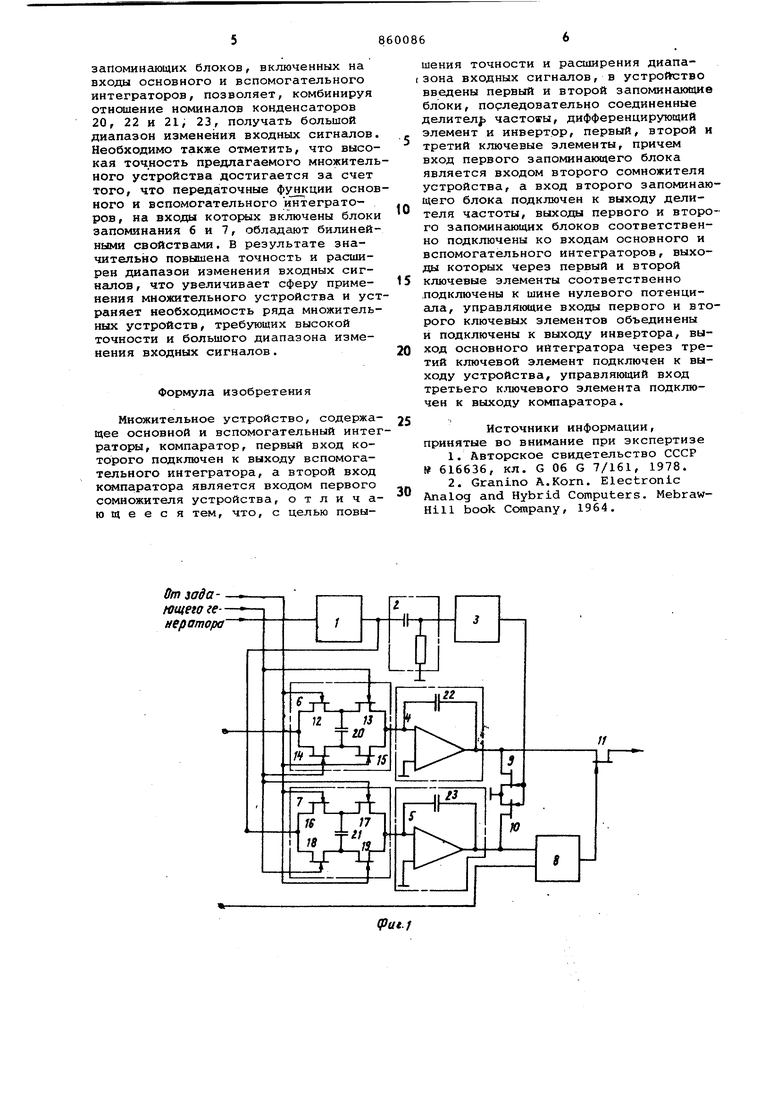

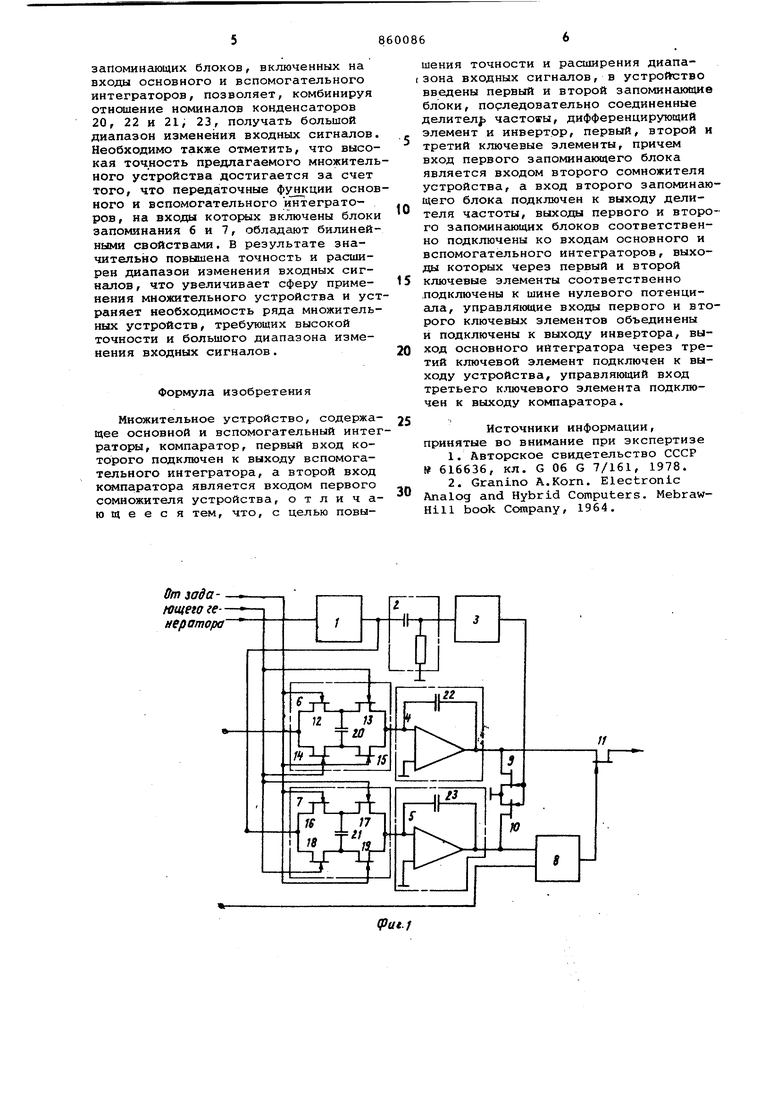

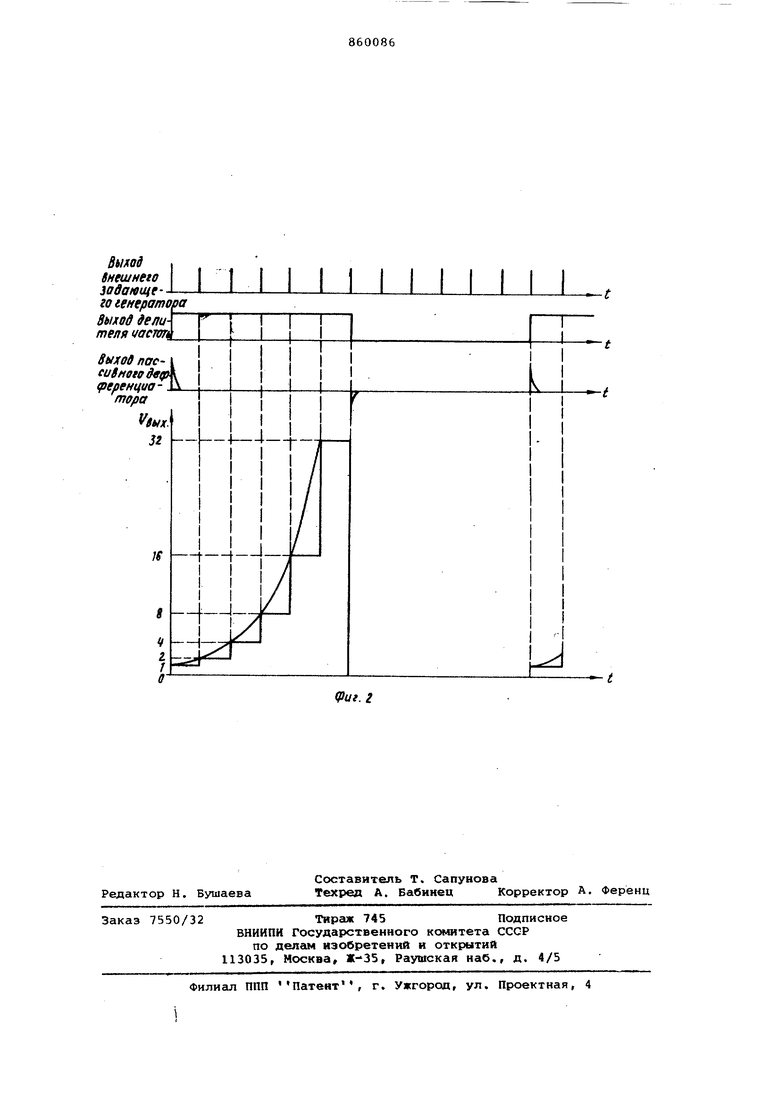

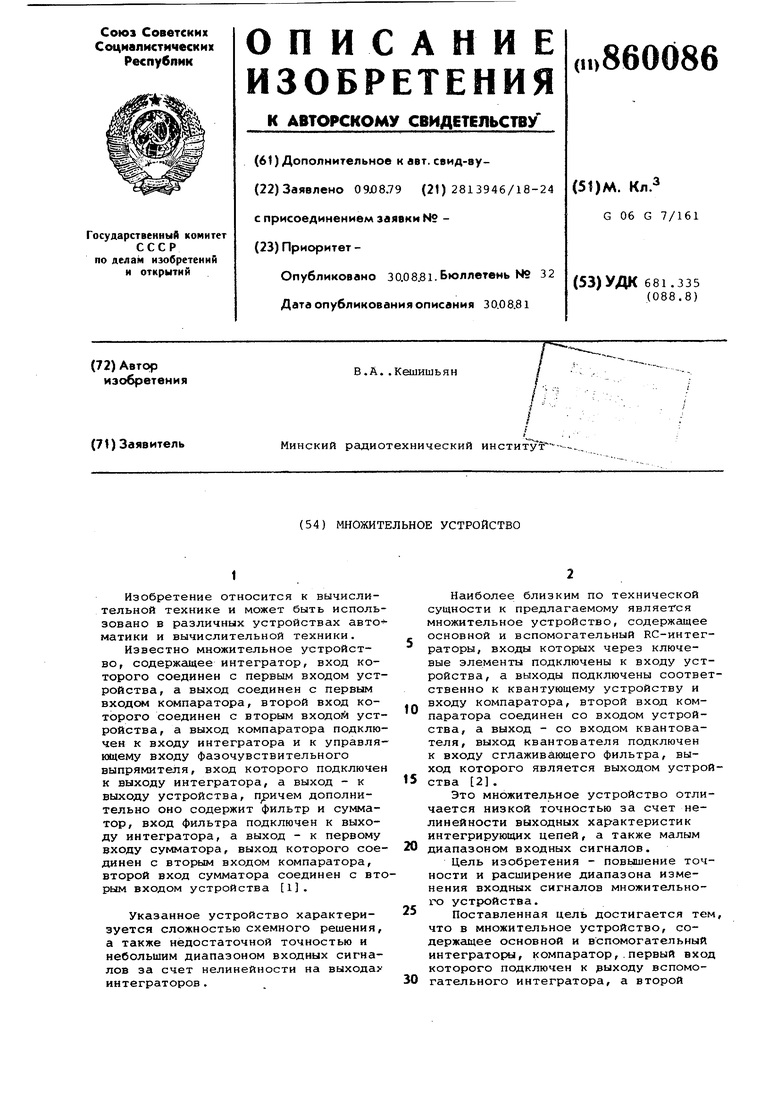

На фиг. 1 приведена функциональная схема множительного устройства; на фиг. 2 - временная диаграмма, поясняющая работу мнолсительного устройства.

Множительное устройство содержит делитель 1 частоты внешнего задающего генератора, дифференцирующий элемент 2, инвертор 3, основной интегратор 4, вспомогательный интегратор 5, первый запоминающий блок 6 второй запоминающий блок 7, компаратор 8, первый ключевой элемент 9, второй ключевой элемент 10, третий ключевой элемент 11, ключевые элементы 12 - 19 на транзисторах и конденсаторы 20 - 23.

Множительное устройство работает следующим образом.

На вход второго запоминающего блока поступает эталонное напряжение с постоянной амплитудой и постоянной длительностью с выхода делителя 1 частоты, который управляется от внешнего задающего генератора. Длительность импульса напряжения, подаваемого на вход второго запоминающего блока 7, может регулироваться внешним задающим генератором, обеспечивая тем самым необходимый размах перемножаемых функций. В моменть времени t 0,2,4... (фиг. 2) открываются ключевые элементы 12, 15 , 19, а в моменты t 1,3,5.. открываются ключевые элементы 13,14 и 17,18. Включение соответствующих пар ключевых элементов обеспечивает заряд конденсаторов 20 и 21.

Рассмотрим первый интервал времени t от О до 1. В момент t О включены ключевые элементы 12, 15 и 16, 19, Б результате конденсатор 20 заряжается до напряжения на входе первого запоминающего блока 6, а конденсатор 21 - до эталонного напряжения, существующего на входе второго запоминающего блока 7 и подаваемого с делителя 1 частоты. Следовательно, в интервале времени t от О до 1 напряжения на конденсаторах 20 и 21 соответствуют входным напряжениям блоков б и 7. Необходимо отметить, что при равенстве номиналов конденсаторов 20, 22 и 21, 23 напряжения на выходах основного и вспомогательного интеграторов 4 и 5 равны соответствующим напряжениям на конденсаторах 20 и 21. При неравенстве номиналов конденсаторов 20,22 и 21,23 напряжения на выходах интеграторов 4 и 5 будут в линейной зависимости от напряжения на входах запоминающих блоков, что позволяет варьировать в широких пределах разма величин перемножаемых функций. В момент t 1 включены ключевые элементы 13,14 и 17,18, в результате конденсаторы 20 и 21 получают дополнительный заряд энергии, а напряжение на них удваивается (фиг. 2). В следущем интервале времени t от 2 до 3 напряжение на конденсаторах 20, 21, а следовательно, и на выходах интеграторов 4 и 5 утраивается и т.д. Процесс нарастания напряжения на конденсаторах 20 и 21, а следовательно и на выходах интеграторов 4,5 продолжается до тех пор, пока напряжение, подаваемое на первый вход устройства, не сравняется с напряжением на выходе вспомогательного интегратора 5. При равенстве напряжений на первом входе устройства и на выходе вспомогательного интегратора 5 срабатывает компаратор 8 и включает третий ключевой элемент -11, обеспечивая в этот момент прохождение напряжения с выхода основного инт гратора 4 на выход устройства (это напряжение равно произведению двух функций, подаваемых на входы устройства) По окончании действия положительного импульса напряжения с делителя 1 частоты на выходе дифференцирующего элемента 2 формируется короткий импульс отрицательной полярности, который после инвертирования в инверторе 3 поступает на управляющие входы ключевых элементов 10, включая последние. Это обеспечивает практически мгновенное уменьшение выходных напряжений с выходов интеграторов 4 и 5 до нулевого значения. При подходе следующего положительного импульса напряжения на вход второго запоминающего блока 7 с делителя 1 частоты вновь начинается процесс перемножения.

Технико-экономические преимущества предлагаемого множительного устройства по сравнению с известным заключаются в том, что использование

запоминающих блоков, включенных на входы основного и вспомогательного интеграторов, позволяет, комбинируя отнслаение номиналов конденсаторов 20, 22 и 21, 23, получать большой диапазон изменения входных сигналов. Необходимо также отметить, что высокая точность предлагаемого множительного устройства достигается за счет того, что передаточные функции основного и вспомогательного интеграторов , на входы которых включены блоки запоминания 6 и 7, обладают билинейными свойствами. В результате значительно повышена точность и расширен диапазон изменения входных сигналов, что увеличивает сферу применения множительного устройства и устраняет необходимость ряда множительных устройств, требующих высокой точности и большого диапазона изменения входных сигналов.

Формула изобретения

Множительное устройство, содержащее основной и вспомогательный интеграторы, компаратор, первый вход которого подключен к выходу вспомогательного интегратора, а второй вход кс 4паратора является входом первого сомножителя устройства, о т л и ч аю Щ е е с я тем, что, с целью повышения точности и расширения диапа(зона входных сигналов, в устройство введены первый и второй запоминающие блоки, последовательно соединенные делител| частоты, дифференцирующий элемент и инвертор, первый, второй и третий ключевые элементы, причем вход первого запоминающего блока является входом второго сомножителя устройства, а вход второго запоминающего блока подключен к выходу дели0теля частоты, выходы первого и второго запомингиощих блоков соответственно подключены ко входам основного и вспомогательного интеграторов, выходы которых через первый и второй

5 ключевые элементы соответственно .подключены к шине нулевого потенциала, управляющие входы первого и второго ключевых элементов объединены и подключены к выходу инвертора, вы0ход основного интегратора через третий ключевой элемент подключен к выходу устройства, управляющий вход третьего ключевого элемента подключен к выходу компаратора.

5

Источники информации, принятые во внимание при экспертизе

1.Авторское свидетельство СССР 616636, кл. G 06 G 7/161, 1978.

2.Granino A.Korn. Electronic

0 Analog and Hybrid Computers. Mebraw- Hill book Company, 1964.

| название | год | авторы | номер документа |

|---|---|---|---|

| Множительно-делительное устройство | 1980 |

|

SU900294A1 |

| Множительно-делительное устройство | 1979 |

|

SU1023344A1 |

| Аналого-цифровое множительное устройство | 1983 |

|

SU1124346A1 |

| Измеритель коэффициента нелинейности пилообразного напряжения | 1980 |

|

SU894607A1 |

| Множительно-делительное устройство | 1981 |

|

SU1001116A1 |

| ПРЕОБРАЗОВАТЕЛЬ ПЕРИОДИЧЕСКОГО СИГНАЛА В ЧАСТОТУ И ПЕРИОД | 2012 |

|

RU2520409C2 |

| Множительно-делительное устройство | 1979 |

|

SU840942A1 |

| Преобразователь частоты | 1982 |

|

SU1092680A1 |

| Множительно-делительное устройство | 1981 |

|

SU993278A2 |

| Множительно-делительное устройство | 1982 |

|

SU1088016A1 |

ffm задаfouieiff генератора

Авторы

Даты

1981-08-30—Публикация

1979-08-09—Подача