(54) УСТЮЙСТВС АСИНХРОННОГО СОПРЯЖЕНИЯ ЦИФРОВЫХ СИГНАЛОВ

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| СИСТЕМА СВЯЗИ | 2003 |

|

RU2249914C2 |

| Дельта-кодек | 1989 |

|

SU1725398A1 |

| СИСТЕМА ДЛЯ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1992 |

|

RU2047908C1 |

| СПОСОБ ПОСЛЕДОВАТЕЛЬНОЙ ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ И СИСТЕМА ДЛЯ ЕГО ОСУЩЕСТВЛЕНИЯ | 2000 |

|

RU2181527C1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| Устройство для контроля многоканального аппарата цифровой магнитной записи | 1988 |

|

SU1607011A1 |

I

Изобретение относится к электросвязи и может быть испояьзовано для асш1хронного ввода - вывода сшгхронной двоичной Ш1формации в цифровые такты с импульсно-кодовой модулявдей и дельта-модулящюй.

Известно устройство асшисронного сопряжения сш1хронных двоичных цифровых сигналов, содержащее на передающей стороне фазовый компаратор, первым своим выходом соединенный с кодером фазы, а вторым выходом с управляющим входом управляемого распределителя, датчик фазирующей комб1шащп1, выход которого подключен к одному из входов блока памяти, а выходы кодера фазы и управляемого распределителя подсоединены соответственно к остальным входам блока памяти, а на приемной стороне содержет KOMNtyтатор, блок фазирования по циклам, вход которого подключен к фазирующему выходу коммутатора, а управляющий выход - к сдвигающему входу коммутатора, декодер фазы, информационные входы которого соединены с выходами служебных сттлалой коммутатора, а управляющий вход - с выходом

опорных сигналов блока фазирования по циклам, управляемый распределитель, управляющий вход которого соедш ен с выходом декодера фазы, а выходы - со входами счтывамня блока памяти, ко входам записи 1шформацпи которого подключены информационные выходы коммутатора 1 .

Недостатком известного устройства является полное отсутствие помехозащ1пценности передаваемой по каналу связн информации и, как следствие, недостаточно высокая достов ность acmixpomioro сопряжения синхронных цифровых сигналов.

Цель нзобретения - повыщенне помехозащн. щетюсти передаваемой га1формащш.

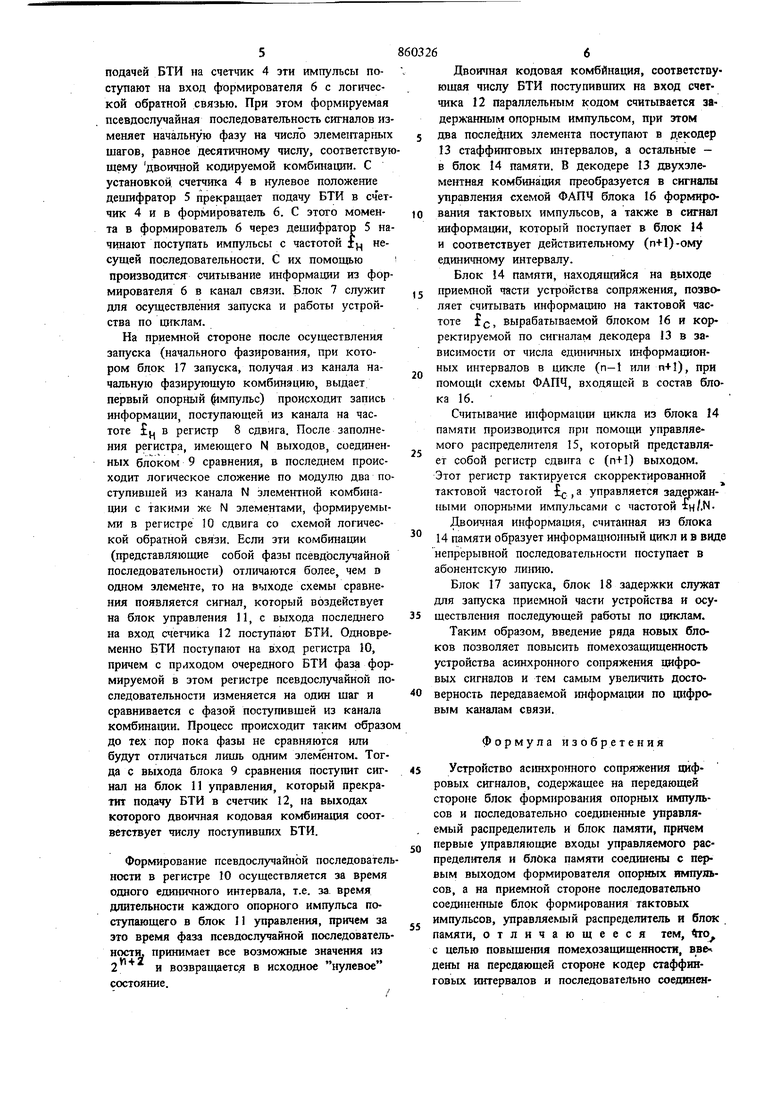

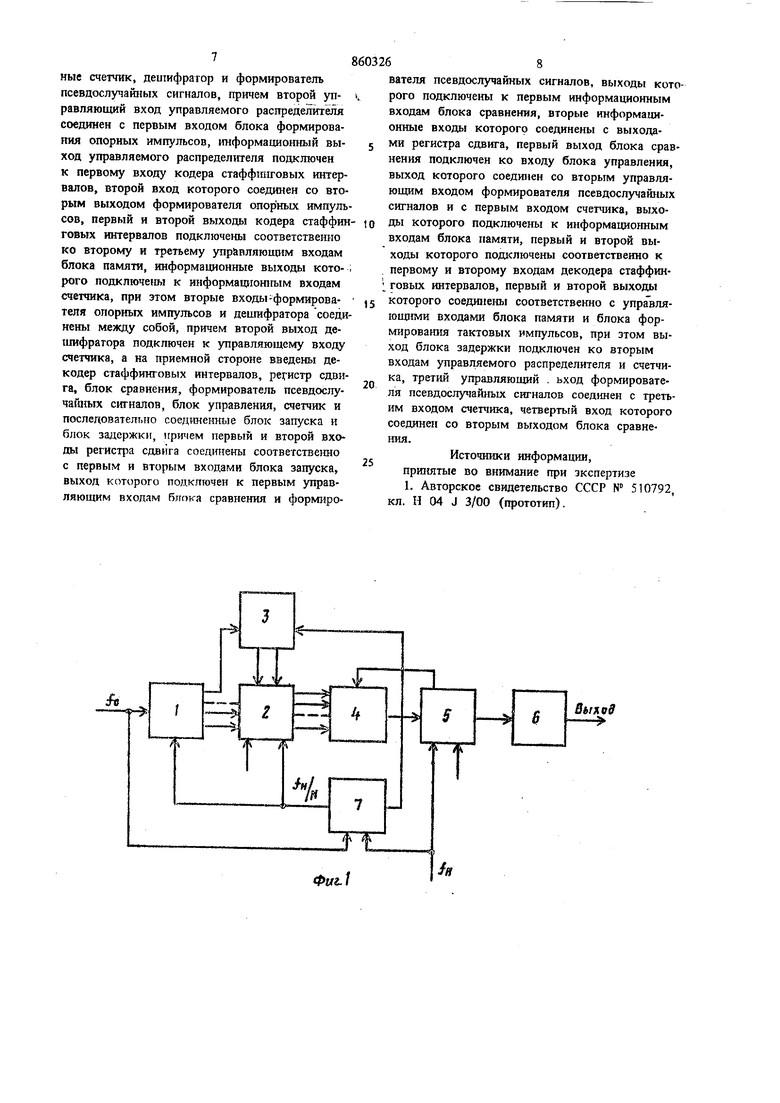

Для дост1Г/кения целн в устройство асинхронного сопряжения цифровых сигналов, содержащее на передающей стороне блок форкпфовапия опорных импульсов и последовательно соедшгенные управляемый распределите и блок памяти, причем первые управляющие входы управляемого распределителя и блока памят : соедшшны с первым выходом формирователя опорных импульсов, а на приемной стороне последовательно соединенные блок формирования тактовых импульсов, управляемый распределитель и блок памяти, введены на передающей стороне кодер стаффкнговых интервалов и последовательно соединенные счетчик, дешифратор и формирователь псевдослучайных сигналов, причем второй управляющий вход управ ляемого распределителя соединен с первым входом блока формирования опорйых импульсов, информационный выход управляемого распределителя подключен к первому входу кодера стаффинговых интервалов, второй вход которого соединен со вторым выходом форми рователя опорных импульсов, первый и второй выходы кодера стаффинговых интервалов подключены соответственно ко второму и третьему управляющим входам блока памяти, информационные выходы которого подключены к информаютонным входам счетчика, при этом вторые входы формирователя опорных импульсов и дешифратора соединены между собой, причем второй выход дешифратора под ключен к управляющему входу счетчика, а на приемной стороне введены декодер стаффинговых интервалов, регистр сдвига, блок сравнения, формирователь псевдослучайных сиг налов, блок управления, счетшк и последовательно соединенные блок запуска и блок задержки, причем первый и второй входы регистра сдвига соединены соответственно с первым и вторым входами блока запуска, выход которого подключен к первым управляющим входам блока сравнения и формирователя псе дослучайных сигналов, выходы которого подключены к первым информационным входам блока сравнения, вторые информационные вхо ды которого соединены с выходами регистра сдвига, первый выход блока сравнения подкл чен ко входу блока управления, выход которого соединен со вторым управляющим входом формирователя псевдослучайных; сигналов и с первым входом счетчика, выходы которо го подключены к Ш1формащюнным входам блока памяти, первый и второй выходы кото рого подключены соответственно к первому и второму входам декодера стаффинтовых интервалов, первый и второй выходы которого соединены соответственно с управляющими входами блока памяти и блока формирования тактовых импульсов, при этом выход блока задержки подключен ко вторым входам управляемого распределителя и счетчюса, третий управляющий вход, формирователя псевдо случайных сигналов соед1ше11 с третьим входом счетчика, четвертый вход которого соеди нен со вторым выходом блока сравнения. На чертежах приведена структурная электрическая схема устройства. На фиг. I показано устройство, передающа сторона; на фиг. 2 - то же, приемная стор Устройство содержит на передающей сторое управляемый распределитель 1, блок 2 амяти, кодер 3 стаффинговых интервалов, чгтшк 4, дешифратор 5, формирователь 6 севдослучайных сигналов, блок 7 формироваия опорных импульсов; на приемной стороне регистр 8 сдвига, блок 9 сравнения, регистр 10 сдвига, бдок 11 управления, счетчик 12, декодер 13 стаффинговых интервалов, блок 14 памяти, управляемый распределитель 15, блок 16 формирования тактовых импульсов, блок 17 запуска и блок 18 задержки. УСТРОЙСТВО работает следующим образом. Для сопряжения синхронных двоичных сигналов, следующих с тактовой частотой f с, и сигналов дифрового канала связи, следующих с частотой ц , несущей последовательность, на передающей стороне устройства в блоке 7 формируются опорные импульсы с частотой f(,|N. Синхронные двоичные сигналы, соответствующие тактовым импульсам, поступают на блок 2 памяти. Эти сигналы, появляющиеся в интервале от одного опорного импульса до другого, образуют информащтонный цикл, который подлежит передаче по Ш1фровому каналу. Опорными импульсами частотой запускается управляемый распределитель 1, представляющий регистр сдвига. Разряды регистра, за исключением первого, обнуляются опорными импульсами. В первый разряд регистра записывается 1, которая продвигается по разрядам импульсами тактовой частоты f. до тех пор, пока не появляется следующий опорный импульс. Запись синхронных двоичных сигналов в блок 2 памяти осуществляется на частоте ( тактовыми импульсами, поступающими с выходов управляемого распределителя 1. Сигналы информационного цикла анализируются затем в кодере 3 стаффинговых интервалов. По сигналам из кодера 3 информационный цикл переменной длины в блоке 2 памяти трансформируется в цикл постоянной длины, содержащий (п 2) единичных двоичных интервала. Кодер 3 стаффинговых интервалов управляется сигналами из блока 7. Считывание информации цикла постоя1шой из ячеек блока 2 памяти производится на частоте опорных импульсов танная информация в параллельном коде поступает на соответствующие входы счетчика 4 и затем на вход дещифратора 5. Если полученная комбинация отличается от нулевой, то дешифратор выдает сигаал, по которому быстрые тактовые импульсы (БТИ) поступают на счетный вход счетчика 4. Эти импульсы подаются до тех пор, пока счетчик не устанавливается в нулевое положение. Одновременно с 5 подачей БТИ на счетчик 4 эти импульсы поступают на вход формирователя 6 с логической обратной связью. При этом формируемая псевдоспучайная последовательность сигналов из меняет начальную фазу на число злеметарратх шатов, равное десятичному числу, соответству щему двоичной кодируемой комбинации. С установкой, счетчика 4 в нулевое положение дешифратор 5 прекращает подачу БТИ в счет чик 4 и в формирователь 6. С этого момента в формирователь 6 через дешифратор 5 на чинают поступать импульсы с частотой i несущей последовательности. С их помощью производится- считывание информации из фор мирователя 6 в канал связи. Блок 7 служит для осуществления запуска и работы устройства по циклам. На прием юй стороне после осуществления запуска (начального фазирования, при котором блок 17 запуска, получая из канала начальную фазирующую комбинацию, выдает первый опорный фмпульс) происходит запись информации, поступающей из канала на частоте j в регистр 8 сдвига. После заполнения регистра, имеющего N выходов, соединенных блоком 9 сравнения, в последнем происходит логическое сложение по модулю два по ступившей из канала N элемеетной комбшгации с такими же N элементами, формируемыми в регистре 10 сдвига со схемой логической обратной связи. Если эти комбинации (представляющие собой фазы псевдослучайной последовательности) отличаются более чем D одном элементе, то на выходе схемы сравнения появляется сигнал, который воздействует на блок управления 11, с выхода последнего на вход счетчика 12 поступают БТИ. Одновременно БТИ поступают на вход регистра 10, причем с приходом очередного БТИ фаза фор мируемой в этом регистре псевдослучайной по следовательности изменяется на один шаг и сравнивается с фазой поступивщей из канала комбинации. Процесс происходит таким образо до тех пор пока фазы не сравняются или будут отличаться лишь одним элементом. Тогда с выхода блока 9 сравнешш поступит сигнал на блок 11 управления, который прекратит подачу БТИ в счетчик 12, па выходах которого двоичная кодовая комбинация соответствует числу поступивишх БТИ. Формирование псевдослучайной последователь ности в регистре 10 осуществляется за время одного единичного интервала, т.е. за. время длительности каждого опорного импульса поступающего в блок 11 управления, причем за это время фаза псевдослучайной последоватеяь ност принимает все возможные значения из 2 и возвращаете в исходное нулевое состояние. 6 Двоитая кодовая комбинация, соответствующая числу БТИ поступивших на вход счетчика 12 параллельным кодом считывается задержанным опорным импульсом, при этом два последних элемента поступают в декодер 13 стаффигповых 1штервалов, а остальные - в блок 14 памяти. В декодере 13 двухэлементная комбинадая преобразуется в сигналы управления схемой ФАПЧ блока 16 формирования тактовых импульсов, а также в сигнал информации, который поступает в блок 14 и соответствует действительному (п+1)-ому единичному интервалу. Блок 14 памяти, находящийся на выходе приемной части устройства сопряжения, позволяет сч1ггывать информацию на тактовой частоте fc, вырабатываемой блоком 16 и корректируемой по сигналам декодера 13 в зависимости от числа единичных информационных интервалов в цикле (п-1 или n+l), при помощи схемы ФАПЧ, входящей в состав блока 16. Считывание ипформащш цикла из блока 14 памяти производится при помощи управляемого распределителя 15, который представляет собой регистр сдвига с (п+1) выходом. Этот регистр тактируется скорректированной тактовой частотой ;. ,а управляется задержанными опорными импульсами с частотой тн/.Двоичная информация, считанная из блока 14 памяти образует информационный цикл и в виде непрерывной последовательности поступает в абонентскую ли}шю. Блок 17 запуска, блок 18 задержки служат для запуска приемной части устройства и осуществления последующей работы по циклам. Таким образом, введение ряда новых блоков позволяет повысить помехозащищенность устройства асинхронного сопряжения цифровых сигналов и тем самым увеличить достоверность передаваемой 1шформации по цифровым каналам связи. Формула изобретения Устройство ас1шхро1шого сопряжения цифровых сигналов, содержащее на передающей стороне блок формирования опорных импульсов и последовательно соещшенные управляемый распределитель и блок памяти, причем первые управляющие входы управляемого распределителя и блока памяти соединены с первым выходом формирователя опорных импульсов, а на приемной стороне последовательно соединегпшге блок формирования тактовых импульсов, управляемый распределитель и блок памяти, отличающееся тем, го целью повыщеш1я помехозащищенности, вве ены на пертдающей стороне кодер стаффиновых интервалов и последовательно соединенные счетчик, дешифратор и формирователь псевдослучайных сигналов, причем второй управляющий вход управляемого распределителя соединен с первым входом блока формирования опорных импульсов, информационный выход управляемого раснределотеля подключен к первому входу кодера стаффтпп-овых интервалов, второй вход которого соединен со вторым выходом формирователя импуль сов, первый и второй выходы кодера стаффин говых интервалов подключены соответственно ко второму и третьему управляющим входам блока памяти, информационные выходы которого подключены к информационным входам счетчика, при этом вторые входы-формирователя опорных импульсов и дешифратора соеди нены между собой, причем второй выход дешифратора подключен к управляющему входу счетчика, а на приемной стороне введены декодер стаффинговых интервалов, регистр сдвига, блок сравнения, формирователь псевдослучайных сигналов, блок управления, счетчик и последовательно coeflvmemttie блок запуска и блок задержки, причем первый и второй входы регистра сдвига соещтнены соответственно с первым и вторым входами блока запуска, выход которого подключен к первым управляющим входам бтгока сравнения и формироФг/г./ вателя псевдослучайных сигналов, выходы которого подключены к первым информационным входам блока сравнения, вторые информационные входы которого соединены с выходами регистра сдвига, первый выход блока сравнения подключен ко входу блока управления, выход которого соединен со вторым управляющим входом формирователя псевдослучайных сигналов и с первым входом счетгшка, выходы которого подключены к информационным входам блока памяти, первый и второй выходы которого под1слючены соответственно к первому и второму входам декодера стаффкнговых интервалов, первый и второй выходы которого соединен соответственно с управляющими входами блока памяти и блока формирования тактовых импульсов, при этом выход блока задержки подключен ко вторым входам управляемого распределителя и счетчика, третий управляющий . ьход формирователя псевдослучайных сигналов соединен с третьим входом счетчика, четвертый вход которого соединен со вторым выходом блока сравнетш. Источники информации, принятые во внимание при экспертизе 1. Авторское свидетельство СССР № 510792, кл. И 04 J 3/00 (прототип). Вы X off

eI

Авторы

Даты

1981-08-30—Публикация

1979-03-28—Подача