ходами блока запуска и управления, а на приемной стороне введены блок приема участков псевдослучайных последовательностей, блок анализа фазы, блок коррекции программы приемной части, блок хранения программы прогноза приемной части и декодер служебной информации, причем первый выход блока запуска и управления приемной части соединен с первым входом блока анализа фазы, первым входом бло-°ка приема ; частков псевдослучайных последовательностей, первым управляющим входом блока коррекции программы приемной части, управляющим входом блока хранения программы прогноза приемной части и с первым управляющим входом декодера служебной информации, второй выход блока запуска и управления приемной части соединен с вторым входом блока анализа фазы, вторым входом блока приема участков псевдослучайных последе вательностей, вторым управляющим входом блока коррекции программы приемной части и вторым управляющим входом декодера служебной информации, вход блока запуска и управления приемной части соединвн с первым выходом блока приема участков

псевдослучайных последЬвательностей,.

touxojtij слуяебноЛ информации которог5 соединены с входами декодера служебной информации, информационный вход которого соединен с информационным выходом блока приема участков псевдослучайных последовательностей и с информационным входом блока анализа фазы, третий вход которого соединен с первым выходом декодера служебной информации, второй и третий выходы которого через блок коррекции программы приемной части соединены с входами блока хранения программы прогноза приемной части, первый, второй и третий выходы которого.соединены соответственно с первым, вторым и третьим входами декодера служебной информации и с первым, вторым и третьим входами блока коррекции программы приемной части, четвертый и пятый вход которого соединены соответственно- с четвертым и пятым выходами блока хранения программы прогноза приемной части, входы генератора тактовой частоты соединены с синхронизирующими выходами декодера служебной информации, четвертый выход koторого соединен с управляющим входом блока памяти приемной части, информсщионный вход которого соединен с выходом блока анализа фазы. .

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного ввода-вывода синхронной информации | 1979 |

|

SU862373A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1987 |

|

SU1649681A1 |

| МНОГОКАНАЛЬНАЯ ЦИФРОВАЯ СИСТЕМА ПЕРЕДАЧИ И ПРИЕМА ИНФОРМАЦИИ | 1990 |

|

RU2013012C1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2001 |

|

RU2185029C1 |

| РАДИОЛИНИЯ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2009 |

|

RU2411663C1 |

| СПОСОБ АДАПТИВНОЙ ПЕРЕДАЧИ ДАННЫХ В РАДИОЛИНИИ С ПСЕВДОСЛУЧАЙНОЙ ПЕРЕСТРОЙКОЙ РАБОЧЕЙ ЧАСТОТЫ | 2007 |

|

RU2356167C1 |

УСТРОЙСТВО АСИНХРОННОГО ВВОДА-ВЫВОДА СИНХРОННОЙ ИНФОРМАЦИИ, содержсццее на передающей стороне последовательно соединенные блок запуска и управления, управляемый распределитель, блок памяти и двоичнодесятичный преобразователь, причем третий выход блока запуска и управления соединен с управлякндим входом двоично-десятичного преобразователя и с управляющим входом блока памяти, а на приемной стороне блок запуска и управления приемной части, а также последовательно соединенные генератор тактовой частоты, управляемый распределитель приемной части и блок памяти приемной части, причем управляющий вход управляемого распределителя приемной части соединен с первым выходом блока запуска и управления приемной части, отличающ. е е с я тем, что, с целью повышения достоверности сопряжения по скорости двух последовательностей циф ровых сигналов,на передающей стороне введены блок определения количества элементов в цикле, блок хранения программы прогноза, блок определения отклонения от прогноза, блок коррекции программы, кодер служебной информации и блок формирования участков псевдослучайных последовательностей, причем первый выход блока запуска и управления соединен с первым управляющим входом блока определения количества элементов в цикле, второй выход блока запуска и управления соединен с первым входом блока формирования участков псевдослучайных последовательностей, с управляющим входом блока хранения программы прогноза, с первым входом блока коррекции nporpaiv и с вторым управляющим входом блока определения количества.элементов в цикле, выходы служебной информации которого через кодер служебной информации соединены с входами служебной информации блока .формирования участков псевдослучайных последовательностей, (О информационный вход которого соединен с выходом двоично-десятично.го преобразователя, первый выход блока; хранения программы прогноза соединен с первым входом блока определения отклонения от прогноза и с вторым входом блока коррекции программы, выходы которого соеди.нены с корректирующими входами блоел ка хранения программы прогноза, информационные выходы которого соесо со динены с программирукицими входами кодера служебной информации, синхронизируквдие входы которого соёдинёны с выходами блока памяти, второй и третий выходы блока хранения программы прогноза соединены соответственно с третьим и четвертым входами блока коррекции программы, пятый вход которого соединен с входом кодера служебной информации и с выходом блока определения отклонения от прогноза, второй вход которого соединен с выходом блока определения количества элементов в цикле, второй и третий входы блока формирования участков псевдослучайных последовательностей соединены, соответственно с третьим к четвертым вы

f

Изобретение относится к связи и может быть использовано в аппаратуре acuHxpoHHcSro ввода - вывода синКронной двоичной информации в цифровые тракты систем, основанных на импульсно-кодовой модуляции, дельтамодуляции и других цифровых методах модуляции.

Известно устройство асинхронного ввода-вывода двоичной информации в цифровом канале, содержащее на передающей стороне управляемый распределтель, блок памяти, фазовый йомпйратор, кодер фазы, датчик фазирующей кoмбинaцф, а на приемной стороне: коммутатор, блок фазирования по Иклам декодер фазы, блок фазовой автоподстррйки частоты, управляемый распределитель и блок памяти J.

Однако известное устройствоце- достаточно экономично с точки зрения использоваш к пропускной способности канала связи, и как следствие - не обеспечивает высокой достоверности сопряжения цифровых последовательностей.

Наиболее близким техническим решением к изобретению является устройство асинхронного ввода-вывода синхронной информации, содержащее на передающей стороне последовательно Соединенные блок запуска и управления, управляемый распределитель, блок памяти и двоично-десятичный преобразователь, причем треQ тий выход блока запуска и управления соединен с управляющим входом двоично-десятичного преобразователя и с управляющим входом блока памяти , а на приемной стороне блок запуска и управления приемной части, а также последовательно соединенные генератор тактовой частоты, управляемый распределитель приемной час- ти и йпок памяти приемной части, причем управляющий вход управляе0 мого распределителя приемной части соединен с первым выходом блока запуска и управления приемной части t 2 З..

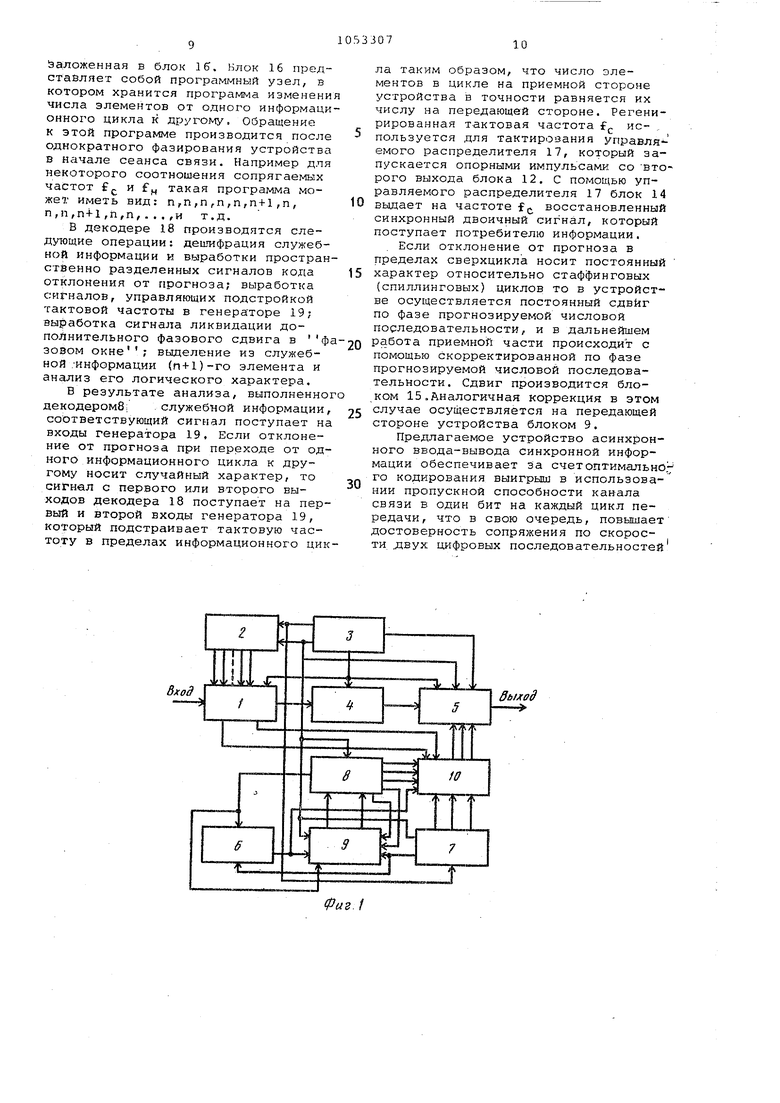

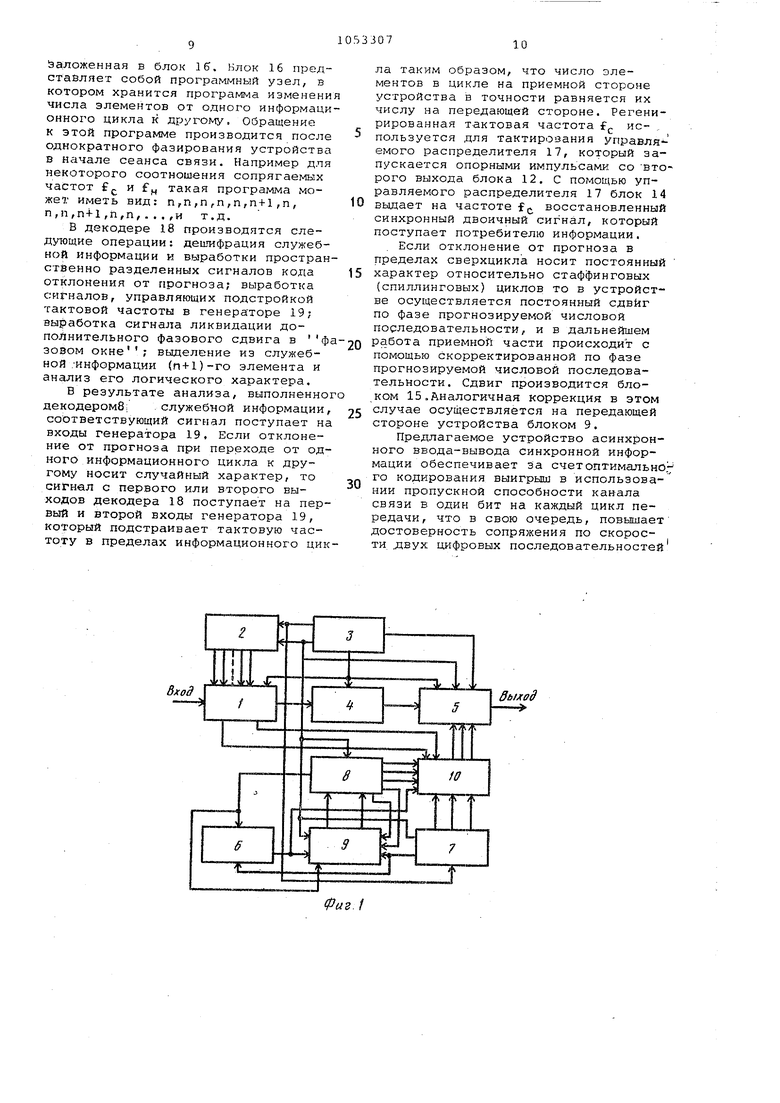

Недостатком известного устройст5 ,ва асинхронного ввода-вывода асинхронной информации является то, что . оно не; обеспечивает достаточной достоверности сопряжения цифровых последовательностей. Целью изобретения является повыше ние достоверности сопряжения по ско рости двух последова.тельностей цифровых сигналов. Поставленная цель достигается тем что в устройство асинхронного ввода вывода синхронной информации, содержащее на передающей стороне последовательно соединенные блок запуска и управления, управляемый рас пределитель, бло.к памяти и двоичнодесятичный преобразователь, причем третий выход блока запуска и управления соединен с управляющим входом двоично-десятичного преобразователя и с управляющим входом блока памяти, а на приемной стороне блок запуска и управления приемной части, а также последовательно соединенные генератор тактовой частоты управляемый распределитель приемной части и блок памяти приемной части, причем управляющий вход управляемого распределителя приемной части соединен с первым выходом блока зап ка и управления приемной части, на передающей стороне введены блок определения количества элементов в цикле, блок хранения программы прогноза, блок определения отклонения от прогноза, блок коррекции программы, кодер служебной информации и блок формирования участков псевдослучайных последовательностей причем первый выход блока запуска и управления соединен с первым упра ляющим входом блока определение количества элементов в цикле, второй выход блока запуска и управления соединен с первым входом блока формирования участков псевдослучайных последовательностей, с управляющим входом блока хранения программы про гноза, с первым входом блока коррек ции программы и со вторым управляющ входом блока определения количества элементов в цикле, выходы служеб ной информации которого через кодер служебной информации соединены с входами служебной информации блока формирования участков псевдослучайных .последовательностей, информационный вход которого :сЬединен с вы-; ходом двоично-десятичного преобразователя, первый выход блока(хранения программы прогноза соединен с первым входом блока определения отклонения от прогноза и с вторым входом блока коррекции программы, выходы которого соединены с корректирующими входами блока хранения программы прогноза, информационные выходы которого соединены с програм мирующими входами кодера служебной информации, синхронизирующие входы которого соединены с выходами олока памяти, второй и третий выходы бло,ка хранения программы прогноза соединены соответственно с третьим и четвертым входами блока коррекции программы, пятый вход которого соединен с входом кодера служебной информации и с выходом блока определения отклонения от прогноза, второй вход которого соединен с выходом блока определения количества элементов в цикле, второй и третий входы блока формирования участков псевдослучайных последовательностей соединены соответственно с третьим и четвертым выходами блока запуска и упрагления, а на приемной стороне введены блок приема участков псевдослучайнпх последова тельностей, блок анализа фазы, блок коррекции программы приемной части, блок хранения программ прогноза приемной части и декодер служебной информации, причем первый выход. блока запуска и управления приемной части соединен с первым входом блока анализа фазы, первым входом блока приема участков псевдослучайных последовательностей, первым управляющим входом блока коррекции программы приемной части, управляющим входом блока хранения программы прогноза приемной части и с первым управляющим входом декодера служебной информации, второй выход блока запуска и управления приемной части соединен с вторым входом блока анализа фазы, вторым входом блока приема участков в псевдослучайных последовательностей, вторым управляю-щим входом блока коррекции программы приемной части и вторым управляющим входом декодера служебной информации, вход блока запуска и yitравления приемной части соединен с первым выходом блока приема участков псевдослучайных последовательностей, выходы служебной информации которого соединены с входами декодера служебной информации, информационный вход которого соединен с информационным выходом блока приема участков псевдослучайных последовательностей и с информационным входом блока анализа фазы, третий вход которого соединен с первым выходом декодера служебной информации, второй и третий выходы которого через блок коррекции программы приемной части соединены с входами блока хранения программы прогноза приемной части, первый, второй и третий выходы которого соединё ны соответственно с первым, вторым и третьим входами декодера служебной информации и с первым,, вторым и третьим входами блока коррекции г.ро- граммы приемной части, четвертый и пятый входы которого соединены :.оответственно с четвертым, пятым выходами блока хранения программы прогноза приемной части, входы генератора тактовой частоты соединены с синхронизирующими выходами декодера служебной информации, четвертый выход которого соединен с уп равляющим входом блока памяти прием ной части, информационный вход кото рого соединен с выходом блока анализа фазы. На фиг Л приведена блок-схема Передающей части устройства асинхро ного ввода-вывода синхронной информации; на фиг,2 - то же, приемной ча-fи устройства асинхронного ввода-вывода синхронной информации. Устройство (фигЛ) содержит блок 1 памяти, управляемый распределител 2, блок 3 запуска и управления, двоично-десятичный преобразователь 4, блок 5 формирования / участков псевдослучайных последовательное тей, блок 6 определения отклонения от прогноза, блок 7 определения количества элементов в цикле, блок 8 хранения программы прогноза, блок 9 коррекции программы, кодер 1Q служе ной информации. Устройство (фиг.2) содержит приема участков псевдослучайных последовательностей, блок 12 запуска и управления приемной части, блок 13 анализа фазы, .блок 14 памяти приемной части, блок 15 коррекции .программы приемной части, блок 16 хранения программы прогноза приемной части, управляемый распределитель 17 приемной части, декодер 18служебной информации, генератор 19тактовой частоты. Устройство асинхронного ввЬда вы .вода синхронной информации работает следующим образом. Синхронный двоичный сигнал (СДС) следующий с тактовой частотой . по следовательно, по информационным ци лам, вводится в цифровой канал связи,-характеризуемый частотой- несу щей последовательности. Информацибнные циклы организуются на передаче с помощью опорных импульсов. Опо ные импульсы следуют с частотой /М, где N - число элементов в организуемом в канале цикле передачи. Начало работы устройства фиксируется на передаче моментом совпадения опорного ,и тактового импульсов в блоке 3. Это совпадение достигается в результате предварительного фазирования приемной и передающей частей устройства в начале сеанса авяз При заданном соотношении заданных частот и f количество и периодичность изменения числа элементов в информационном цикле, включаю щем в себя определенное количество тактовых импульсов между двумя -смеж ными опорными импульсами и равное м, п-1 или п+1 импульсов, программируется в блоке 8. Отклонение на единицу числа элементов в информационном цикле от nporpaMviHpyeMoft величины, происходящее вследствие относительной девиации частот и или вследствие постоянного фазового сдвига фактической и количественно прогнозируемой последовательностей, фиксируется блоком б. Для работы этого блока используется двоичная информация, поступающая из блока 7 и ИЗ блока 8. В предлагаемом устройстве прёДусмотрена коррекция программы в случае постоянного фазового сдвига фактической и количественно прогнозируемой последовательности. Фнкции коррекции выполняет блок 9 коррекции программы, .Цифровые сигналы с выхода блока 7, сигналы с выхода блока 8 и сигналы с выхода блока 6, поступающие на соответствующие входы кодера 10, обр-абатывалотся последниг/п-ь Задача кодера 10 заключается в том,, чтобы еализовать алгоритм работы перещающей части устройства, для чего им, кроме указанных сигналов, дополнительно использую,тся сигналы из п-й и {пт1)-й ячеек блока 1. На выходах кодера 10 имеют место управляющие сигналы, которые задают номер используемой для передачи ПСП и определяют наличие или отсутствие фазового сдвига в фазовом окне. Эти сигналы используются блоком 5, В результате сравнения сигналов в блоке б на выходе последнего формируется соответствующий сигнал, который направляется на вход кодера 10 и на вход блока 9. Для осуществления оперс1ции коррекции программы прогноза используется блок 9. В остальных случаях никаких сигналов коррекции не формируется. Сигналы коррекции прогЕ а у1мы из блока 9 поступают в блок 8. Опорными импульсами с третьего выхода блока 3 запускается управляемый распределитель 2, который представляет собой регистр сдвига с (п+1) входом,, После запуска управляемый распредлелитель 2 тактируется импульсами тактовой частоты f, поступающими с первого выхода блока 3, Тактовые импульсы на выходах управляемого распред елителя 2 служат импульсами записи СДС в блок 1. Синхронные двоичные сигналы, записанные в блок 1 на тактовой частоте f считываются оттуда быстрыми тактовыми импульсами (БТИ), поступающими с третьего выхода блока 3 и обрабатываются в двоично-десятичном преобразователе 4. Частота еледования БТИ в двоично-десятичном преобразователе 4 превышает канальную частоту fj не менее, чем в N ра Двоично-десятичный преобразователь осуществляет перевод информационного цикла длиной п элементов из двои ного кода в десятичный. Полученное число, выраженное в количестве ВТИр выхода двоично-десятичного преобраз вателя 4 направляется на информационный вход блока 5. Таким образом, под действием БТИ и в соответствии с сигналами с выхода двоично-десятичного преобразователя 4 в блоке 5 осуществляется соответствующий сдвиг той ПСП, кото |рая используется для организации ди ла Ттередачи. Считывание ПСП из блока 5 производится на несущей частоте f , канала связи. Импульсы частоты f, направляются в блок J5| со второго выхода блока 3. Длина N передаваемого в канал связи участка ПСП может выбираться с учетом необходимости защиты информации от однократных ошибок, если позволяет соотношение сопрягаемых частот и цифровых сигналов. Минимальная длина участка ПСП, исходя из условий распознавания ПСП на приеме, должна быть установлена равной (п+2) элементам для рассматриваемого устройства и равной(h+3) элементам-для прототи па. В то же время в канале связи имеет место непрерывная последовательность элементов. Поэтому осталь ные -{N-(г1+2)} или (N-(n + 3) элементов, направляемые в канал связи за время между двумя смежными опорными импульсами, в общем, случае мо гут быть как соответствующими элементам ПСП, так и служебными сигнал ми, по своей структуре и сути не связанными.с ПСП. Для повышения достоверности сопряжения цифровых последовательностей указанные оставши ся элементы целесообразно рассматри вать в качестве элементов, являющихся продолжением соответствующего участка ПСП длиной (п+2). Тогда разность N-(n+2)j или {N-(n+3) элементов представляет собой избыточность, используемую на приеме при распознавании участков ПСП. На приемной стороне ПСП поступает на первый вход блока 11. Сигнал, свидетельствующий о номере принятой ПСП, поступает в декодер 18. При принятому и распознанному в начале сеанса связи участку ПСП, с помощью которого закодирована спе циальная служебная кодовая комбинация осуществляется однократное начальное фазирование опорных импульсов приемно и передающей сторон устройства. Пос ле этого начинает работу блок 12. Последний вырабатывает опорные импульсы и быстрые тактовые импульсы, используемые в дальнейшем в работе приемной части устройства. С приходом участка ПСП,несущего полезную информацию, блок 1 распознает и устанавливает номер ПСП, использованной для передачи. Информация об абсолютном значении фазы принятого участка ПСП со второго выхода блока 1 1 поступает на первый вход блока 13. Блок 13 переводит абсолютный фазовый сдвиг в двоичную кодовую комбинацию, устраняя при этом фазовое окно. Полученная на выходе блока 13 анализа фазы двоичная кодовая комбинация имеет длину h и повторяет характер ti информационных элементов на передаче. Полученный в двоичном коде информационный цикл, длина которого равна п, с выхода блока 13 переписывается на частоте БТИ в блок 14, поступая на его первый вход. Единичный.сигнал с выходадекодера 18 служебной информации поступает на вход блока 14 только в том случае, когда характер (п-Ц)-го элемента информационного цикла.на передаче был единичным. Если же характер (п + 1)-го элемента информационного цикла на передаче был нулевым, то единичный сигналс выхода. декодера 18 служебной информации па вход блока 14 не поступает, т.е. он остается в исходном нулевом состоянии. Считывание информации информациом- ного цикла потребителю из блока 14 памяти осуществляется на регенерированной тактовой частоте . В обоих случаях благодаря перестройке генератора 19 в пределах между двумя соседними опорными импульсами, он выдаст (n+l) тактовых импульсов частоты g и все (n+l) элементов, записанных в ячейках регистра блока-14, будут считаны потребителю на частоте f. В случае, если в информационном цикле на передаче было п .элементов, то из ячеек регистра, будут считаны только п элементов (со второй ячейки по (п+1)-ую), так как с генератора 19 поступит только п тактов частоты f. . При спиллинговых информационных циклах генератор 19 выдаст (п-1) тактов частоты f и потребителю поступит (п-1) элементов информационного цикла, которые будут считаны из ячеек регистра (с третьей ячейки по (п+1)-ую) . Для получения тактовой частоты fc в устройстве используется управляемый распределитель 17, генератор 19, декодер 18 и блок 16.При регенерации тактовой частоты используется программа прогнозируемого числа элементов в информационном цикле. Заложенная в блок 16, Ьлок 16 представляет собой программный узел, в котором хранится программа изменени числа элементов от одного информаци онного цикла к другому. Обращение к этой программе производится после однократного фазирования устройства в начале сеанса связи. Например для некоторого соотношения сопрягаемых частот f- и такая программа может иметь вид: n,n,n,n,n,n+l,n, п ,п ,n+l,n,n,...,и т.д. В декодере 18 производятся следующие операции: дешифрация служебной информации к выработки простран ственно разделенных сигналов кода отклонения от прогноза; выработка сигналов, управляющих подстройкой тактовой частоты в генераторе 19; выработка сигнала ликвидации дополнительного фазового сдвига в ф зовом окне; выделение из служебной ,информации (п+1)-го элемента и анализ его логического характера. В результате анализа, выполненно декодеромб; .служебной информации соответствующий сигнал поступает на входы генератора 19, Если отклонение от прогноза при переходе от одного информационного цикла к другому носит случайный характер, то сигнал с первого или второго выходов декодера 18 поступает на первый и второй входы генератора 19, который подстраивает тактовую частоту в пределах информационного цик

Sjfffff

Выход ла таким образом, что число элементов в цикле на приемной стороне устройства в точности равняется их числу на передающей стороне. Регенирированная тактовая частота ис- , пользуется для тактирования управляемого распределителя 17, который запускается опорными импульсами со второго выхода блока 12. С помощью управляемого распределителя 17 блок 14 выдает на частоте f восстановленный синхронный двоичный сигнал, который поступает потребителю информации. Если отклонение от прогноза в пределах сверхцикла носит постоянный характер относительно стаффинговых (спиллинговых) циклов то в устройстве осуществляется постоянный сдвиг по фазе прогнозируемой числовой последовательности, и в дальнейшем работа приемной части происходит с помощью скорректированной по фазе прогнозируемой числовой последовательности. Сдвиг производится блоком 15.Аналогичная коррекция в этом случае осуществляется на передающей стороне устройства блоком 9. Предлагаемое устройство асинхрон ного ввода-вывода синхронной информации обеспечивает за счет оптимально. го кодирования выигрыш в использова- НИИ пропускной способности канала связи в один бит на каждый цикл передачи, что в свою очередь, повышает достоверность сопряжения по скорости двух цифровых последовательностей

| Печь для непрерывного получения сернистого натрия | 1921 |

|

SU1A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Аппарат для очищения воды при помощи химических реактивов | 1917 |

|

SU2A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1979 |

|

SU862373A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1983-11-07—Публикация

1982-06-23—Подача