Изобретение относится к электросвязи и может быть использовано при вводе-выводе синхронных двоичных сигналов в цифровые тракты систем с дельта-модуляцией и импульсно-кодовой модуляцией.

Целью изобретения является повышение пропускной способности тракта передачи.

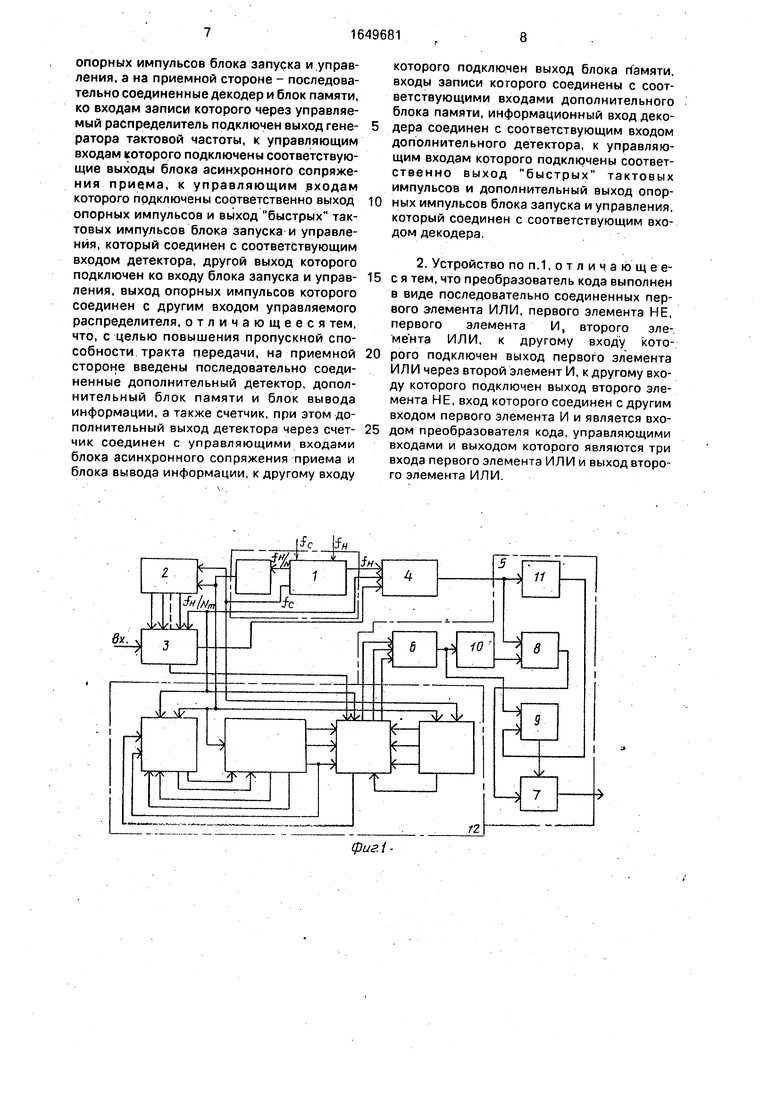

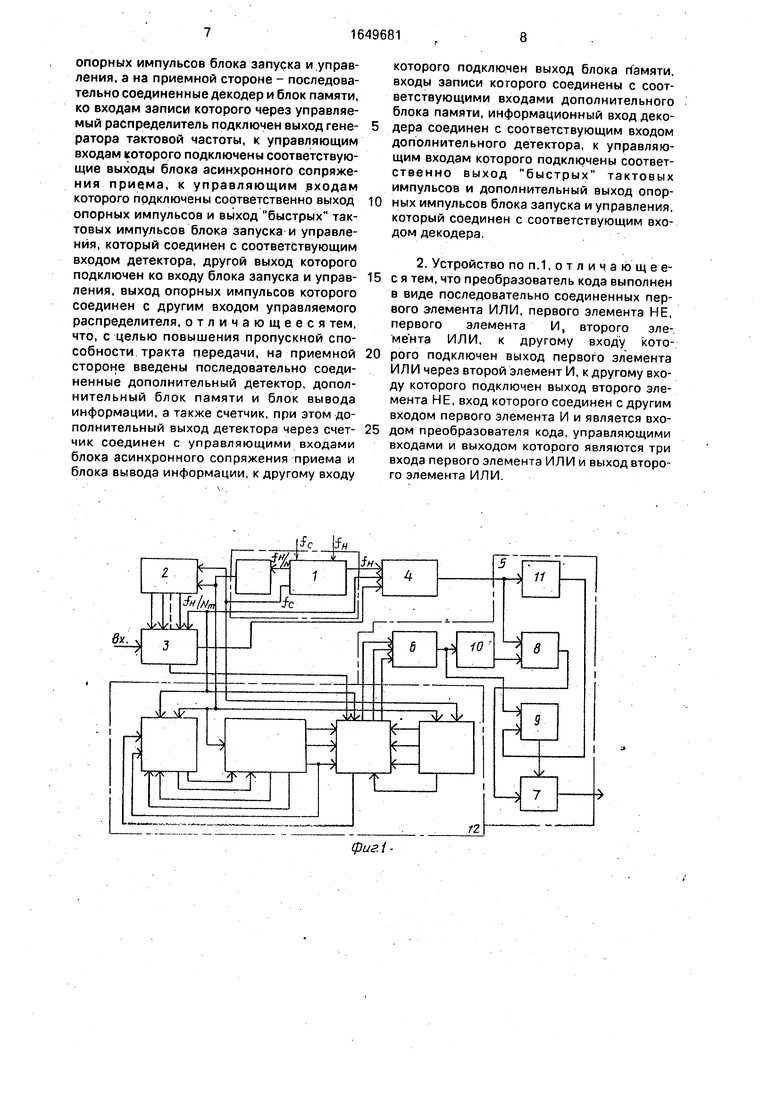

На фиг. 1 и 2 представлены структурные электрические схемы устройства асинхронного сопряжения цифровых сигналов на передающей и приемной сторонах.

Устройство асинхронного сопряжения цифровых сигналов содержит на передающей стороне блок запуска и управления (БЗУ) 1, управляемый распределитель 2, блок памяти 3, кодер 4, преобразователь 5 кода, в состав которого входят первый и второй элементы ИЛИ 6 и 7 первый и второй

элементы И 8 и 9 и первый и второй элементы НЕ 10 и 11, а также блок асинхронного сопряжения передачи (АСП) 12, а на приемной стороне -детектор 13, дополнительный детектор 14, первый и второй блоки памяти 15 и 16, управляемый распределитель 17, генератор 18 тактовой частоты, блок запуска и управления 19, блок асинхронного сопряжения приема 20, счетчик 21 и блок вывода 22 информации

Сущность изобретения состоит в исключении канала согласования скоростей, т.е. в исключении в каждом цикле передачи единичных интервалов служебной информации о согласовании скоростей,

Информацию о согласовании скоростей (в прототипе и данном устройстве это информация об отклонении числа единичных интервалов полезной информации в цикле

О Јь Ч) О

со

передачи от прогнозируемого числа) передают путем комбинированного кодирования полезной информации цикла передачи с защитой от ошибок заданной кратности. На передающей стороне устройства в блоке запуска и управления 1 формируют цикловые опорные импульсы с частотой следования fH/fnN. Другими словами организуют так называемые гиперциклы, существенно превышающие по длине используемые в прототипе сверхциклы и содержащие в своем составе m циклов передачи (величина m зависит от взаимной нестабильности сопрягаемых частот и на практике -.100), т.е. циклы такой максимальной длины M m N, при которой влияние нестабильности сопрягаемых частот не приводит к сбоям числа интервалов полезной информации в них по сравнению с прототипом. В циклах передачи (длиной N элементов) полезную информацию кодируют с защитой от ошибок заданной кратности. При этом, если в гиперцикле число единичных интервалов полез- ной информации не отличается от прогнозируемого, то передающая сторона устройства выдает в циклах передачи разрешенные комбинации выбранного кода. Если же это число отличается от прогнозируемого, то на выходе передающей стороны устройства в каждом цикле передачи формируются комбинации, инверсные разрешенным (запрещенные комбинации). При этом сам переход к кодированию комбинации того или иного типа является служебной информацией о согласовании скоростей. На приемной стороне устройства декодируют разрешенные или запрещенные комбинации циклов передачи каждого гиперцикла. При декодировании восстанавливают также исходную информацию. При этом в одной из параллельных ветвей восстанавливается информация в случае кодирования разрешенными комбинациями, в другой - в случае кодирования запрещенными комбинациями. На регенерированной частоте осуществляют вывод информации, декодированной в той ветви, где было обнаружено меньше ошибок.

Устройство асинхронного сопряжения цифровых сигналов работает следующим образом.

Синхронный двоичный сигнал, следующий с тактовой частотой fc, вводится в цифровой канал связи, характеризуемый частотой fn несущей последовательности. Начало работы устройства фиксируется на передаче моментом совпадения тактового импульса частоты fH/N, где N -длина цикла передачи, в блоке запуска и управления 1, на одном из выходов которого формируются

опорные импульсы с частотой следования fH/m N в соответствии с заданной длиной М N m гиперцикла.

После включения устройства блок ДСП

12 обнуляется и затем начинает работу по первому опорному импульсу частоты fH/mN. Это обеспечивает работу устройства, начиная с первого информационного цикла каждого сверхцикла. Счет последую0 щих информационных циклов в пределах каждого сверхцикла осуществляется по опорным импульсам.

Фактическое число элементов в информационном цикле может отличаться от про5 гнозируемого вследствие относительной девиации частот fc и тн или вследствие постоянного фазового сдвига фактической и прогнозируемой последовательностей. В соответствии с информацией об отклонении

0 числа элементов в информационном цикле от прогнозируемого блок АСП 12 выдает единичный сигнал по одному из трех выходов, подключенных ко входам элемента ИЛИ-6 преобразователя 5 кода. При этом по

5 двум другим выходам выдаются нулевые сигналы. Сигналы на указанных выходах блока АСП 12 несут одну из следующих команд: вычесть один элемент из прогнозируемого количества элементов в

0 информационном цикле; прибавить один элемент (логический/юль) к прогнозируемому количеству элементов в информационном цикле; прибавить один элемент (логическую единицу) к прогнозируемому

5 количеству элементов в информационном цикле,

Эти команды объединяются через элемент ИЛИ 6, на выходе которого появляется единичный сигнал в любом случае отклоне0 ния числа единичных информационных интервалов полезной информации в информационном цикле от прогнозируемого числа.

Опорными импульсами с выхода блока

5 запуска и управления 1 запускается управляемый распределитель 2, который тактируется импульсами тактовой частоты fc. С помощью управляемого распределителя 2 осуществляется запись информации в блок

0 памяти 3, имеющий (п + 1) ячеек. Информационная часть цикла передачи (длина цикла передачи N (п + 1)/ m элементов) считывается из блока памяти З в кодер 4 быстрыми тактовыми импульсами (БТИ), формируемы5 ми в блоке запуска и управления 1. При этом частота их следования превышает канальную частоту тн не менее, чем в 2 N + s раз, где S - избыточность, необходимая для кодирования информации циклов передачи с защитой от ошибок заданной кратности К. Под

ействием БТИ в кодере 4 формируются омбинации псевдослучайной последоваельности (ПСП), соответствующие инфорации цикла передачи, длина которого N лементов, и имеющие избыточность S, небходимую для кодирования информации с защитой от ошибок заданной кратности К.

С выхода кодера 4 на несущей частоте H комбинации поступают на входы первого элемента И 8 и второго элемента НЕ 11 преобразователя 5 кода, с выхода элемента НЕ 11 инвертированные комбинации поступают на вход второго элемента И 9. Сигналы на выходе передающей части устройства появляются на выходе элемента ИЛИ 7, объединяющего сигналы либо с выхода элемента И 8, либо с выхода элемента И 9 в зависимости от наличия сигнала на других входах элементов И 8 и 9. Сигналы на этих входах (сигналы об отклонении числа информационных интервалов от прогнозируемого) взаимообратны и представляют собой прямые и инвертированные элементы НЕ 10 сигналы с выхода элемента ИЛИ 6. В результате на выходе устройства формируются разрешенные или запрещенные комбинации в циклах передачи каждого гиперцикла в зависимости от того имеется отклонение действительного числа интервалов в информационном цикле от прогнозируемого числа или нет.

На приемной стороне устройства комбинации ПСП параллельно обрабатываются в декодерах 13 и 14. Перед началом сеанса связи на передающей стороне формируется служебная кодовая комбинация - участок ПСП длиной N + S элементов (соответствующая информационной комбинации, состоящей из нулей, поступающих из обнуленного блока памяти 3). По этому участку ПСП, принятому декодером 13, в блоке запуска и управления 19 осуществляется однократное за сеанс связи начальное фазирование опорных импульсов приемной и предающей сторон устройства, позволяющее осуществить прогнозирование и на приеме и на передаче син- фазно. После этого блок запуска и правления 19 начинает формировать им- пульсы частоты fH/N и быстрые тактовые мпульсы. В декодерах 13 и 14 происходит екодирование с обнаружением и исправлением ошибок заданной кратности К как для случая кодирования информации разрешенными комбинациями, так и для случая кодирования запрещенными комбинациями.

Сигналы наличия несовпадений (ошибок) поступают с выхода декодера 13 на вход счетчика 21, в котором происходит подсчитывание числа циклов передачи с ошибками в гиперцикле при декодировании разрешенных комбинаций. Если это число

равно (т/2 + 1) , то на выходе счетчика 21 формируема единичный сигнал, который служит в дальнейшем указанием на то, что истинной будет информация, восстановленная в другой ветви, т.е. в декодере 14.

Информация циклов передачи, восстановленная при прямом и обратном декодировании с выходов декодеров 13 и 14 записываются в блоки памяти 15 и 16. Счи0 тывание информации с того или иного блока памяти (15 и 16) осуществляется на регенерированной тактовойчастоте в зависимости от наличия сигнала на выходе счетчика 21, который поступает на управляющий вход

5 блока вывода 22 информации, на другие входы которого поступает считываемая информация из блоков памяти 15 и 16.

Номинальное значение частоты генератора 18 тактовой частоты соответствует слу0 чаю, когда в информационном цикле содержится п элементов. В случае, когда в информационном цикле фактически содержится (п + 1) или (п - 1) элементов блок асинхронного сопряжения приема 20 фор5 мирует сигнал на соответствующее увеличение или уменьшение тактовой частоты относительно ее номинального значения.

Управляемый распределитель 17 запускается опорными импульсами с выхода

0 блока запуска и управления 19, а тактируется регенерированной тактовой частотой, поступающей с выхода генератора 18 тактовой частоты. С помощью управляемого распределителя 17 из блоков памяти 15 и 16 через

5 блок вывода 22 информации происходит считывание восстановленного синхронного двоичного сигнала.

Формула изобретения

1. Устройство асинхронного сопряже0 ния цифровых сигналов, содержащее на пе- редающей стороне последовательно соединенные управляемый распределитель, блок памяти, кодер и преобразователь кода, к управляющим входам которого под5 ключены выходы команд управления блока асинхронного сопряжения передачи, ко входам которого подключены соответственно другой выход блока памяти и выходы сигнала тактовой частоты, опорных импульсов и

0 быстрых тактовых импульсов блока запуска и управления, выход сигнала канальной частоты которого соединен с первым управляющим входом кодера, ко второму управляющему входу которого подключен выход

5 быстрых тактовых импульсов блока запуска и управления,который соединен с соответствующим входом блока памяти, а к управляющим входам управляемого распределителя подключены соответственно выход сигнала тактовой частоты и выход

опорных импульсов блока запуска и управления, а на приемной стороне - последовательно соединенные декодер и блок памяти, ко входам записи которого через управляемый распределитель подключен выход генератора тактовой частоты, к управляющим входам которого подключены соответствующие выходы блока асинхронного сопряжения приема, к управляющим входам которого подключены соответственно выход опорных импульсов и выход быстрых тактовых импульсов блока запуска и управления, который соединен с соответствующим входом детектора, другой выход которого подключен ко входу блока запуска и управления, выход опорных импульсов которого соединен с другим входом управляемого распределителя, отличающееся тем, что, с целью повышения пропускной способности тракта передачи, на приемной стороне введены последовательно соединенные дополнительный детектор, дополнительный блок памяти и блок вывода информации, а также счетчик, при этом дополнительный выход детектора через счетчик соединен с управляющими входами блока асинхронного сопряжения приема и блока вывода информации, к другому входу

0

которого подключен выход блока Памяти, входы записи которого соединены с соответствующими входами дополнительного блока памяти, информационный вход декодера соединен с соответствующим входом дополнительного детектора, к управляющим входам которого подключены соответственно выход быстрых тактовых импульсов и дополнительный выход опорных импульсов блока запуска и управления, который соединен с соответствующим входом декодера.

2. Устройство поп.1,отличающее- с я тем, что преобразователь кода выполнен в виде последовательно соединенных первого элемента ИЛИ, первого элемента НЕ, первого элемента И, второго элемента ИЛИ, к другому входу кото- рого подключен выход первого элемента ИЛИ через второй элемент И, к другому входу которого подключен выход второго элемента НЕ, вход которого соединен с другим входом первого элемента И и является вхо- дом преобразователя кода, управляющими входами и выходом которого являются три входа первого элемента ИЛИ и выход второго элемента ИЛИ.

| название | год | авторы | номер документа |

|---|---|---|---|

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1978 |

|

SU786024A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1982 |

|

SU1053307A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1983 |

|

SU1111257A1 |

| Устройство асинхронного сопряжения цифровых сигналов | 1979 |

|

SU860326A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1986 |

|

SU1401629A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1982 |

|

SU1072278A1 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1987 |

|

SU1552388A2 |

| Устройство асинхронного сопряжения синхронных двоичных сигналов | 1974 |

|

SU510792A1 |

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Устройство асинхронного ввода-вывода синхронной информации | 1979 |

|

SU862373A1 |

Изобретение относится к электросвязи. Цель изобретения - повышение пропускной способности тракта передачи. Устройство асинхронного сопряжения цифровых сигналов содержит на передающей стороне блок запуска и управления, управляемый распределитель блок памяти, кодер, преобразователь кода и блок асинхронного сопряжения передачи, а на приемной стороне дв-а детектора, два блока памяти, управляемый распределитель, генератор тактовой частоты, блок запуска и управления, блок асинхронного сопряжения приема, счетчик и блок вывода информации Цель достигается путем исключения канала согласования скоростей, т.е. исключения в каждом цикле передачи единичных интервалов служебной информации о согласовании скоростей. Устройство также отличается выполнением преобразователя кода, состоящего из двух элементов ИЛИ, двух элементов И и двух элементов НЕ 1 з п. ф-лы, 2 ил.

N

3

&

| Устройство ввода-вывода синхронной двоичной информации в цифровые тракты | 1984 |

|

SU1374438A1 |

| Очаг для массовой варки пищи, выпечки хлеба и кипячения воды | 1921 |

|

SU4A1 |

Авторы

Даты

1991-05-15—Публикация

1987-12-02—Подача