Изобретение относится к технике передачи данных и может использоваться в системах с решающей обратной связью для приема информации, закодированной шклическим кодом допускающим мажоритарную процедуру декодирования. Известен декодер с обнаружением и испра лением ошибок, содержащий последовательно соединенные первый элемент ИЛИ, регистр сдвига, первый ключ и вычислитель синдрома а также сумматор по модулю два, счетчик сдвигов, счетчик исправлений, второй, третий, четвертый, пятый, щестой и седьмой ключи, при этом выходы регистра сдвига через сумматоры подключены к входам мажоритарного элемента, выход которого через второй ключ подсоединен к сигнальному входу третьего ключа, к управляющему входу которого и управляюидам входам первого и четвертого ключей подсоединены первый выход счетчика сдвигов, второй и третий выходы которого подключе1п 1 соответственно к управляющим входам пятого и щестого ключей, причем выход первого ключа соединен с сип1альным входом пятого ключа 1. Одаако известный декодер имеет недостаточную помехоустойчивость и точность. Цель изобретения - повышение помехоустойчивости и точности декодирования. Для этого в декодер с обнаружением и исправлением ошибок, содержащий последовательно соединен1П 1е первый элемент ИЛИ, регистр сдвига, первый ключ и вычислитель синдрома, а также сумматор по модулю два, счетчик сдвигов, счетчик исправлений, второй, третий, четвертый, пятый, щестой и седьмой ключи, при этом выходы регистра сдвига через сумматоры подключены к входам мажоритарного элемента, выход которого через второй ключ подсоединен к сигнальному входу третьего ключа, к управляющему входу которого и управляющим входам первого и четвертого ключей подсоединен первый выход счетчика сдвигов, второй и третий выходы которого подклю1чены соответстве1то к управляющим входам пятого и щестого ключей, причем выход первого ключа соединен с сигнальным входом пятого ключа, введены последовательно соединертые блок дискретного интегрирования, счетчик недостоверных символов и второй элемент ИЛИ, а также буферный регистр сдвига, восьмой и девятый ключи, при этом второй выход счетчика недостоверных символов подключен к управляющим входам второго, седьмого и восьмого . ключей, а выход блока дискретного .интегрирования через девятый ключ подсоедштен к первому входу первого элемента ИЛИ, к второгугу входу которого через восьмой ключ подсоединен выход регистра сдвига, а к третьему входу первого элемента ИЛИ и первому входу сумматора по модулю два подключен выход третьего ключа, при этом выход, регистра сдвига через последовательно соед1тешп 1е седьмой и четвертый ключи подсоединен к второму входу сумматора по модулю два, выход которого через счет-чик исправлений подключен к одному из входов второго элемента ИЛИ, к другим входам которого подключены выходы вмчист-1тсля снидрома, а выход второго элемента ИЛИ подключен к сигнальному входу шестого ключа, выход которого подключен к первому входу буферного регистра сдвига, к второму входу которого подключен выход пятого ключа, причем первый выход счетчика сдвигов подключен к управляющему входу девятого ключа.

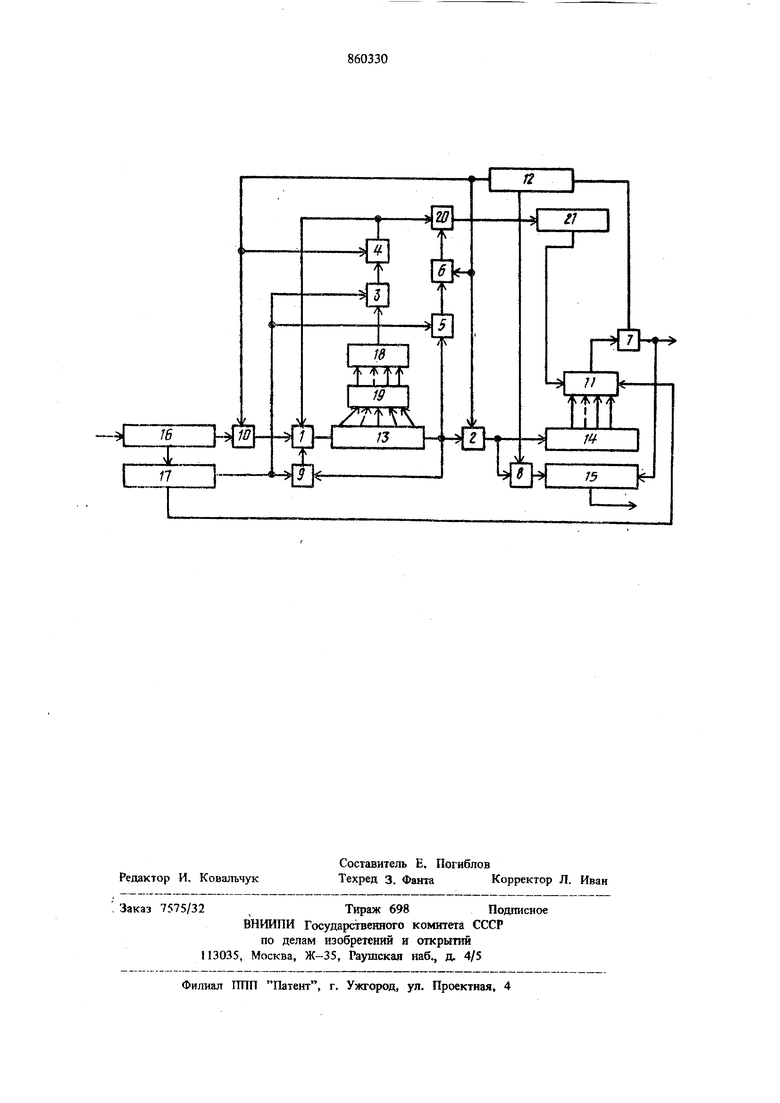

На чертеже представлена структурная электрическая схема предлагаемого декодера.

Устройство содержит первый элемент ИЛИ 1, первый ключ 2, второй ключ 3, третий ключ 4, четвертый ключ 5, пятый ключ 6, шестой ключ 7,, седьмой ключ 8, восьмой клточ 9, девятый ключ 10, второй элемент ИЛИ II, счетчик 12 сдвигов, регистр 13 сдвига, вычислитель 14 С1шдрома, буферный регистр 15 сдвига, блок 16 дискретного интегрирования, счетчик 17 недостоверных символов, мажоритарный элемент 18, сумматоры 19, сумматор 20 по модулю два, и счетчик 21 исправлений.

Декодер работает следующим образом. На вход блока 16 дискретного интегрирования поступают элементы кодового слова, при этом каждый принимаемый кодовый элемент стробируется в точках, количество которых выбирается равным нечетному числу, причем г fe + 2 m, где b характеризует зону неопределенности блока дискретного тгтегрировашш.

Сигнал о недостоверно принятом элементе кодового слова вырабатывается, если число импульсов стробирования tT находится в предлах Ул -6 rf-S vn+b-i Число недостоверных кодовых элементов на длине п кодового слова определяется счетчиком 17. С выхода

процесс исправления ошибок в соответствии с процедурой мажоритарного декодирования циклического кода. При этом ключи 3 и 5 открыты сигналом со счетчика 17, ключи 4

и 6 открыты после приема п элементов, ключи 10 и 2 закрыты на время исправления, равное п тактам, а ключ 9 закрыт. Если в процессе исправления ошибок в кодовом слове счетчик 21 исправлений зарегистрирует число

исправлений, не превышающее t, то элементы кодового слова, записанные через ключи 3, 4 и элемент ИЛИ I в регистр 13 сдвига, поступают через открытые ключи 2 и 8 в вычислитель 14 синдрома и буферный регистр 15, причем ключ 8 открывается на К тактов, а ключ 2 на п тактов.

Если при вычислении синдрома его вес оказался нулевым, то сигналом с выхода ключа 7 разрегиается вывод информации из буферного регистра 15, а в случае не нулевого веса синдрома вырабатывается сигнал ошибка, который поступает на выход ключа 7 и одновременно запрещает вывод информации с буферного регистра 15 сдвига.

Если число исправлений, зарегистрируемое

счетчиком 21, превышает t, то независимо от результата вычисления синдрома сигнал Ошибка поступает на выход ключа 7 и запрещает вывод информации из буферного регистра 15.

Если счетчик 17 недостоверных символов зарегистрировал число недостоверно принятых элементов на длине п кодового слова, превышающее t, то сигналом с второго выхода счетчика 17 открывается ключ 9, закрываются ключи 3 и 5, запрещается процесс неисправления ошибок в кодовом слове, записанные в регистр 13 элементы переписываются на его вход через ключ 9 и элемент ИЛИ I. При этом независимо от результата вычислеHirii синдрома на выход ключа 7 поступает сигнал Ошибка с другого выхода счетчика 17 недостоверных символов через элемент ИЛИ П и ключ 7, запрещая выдачу информации потребителю. Изменяя первый порог (второй выход счетчика 17) от О до t, второй порог (пер&ый выход счетчика 17) от t до п и ширину в зоны неопредепенности от 1 до 6 можно изменять скорость передачи блока 16 элементы кодового слова поступают в регистр 13 сдвига через ключ 10, открытый сигналом, поступающим со счетчика 12 сдвигов, и элемент ИЛИ 1. При записи элементов кодового слова в регистр 13 сдвига ключа 4 и 6 закрыты сигналом со счетчика 12 сдвигов. Если число недостоверно принятых элементов кодового слова не превышает k (число ошибок, исправляемых кодом), то начинается 5 информации и noMexoycToiTfflBocTb декодера в зависимости от качества канала. Таким образом, при обнарзокешш числа не достоверио принятых элементов в кодовом сл(же, превышающего t , процесс неисправления ошибок запрещается, а на выходе декодера появляется сигнал Ошибка, в результате чего уменьшается вероятность раз- множения ошибок в процессе мажоритарного декодирования циклического кода, повышается помехоустойчивость декодера. Использование новых злгментбв (схемы ди скретного интегрирования, счетчика недостовер ных символов, второго элемента ИЛИ с входами, буферного регистра сдвига, восьмого и девятого ключей) выгодно отличает предлагаемый декодер с обнаружением и исправлением ошибок от известного, так как повышается точность исправления ошибок (декоди рования) и увеличивается помехоустойчивость приема дискретной информации. Это достигается тем, что при числе ошибок, превышаюшем t, осуществляется запрет на исправление ошибок и вырабатывается сигнал ошибка независимо от результата вычисления синдрома. Применение предлагаемого декодера в системах с решающей обратной связью позволяет более эффективно использовать корректирующие свойства кодов, допускающих мажори тарную процедуру декодирования. Формула изобретения Декодер с обнаружением и исправлением ошибок, содержащий последовательно соединен ные первый элемент ИЛИ, регистр сдвига, пер вый ключ и вычислитель синдрома, а также сумматор по модулю два, счетчик сдвигов, счетчик исправлений, второй, третий, четверты пятый, щестой и седьмой ключи, при этом в ходы регистра сдвига через сумматоры подключены к входам мажоритарного элемента, выход которого через второй ключ подсоеди0нен к сигнальному входу третьего ключа, к управляющему входу которого и управляющим входам первого и четвертого ключей подсоединен первьш выход счетчика сдвигов, второй и третий выходы которого подключены соответственно к управляющим входам пятого и шестого ключей, причем выход первого ключа соединен с сигеальным входом пятого ключа, отличающийся тем, что, с целью повышения помехоустойчивости и точности декодирования, введены последовательно соединенные блок дискретного интегрирования, счетчик недостоверных символов и второй элемент ИЛИ, а также буферный регистр сдвига, восьмой и девятый ключи, при этом второй выход счетчика недостоверных символов подключен к управляющим входам второго, седьмого и восьмого ключей, а выход блока дискретного интегрирования через девятый ключ подсоед шен к первому входу первого элемента ИЛИ, к второму входу которого через восьмой ключ подсоединен выход регистра, а к третьему входу первого элемента ИЛИ и первому входу сумматора по модулю два подключен выход третьего ключа, при этом выход регистра сдвига через последовательно соед}шеныне седьмой и четвертый ключи подсоединен к второму входу сумматора по модулю два, выход которого через счетчик исправлений подключен к одному из входов второго элемента ИЛИ, к другим входам которого подключены выходы вычислителя синдрома, а выход второго элемента ИЛИ подключен к сигнальному входу шестого ключа, вь1ход которого подключен к первому входу буферного регистра сдвига, к второму входу которого подключен выход пятого ключа, причем первый выход счетчика сдвигов подключен к управляющему входу девятого ключа. Источники информащш, принятые во внимание при экспертизе 1. Авторское свидетельство СССР IP 563717, кл, Н 03 К 13/32, 1975 (прототип).

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство декодирования произведений кодов Рида-Соломона | 2017 |

|

RU2677372C1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Асинхронное устройство для исправления ошибок | 1973 |

|

SU633149A1 |

| Устройство обнаружения и исправления ошибок в кодах Рида-Соломона | 1986 |

|

SU1381719A1 |

| Декодер | 1975 |

|

SU563717A1 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Устройство мажоритарного декодирования кода Рида-Соломона по k-элементным участкам кодовой комбинации с порогом определения неисправляемой ошибки | 2015 |

|

RU2610684C1 |

Авторы

Даты

1981-08-30—Публикация

1979-10-09—Подача