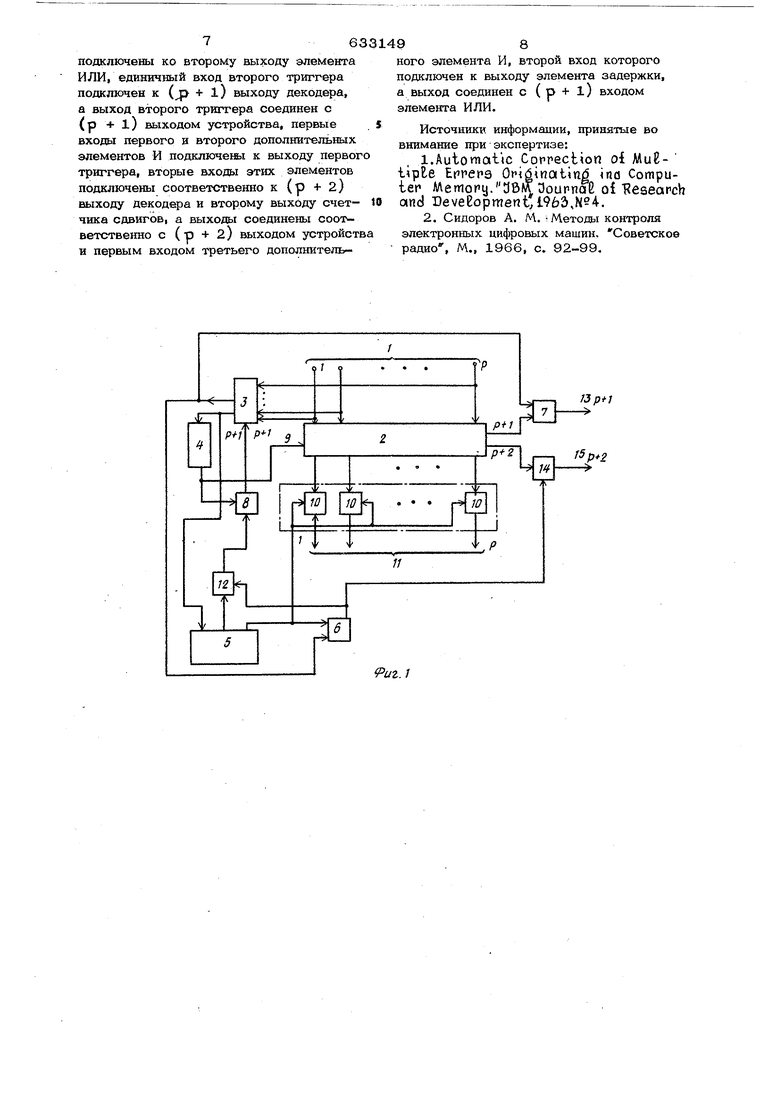

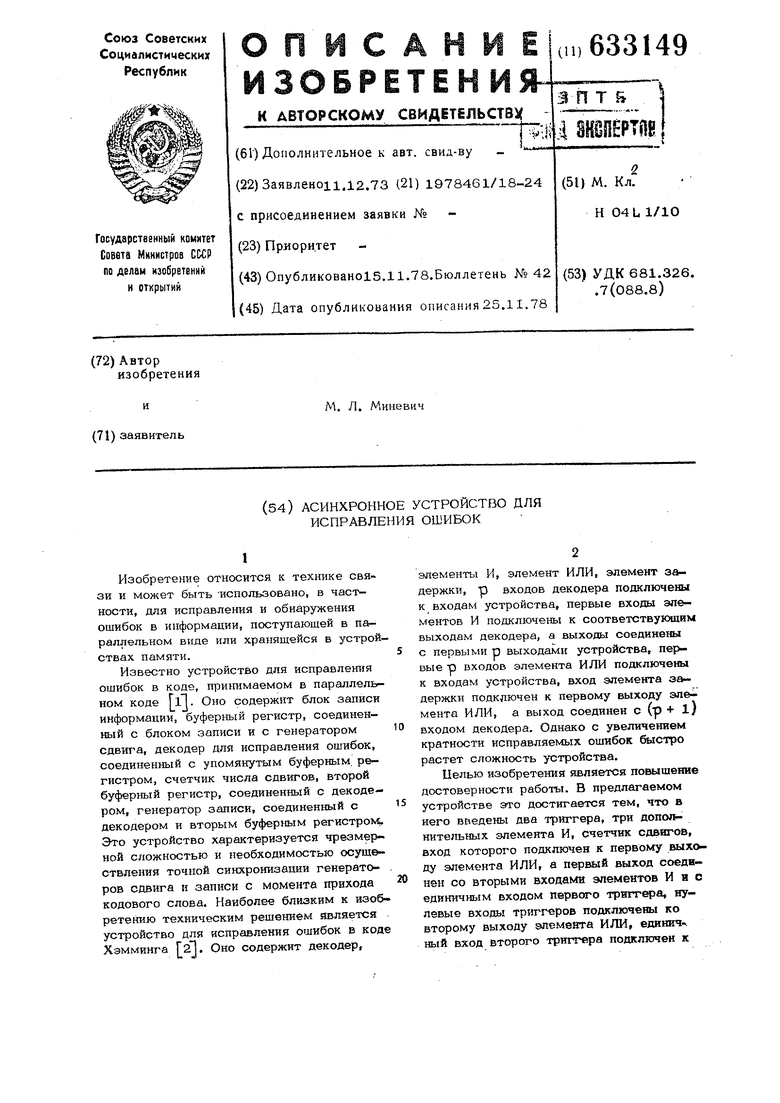

(р + 1 ) выходу декодера, а выход вто рого триггера соединен с (р 4-1 ) выходом устройства, первые входы первого и второго дополнительных элементов И подключены к выходу первого триггера, вторые входы этих элементов подключены соответственно к ( р + 2) выходу декодера и второму выходу счетчика сдвигов, а выходы соединены соответственно с ( р + 2) выходом устройства и первым входом третьего дополнительного элемента И, второй вход которого подключен к выходу элемента задержки, а выход соединен с (р + l) входом элемента ИЛИ, Предлагаемое устройство можно испол зовать как для исправления, так и для обнаружения ошибок в асинхронном режиме 1ри приеме информации в параллельном коде, если она закодирована любым корректирующим кодом. Переход от испра ления к обнаружению ошибок бывает необ ходим в том Случае, когда характер помех в канале связи нестационарен и с целью сохранения требуемой достоверности приходится использовать избыточность кода или для исправления ошибок (при малых уровнях помех), или для обнаружения ошибок (при больших уровнях помех) Иными словами, предлагаемое устройство может использоваться в адаптивной системе приема информации. Кроме того, появляется возможность снимать информацию с выхода устройства как в параллель ном, так и в последовательном коде, что расширяет возможности его применения. На фиг. 1 представлена блок-схема предлагаемого устройства 1три использовании произвольного декодера; на фиг. 2то же, для частного, но весьма важного и распространенно1 о случая, когда инфор- мация закодирована циклическим (n,k,d кодом, допускающим мажоритарную процедуру декодирования Устройство содержит входы 1, декодер 2, элемент ИЛИ 3, элемент 4 задерж ки, счетчик 5 сдвигов, триггеры 6 и 7, дополнительный элемент И 8, (р + 1) вход 9 декодера, элементы И 10, р выходы 11 устройства, дополнительный элемент И 12, выход 13 обнаружения ошибок, дополнительный элемент И 14, выход 15 информации. Входная информация в параллельном коде (из многоканальной линии связи, из устройства хранения информации или из другого источника), зaкoдиpoвaннaя(п,k,d кодом, поступает в декодер 2 и одновременно в элемент ИЛИ 3, на выходе которого формируется импульс, соответствующий моменту поступления информации в декодер 2, -Этот импульс с первого выхода элемента ИЛИ 3 поступает на вход элемента 4 и на счетный вход счетчика 5, а со второго выхода -на входы установки О триггеров 6 и 7. Нулевое состояние триггера 6 запрещает прохождение сигналов через элементы И 12 и 14. Элемент И 8 в исходном состоянии-от крыт. С выхода элемента 4 импульс поступает черев элемент И 8 вновь на вход элемента ИЛИ 3, а также на (р + l) вход 9 декодера 2. Декодирование принятого кодового слова п юизводится за N тактов (в общем случае N И ). Таким образом, за Ц тактов в декодере 2 производится исправлетше ошибок в принятом кодовом векторе (если эти ошибки имели место). t Каждый тактовый импульс, поступивший в декодер2, одновременно через элемент И 8 и элемент ИЛИ 3 вновь поступает в элемент 4 и тем самым обеспечивается непрерывное поступление тактовых импульсов в декодер 2. После пос- туплет Я N -го тактового импульса счет чик 5 автоматически возвращается в исходное состоя1П1е, при этом с его выхода снимается импульс, который поступает на элементы И 10, .и декодированная информация поступает в параллельном коде па выход 11. Одновременно импульс с выхода Счетчика 5 поступает на триггер . G и переводит его в состояние I. По- теш1иалом с выхода триггера 6 открЫБают ся элементы И 12 и 14. Если в процессе декодирова1шя в декодере 2 имело место хотя бы одно исправление ошибки, то сигнал с выхода исправлений декодера 2 поступает на триггер 7 и переводит его в состояние 1, Таким образом, наличие потенциала на выходе 13 свидетельствует о наличии ошибок в принятой информации. В случае необходимости этот сигнал может быть использован для запрещения использования декодированной информации, для повторного ее запроса и т. д. В течение следующих П -тактов сдвиi a информация из декодера 2 через OTV крытый элемент И 14 поступает в пооледовательном коде на выход 15. Эти импульсы вновь подсчитываются CHeiv чиком 5. Через тактов все импу/п сы из декодера 2 поступают на шлход 15. Этот момент фиксируется счетчиком 5, и потенциал с этого счетчика через 563 открытый элемент и 12 закрывает элемент И 8. Тем самым запрещается прохождение (N П )-го импульса с выхода элемента 4 через элемент И 8 на вход элемента ИЛИ 3, и тактовые импульсы пвекращают поступать на вход 9 декодера 2. Если, например, требуется получение информации на выходе только в параллельном коде, то для этого достаточно совме тить выход п счетчика 5 с выходом. В этом случае схема прекращает работу сразу после N -го такта и поступления информации на выход 11. Таким образом, предлагаемое устройство действительно имеет более Ш1фокие фуш циона/пэные возможности, чем извест ное (обнаружеш1е или исправлетге ошибок любой кратности, выдача информации в параллельном или последовательном коде) и в то же время является более простым поскольку в нем отсутствуют буферные регистры для преобразования параллельного кода Б последовательный и, наоборот, нет схем синхронизации приходящей информации с местными генераторами/ Декодер 2 (мажоритарный) состоит на Л - каскадного регистра 16 сдвига с обратной связью, сумматоров 17, мажоритарного элемента 18 и выходного сумматора 19 по модулю 2 (см. фиг, 2), При этом сумматоры в соответствии со схемой декодера подсоединены к триггерам регистра 16 сдвига, выходы сумматоров подсоединень го входу мажоритарного элемента-18, выход которого соединен с сумматором 19, на второй вход которого поступают символы из регистра 16. На каждом такте сдвига с помощью мажоритарного элемента 18 проверяется один символ кодового слова, находящийся в крайней правой ячейке регистра 16. Если в проверяемом символе содержится ошибка, то с выхода мажоритарного элемента 18 снимается сигнал исправления, который суммируется (по модулю 2) с проверяемым символом на сумматоре 19 и по цепи обратной связи вновь заш1сывается на вход регистра 16. За г7 тактов оказываются проверенными и при необходимости исправлен 1ыми все Y2 символов. Таким образом, в этом частном случа число тактов декодирования N равно числу символов И . Поэтому выход счетчика 5, соответствующий п -му импульсу, соединен с триггером 6 и элемеЕГгом И 12. 9 Счетчик 5 считает до Л , затем автоматически сбрасывается в О, одновременно записывает в триггер 6 и подает сигнал на элементы И 10 для считывания ин {юрмации в параллельном коде. Потенциал с тр1п: гера 6 открывает элементы И 12 и 14, и декодированная информация, через элемент И 14 поступает в последовательном коде на выход. За ,п тактов вся информация считывается на выход, очередной сигнал со счетчика 5 проходит через элемент И 12 на элемент И 8, и поступление импульсов сдвига прекращает, ся. Схема готова к декодированию следук шего кодового слова. Триггер 7 подсоединен своим едишггiibiM входом к вь1ходу мажоритарного элемента 18, поэтому любое исправление переводит триггер 7 в состоять 1, что свидетельствует о наличии ошибки в принятом кодовом слове. Предлагаемое устройство, по сравне1гаю с известным, позволяет существенно повысить достоверность и надежность приема информации. Положительгый эффект от использоваш я предлагаемого устройства существенным образом зависит от значимости и ценностн передаваемой информации. В системах связи использовашге этого устройства приводит как к нию скорости передачи информации при заданной достоверности, так и к уменьшению занятости канала связи. Формула изобретения Асинхронное -стройство для исправления ошибок, содержащее декодер, элементы И, элемент V1ЛИ, элемент задержки, р входов декодера подключены к входам устройства, первые входы элементов И подключены к соответствующим выходам декодера, а выходь соединен с первыми р выходами ycTpovlcTsa, первые р вход элемента ИЛИ подключены к входам устройства, вход элемента задержки подключен к первому выходу элемента ИЛИ, а выход соединен с (р + l) входом декодера, отличающееся тем, что, с целью повышения достоверности работы устройства, оно содержит два триггера, три допольштеяьных элемента И, счетчик сдвигов, вход которого подключен к первому ВЫХОД элемента ИЛИ, а первый выход соединен со вторыми входами элементов И и с единич11ым входом первого триггера, нулевые входы триггеров

подключены ко второму выходу элемента ИЛИ, единичный вход второго триггера подключен к (jp + l) выходу декодера, а выход второго триггера соединен с (р + l) выходом устройства, первые5

входы первого и второго дополнительных элементов И подключены к выходу первого триггера, вторые входы этих элементов подключены соответственно к (р + 2) выходу декодера и второму выходу счет- 1в чика сдвигов, а выходы соединены соотBeTCTBeifflo с (р + 2) выходом устройства и первым входом третьего дополнительного элемента И, второй вход которого подключен к выходу элемента задержки, а выход соединен с ( р + l) входом элемента ИЛИ.

Источники информации, принятые во внимание при экспертизе:

l.Autotiiat«c Cqppection of MuEtiple Onidinatind na Computer Memory.ЗВЙ Эоирпаб o{ Reseapch and DeveBopraentt9b3,№4.

2. Сидоров A. A1. Методь контроля электронных цифровых машин. Советское радио, М., 1966, с. 92-99.

Фиг. 2

| название | год | авторы | номер документа |

|---|---|---|---|

| ДЕКОДЕР С ОБНАРУЖЕНИЕМ И ИСПРАВЛЕНИЕМ ОШИБОК | 2008 |

|

RU2370887C1 |

| Декодер | 1979 |

|

SU860330A1 |

| Кодек несистематического сверточного кода | 1990 |

|

SU1714812A1 |

| Декодер циклического кода с исправлением ошибок и стираний | 1980 |

|

SU1083387A1 |

| Кодек несистематического сверточного кода | 1988 |

|

SU1580567A1 |

| Декодер мажоритарного двоичного кода | 1988 |

|

SU1566488A1 |

| Мажоритарное декодирующее устройство | 1981 |

|

SU1005059A1 |

| АДАПТИВНЫЙ ДЕКОДЕР | 2008 |

|

RU2379833C1 |

| Устройство для декодирования сверточного кода | 1984 |

|

SU1213491A1 |

| Устройство для исправления ошибок | 1981 |

|

SU997254A2 |

Авторы

Даты

1978-11-15—Публикация

1973-12-11—Подача